1 基于SOPC軟硬件協(xié)同設(shè)計(jì)方法

SOPC設(shè)計(jì)技術(shù)實(shí)際上涵蓋了嵌入式系統(tǒng)設(shè)計(jì)技術(shù)的全部內(nèi)容,除了以處理器和實(shí)時(shí)多任務(wù)操作系統(tǒng)RTOS為中心的軟件設(shè)計(jì)、以PCB和信號完整性分析為基礎(chǔ)的高速電路設(shè)計(jì)技術(shù)以外,SOPC還涉及目前已經(jīng)引起普遍關(guān)注的軟硬件協(xié)同技術(shù)。

1.1 軟硬件協(xié)同設(shè)計(jì)模型

目前的軟硬件協(xié)同設(shè)計(jì)是指軟硬件的設(shè)計(jì)同時(shí)進(jìn)行,在系統(tǒng)的初期階段兩者就緊密相連。軟硬件協(xié)同設(shè)計(jì)不僅是一種設(shè)計(jì)技術(shù),同時(shí)也是一種新的設(shè)計(jì)方法和思想,它的核心問題是溝通軟件設(shè)計(jì)和硬件設(shè)計(jì),避免系統(tǒng)中關(guān)系密切的兩部分設(shè)計(jì)過早獨(dú)立。同傳統(tǒng)設(shè)計(jì)方法相比,軟硬件協(xié)同設(shè)計(jì)提高了設(shè)計(jì)抽象的層次,并拓展了設(shè)計(jì)的覆蓋范圍。采用軟硬件協(xié)同設(shè)計(jì)技術(shù)可以使嵌入式系統(tǒng)設(shè)計(jì)更好和更快。

軟硬件協(xié)同設(shè)計(jì)在其研究和生產(chǎn)實(shí)踐過程中,提出了很多的設(shè)計(jì)模型。這些模型都是把系統(tǒng)功能轉(zhuǎn)換成組織結(jié)構(gòu),將抽象的功能描述模型轉(zhuǎn)換成組織結(jié)構(gòu)模型。由于針對一個(gè)系統(tǒng)可以建立多種模型,因此應(yīng)根據(jù)系統(tǒng)的仿真和先前的經(jīng)驗(yàn)來選擇模型。

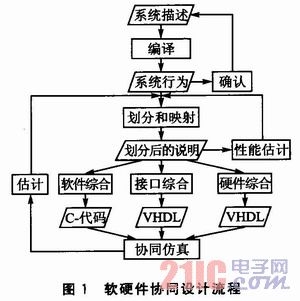

軟硬件協(xié)同設(shè)計(jì)流程從目標(biāo)系統(tǒng)構(gòu)思開始。對一個(gè)給定的目標(biāo)系統(tǒng),經(jīng)過構(gòu)思,完成該系統(tǒng)的規(guī)范描述,然后是模塊的行為描述、對模塊的有效性檢查、軟硬件劃分、性能評估、硬件綜合、軟件編譯、軟硬件集成、軟硬件協(xié)同仿真與驗(yàn)證等各個(gè)階段。其中軟硬件劃分后產(chǎn)生硬件部分、軟件部分和軟硬件接口3個(gè)部分。硬件部分遵循軟件描述、軟件生成和參數(shù)化的步驟,生成軟件模塊,最后把生成的軟硬件模塊和軟硬件接口集成,并進(jìn)行軟硬件協(xié)同仿真,以進(jìn)行系統(tǒng)評估和設(shè)計(jì)驗(yàn)證。圖1給出了一個(gè)軟硬件協(xié)同設(shè)計(jì)流程。

圖中對軟硬件設(shè)計(jì)流程中每個(gè)子過程進(jìn)行了簡單的描述。確定說明文檔之后,先建立高級算法模型,然后再考慮軟硬件的劃分,這樣可以更好地分析算法的實(shí)現(xiàn)方法,比如是用硬件實(shí)現(xiàn)還是用軟件實(shí)現(xiàn)等。

1.2 軟硬件任務(wù)劃分和軟硬件接口

系統(tǒng)模型是對系統(tǒng)初步的粗粒度劃分。依據(jù)這個(gè)粗粒度的劃分,有助于第一次軟硬件任務(wù)分配。在進(jìn)行軟硬件劃分時(shí),需要將系統(tǒng)需求根據(jù)設(shè)計(jì)目標(biāo)和設(shè)計(jì)約束,分解出硬件的功能需求和非功能需求,以及軟件的功能需求和非功能需求,并進(jìn)一步細(xì)化硬件需求及軟件需求。

進(jìn)行軟硬件劃分是協(xié)同設(shè)計(jì)的重心,劃分的合理與否,將直接影響到后續(xù)的設(shè)計(jì)與開發(fā)。設(shè)計(jì)者要從系統(tǒng)的角度,將軟硬件完成的功能作均衡,以想要達(dá)到的目標(biāo)為設(shè)計(jì)標(biāo)準(zhǔn)。在系統(tǒng)的復(fù)雜度一定時(shí),使軟硬件結(jié)合,達(dá)到更高的性能。軟硬件劃分好以后,軟件和硬件的設(shè)計(jì)一直是保持并行的,在設(shè)計(jì)過程中兩者交織在一起,互相支持,互相提供開發(fā)的平臺。

軟硬件的劃分不是簡單地將功能分解,在進(jìn)行軟硬件任務(wù)分配時(shí)已經(jīng)在進(jìn)行系統(tǒng)的架構(gòu)設(shè)計(jì)。其中,非常重要的部分是軟硬件的接口設(shè)計(jì)。嵌入式系統(tǒng)的軟硬件接口,從基本的寄存器到高級的系統(tǒng)接口都非常重要。在軟硬件任務(wù)分配時(shí),主要考慮系統(tǒng)的軟件與硬件之間的接口,以及那些影響最終軟硬件集成、調(diào)試的軟硬件接口。

2 系統(tǒng)硬件設(shè)計(jì)

整個(gè)系統(tǒng)的設(shè)計(jì)可以分為兩個(gè)部分:第一部分是硬件平臺的設(shè)計(jì),即可用以運(yùn)行整個(gè)系統(tǒng)的硬件部分,包含了主芯片、外設(shè)芯片以及它們之間的互聯(lián);第二部分是根據(jù)系統(tǒng)設(shè)計(jì)需求來定制硬件系統(tǒng),即設(shè)計(jì)處理器軟核和相關(guān)外設(shè)的控制邏輯,完成系統(tǒng)的定制。第一部分的工作是后面工作的基礎(chǔ)。

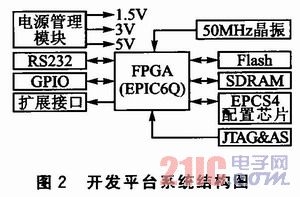

本設(shè)計(jì)中的SOPC開發(fā)平臺系統(tǒng)結(jié)構(gòu)如圖2所示,開發(fā)板的PCB版圖設(shè)計(jì)利用Altium Designer工具完成。軟硬件接口設(shè)計(jì)的主要任務(wù)是基于基本指令集完成驅(qū)動程序的編寫工作。驅(qū)動程序是硬件組件與軟件組件之間的橋梁。軟硬件接口的另一個(gè)重要工作是進(jìn)行硬件初始化。初始化代碼是處理器從復(fù)位狀態(tài)進(jìn)入操作系統(tǒng)能夠運(yùn)行的狀態(tài),也就是在把控制權(quán)交給操作系統(tǒng)或應(yīng)用程序之前硬件和底層軟件(驅(qū)動)必須做的一些工作。

下面詳細(xì)說明平臺中重要的電源電路、Flash接口電路、SDRAM接口電路設(shè)計(jì),其他部分電路可參考相應(yīng)資料。

2.1 FPGA EP1C6Q

目前大部分Altera公司的FPGA均支持NiosIICPU,而Cyclone系列器件是當(dāng)前世界上成本最低的FPGA芯片之一,因此本設(shè)計(jì)中的核心芯片采用Cyclone EP1C6,具有9800個(gè)邏輯單元,92Kb的RAM資源,提供兩個(gè)全功能的鎖相環(huán)(PLL)。I/O接口185個(gè),還支持LVDS、DDR等傳輸接口。它的配置使用最新型的AS配置方式,配置芯片是EPCS4(Flash結(jié)構(gòu),4Mb)。

2.2 電源電路設(shè)計(jì)

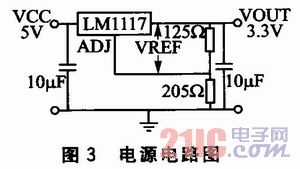

本設(shè)計(jì)采用了可調(diào)三端穩(wěn)壓器LM1117T-ADJ,可以將電壓進(jìn)行線性轉(zhuǎn)換,電流為800 mA,3引腳的T0200封裝。Cyclone系列FPGA上電的最大電流為300mA,該芯片可以滿足要求。LM1117需要在輸出與地之間接入電容以維持內(nèi)部電路的穩(wěn)定,輸入與地之間也需要接入電容對輸入信號進(jìn)行濾波。具體的連接如圖3所示。

2.3 Flash接口電路設(shè)計(jì)

Flash即閃速存儲器,是一種在系統(tǒng)可電擦寫的存儲器。作為一種非易失性存儲器,F(xiàn)lash主要有兩個(gè)功能,一部分用來存儲數(shù)據(jù),另一部分存儲專用程序。

由于不同廠家的Flash的擦寫時(shí)序往往不同,Niosll只支持部分常用的Flash,對于不支持的Flash類型,需要NiosII系統(tǒng)設(shè)計(jì)人員自己完成相關(guān)Flash擦寫子程序的編寫。本平臺采用的AM29LV065 Flash存儲器。采用48腳TSOP封裝,8位數(shù)據(jù)寬度,工作電壓為2.7~3.6V,讀寫操作都較一般Flash省電,僅需要單3 V電壓即可完成在系統(tǒng)編程與擦除操作。

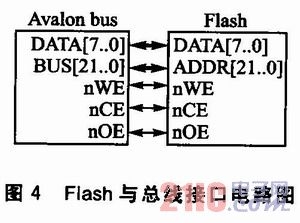

Flash選用的是22×8,即地址總線為22位,數(shù)據(jù)總線為8位,其連接關(guān)系如圖4所示。

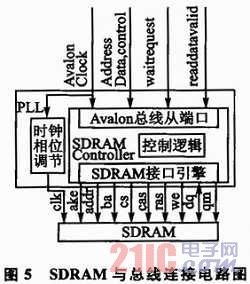

2.4 SDRAM接口電路設(shè)計(jì)

與Flash存儲器不同,SDRAM不具有掉電保護(hù)數(shù)據(jù)的特性,但其操作都是由時(shí)鐘作為同步。可以將其理解為一個(gè)電容,總是傾向于放電,為避免數(shù)據(jù)丟失,必須定時(shí)刷新(充電)。因此,要在系統(tǒng)中使用SDRAM,就要求微處理器具有刷新控制邏輯,或在系統(tǒng)中加入刷新控制邏輯電路。

在NiosII系統(tǒng)中,SDRAM主要用于存放運(yùn)行程序和數(shù)據(jù),并且其運(yùn)行速度比Flash快很多。所以在SOPC系統(tǒng)中,當(dāng)系統(tǒng)啟動后,NiosII CPU首先從復(fù)位地址0x0處讀取啟動代碼,在完成系統(tǒng)的初始化后,程序代碼一般應(yīng)調(diào)入SDRAM中運(yùn)行,以提高系統(tǒng)的運(yùn)行速度。平臺使用的是hynix57V641620HGT,其存儲容量為4Bank×1M×16位(64 Mb)。SDRAM與總線的連接關(guān)系如圖5所示,其刷新頻率是靠FPGA內(nèi)的PLL經(jīng)過相移來提供。

3 SOPC系統(tǒng)結(jié)構(gòu)

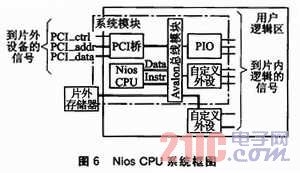

SOPC Builder是一個(gè)能夠生成復(fù)雜硬件系統(tǒng)的工具,將軟硬件的設(shè)計(jì)結(jié)合起來,提供給客戶一個(gè)很好的開發(fā)環(huán)境。利用SOPC Builder可以將Nios CPU和其他應(yīng)用模塊嵌入到FPGA內(nèi)部,實(shí)現(xiàn)一個(gè)可重構(gòu)的嵌入式系統(tǒng),其中Nios CPU是整個(gè)系統(tǒng)的核心。圖6是典型Nios系統(tǒng)的框圖,其中片內(nèi)邏輯是指實(shí)現(xiàn)在FPGA內(nèi)部的電路設(shè)計(jì),系統(tǒng)模塊指的是由SOPC Builder自動生成的設(shè)計(jì)。SOPC Builder會根據(jù)用戶選擇的IP生成相應(yīng)的HDL描述文件(系統(tǒng)模塊文件),這些文件與用戶邏輯區(qū)域內(nèi)的設(shè)計(jì)描述文件一起由QuartusII軟件綜合,然后下載到FPGA內(nèi),這樣就構(gòu)成了系統(tǒng)的硬件基礎(chǔ)。

如圖7所示,采用NiosII單處理器,多個(gè)特定功能專用IP核的系統(tǒng)體系結(jié)構(gòu),軟件部分由處理器進(jìn)行,而硬件部分功能由下載到FPGA上的IP核實(shí)現(xiàn)。硬件之間的通信以及與處理器的通信由Altera公司定義的Avalon片內(nèi)總線實(shí)現(xiàn),而硬件和軟件之間的通信則是通過由IDE根據(jù)硬件系統(tǒng)生成的硬件抽象層HAL來實(shí)現(xiàn)的。

4 總結(jié)

嵌入式技術(shù)發(fā)展之迅速,嵌入式市場前景之廣闊,使嵌入式教學(xué)和研發(fā)成為當(dāng)今熱點(diǎn)。近年來FPGA技術(shù)的飛速發(fā)展,各大FPGA廠商也相繼推出針對SOPC開發(fā)的各種功能強(qiáng)大的開發(fā)套件,這使得FPGA在嵌入式系統(tǒng)設(shè)計(jì)中相對于傳統(tǒng)的ASIC器件具有設(shè)計(jì)靈活、功能強(qiáng)大、一次性投入低、設(shè)計(jì)周期短等優(yōu)勢,在嵌入式系統(tǒng)設(shè)計(jì)中得到越來越廣泛的應(yīng)用。無論是嵌入式教學(xué)實(shí)驗(yàn)還是企業(yè)產(chǎn)品研發(fā),嵌入式系統(tǒng)實(shí)驗(yàn)開發(fā)平臺都具有很高的使用價(jià)值,其開發(fā)具有現(xiàn)實(shí)意義和社會經(jīng)濟(jì)價(jià)值。