關(guān)鍵字:ARM FPGA 聲納波形產(chǎn)生

1、引言

最佳聲納系統(tǒng)的設(shè)計(jì)需要從聲納波形、聲納信道和聲納接收機(jī)三方面進(jìn)行綜合考慮[1]。在聲納信道一定的假設(shè)下,需要設(shè)計(jì)最佳聲納波形和最佳接收機(jī),使聲納系統(tǒng)能在給定的聲納環(huán)境中對(duì)目標(biāo)有最佳的檢測(cè)效果。工作在淺水中的主動(dòng)聲納,其性能主要受限于混響級(jí)。根據(jù)波形選擇與信道匹配的原則,針對(duì)混響信道,所選的聲納波形應(yīng)使其模糊度函數(shù)盡量與混響信道散射函數(shù)不重合,而與聲傳輸信號(hào)散射函數(shù)盡量重合[2]。基于這樣的原則,常用的聲納信號(hào)單頻信號(hào)(CW)、線性調(diào)頻信號(hào)(LFM)抑制混響的能力比較如下:在檢測(cè)靜止或低速目標(biāo)時(shí),LFM和短CW較長(zhǎng)CW有更好的混響抑制能力,但短CW波只適合近距離目標(biāo);在檢測(cè)高速運(yùn)動(dòng)目標(biāo)時(shí),長(zhǎng)CW脈沖是最合適的信號(hào)形式[2]。由此可見,主動(dòng)聲納要完成目標(biāo)捕獲、識(shí)別、跟蹤等不同任務(wù),需要發(fā)射不同的聲納波形。同時(shí)針對(duì)遠(yuǎn)距離、低速和高速運(yùn)動(dòng)等目標(biāo)的不同情況,也需要靈活的選擇聲納波形。正是基于這樣一種需求,本文把具有強(qiáng)大控制能力的微處理器ARM與具有靈活波形產(chǎn)生能力的直接數(shù)字頻率合成技術(shù)(DDS)結(jié)合起來,用FPGA實(shí)現(xiàn)DDS技術(shù),設(shè)計(jì)出了基于ARM和FPGA的聲納波形產(chǎn)生系統(tǒng)。

2、DDS基本原理

隨著微電子技術(shù)的迅速發(fā)展,具有頻率切換時(shí)間短、頻率分辨率高、相位變化連續(xù)、易實(shí)現(xiàn)信號(hào)的多種調(diào)制等諸多優(yōu)點(diǎn)的DDS技術(shù),有了廣闊的應(yīng)用前景。DDS技術(shù)可以理解為數(shù)字信號(hào)處理中信號(hào)綜合的硬件實(shí)現(xiàn)問題,即給定信號(hào)幅度、頻率、相位等參數(shù),產(chǎn)生所需要的信號(hào)波形。

DDS的基本結(jié)構(gòu)包括:相位累加器、相位-幅值轉(zhuǎn)換電路、數(shù)模轉(zhuǎn)換電路及低通濾波器等。相位-幅值轉(zhuǎn)換電路根據(jù)轉(zhuǎn)換方式的不同可分為兩大類[4]:(1)ROM查找表法。ROM中存儲(chǔ)有不同相位對(duì)應(yīng)的幅度值,可根據(jù)相位累加器輸出的相位值尋址ROM,輸出對(duì)應(yīng)的幅值序列。 (2)計(jì)算法。對(duì)相位累加器輸出的相位值,通過數(shù)學(xué)計(jì)算的方法得到對(duì)應(yīng)的幅值。常用的實(shí)時(shí)計(jì)算方法有泰勒級(jí)數(shù)求值法、反函數(shù)求值法、CORDIC算法等。

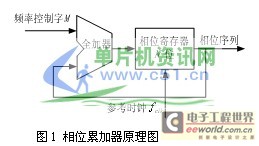

相位累加器是DDS電路中核心的模塊,在工程實(shí)踐上一般用數(shù)字全加器和數(shù)字寄存器的組合來實(shí)現(xiàn),是一個(gè)典型的反饋電路。如圖1所示。

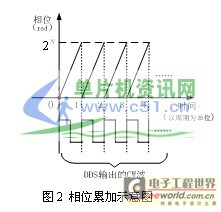

其中, 為頻率控制字, 為相位累加器的位數(shù),fclk為系統(tǒng)參考時(shí)鐘。相位累加器的工作過程為:每來一個(gè)參考時(shí)鐘脈沖,頻率控制字 與相位寄存器輸出的相位數(shù)據(jù)累加一次,累加后的相位一方面反饋到全加器的輸入端,以使全加器在下一時(shí)鐘的作用下繼續(xù)與頻率控制字 相加;另一方面作為采樣地址值送入ROM查找表。如此循環(huán),當(dāng)相位累加器累加滿量后,就會(huì)產(chǎn)生一次溢出,ROM存儲(chǔ)器的地址正好循環(huán)一次,完成一個(gè)周期性的動(dòng)作,這個(gè)周期就是DDS合成信號(hào)的周期,累加器的溢出頻率就是合成信號(hào)的頻率[8]。圖2為相位累加過程示意圖及對(duì)應(yīng)輸出的占空比1:1的CW波。

一般地,DDS輸出信號(hào)頻率![]() 為一個(gè)參考時(shí)鐘周期內(nèi)的相位增量,由此可得:

為一個(gè)參考時(shí)鐘周期內(nèi)的相位增量,由此可得:

由圖2可知,![]() 相當(dāng)與

相當(dāng)與![]() rad,相位累加器溢出一次所歷經(jīng)的采樣脈沖(參考時(shí)鐘)個(gè)數(shù)與DDS輸出一個(gè)周期的信號(hào)所包含的采樣脈沖個(gè)數(shù)是相等的,即:

rad,相位累加器溢出一次所歷經(jīng)的采樣脈沖(參考時(shí)鐘)個(gè)數(shù)與DDS輸出一個(gè)周期的信號(hào)所包含的采樣脈沖個(gè)數(shù)是相等的,即:

將(1)式代入(2),可得:

![]()

由(3)可知,在參考時(shí)鐘一定的情況下,頻率控制字 決定了DDS輸出頻率。 實(shí)際上改變的是信號(hào)的相位增長(zhǎng)速率, 越大,相位累加的曲線越陡峭,溢出一次所需的時(shí)間越短,對(duì)應(yīng)輸出信號(hào)的周期也越小,輸出信號(hào)的頻率就越大;與此相反, 越小,相位累加的曲線越平坦,溢出一次所需的時(shí)間越長(zhǎng),對(duì)應(yīng)輸出信號(hào)的周期也越大,輸出信號(hào)的頻率就越小;當(dāng) 按線性變化時(shí),輸出信號(hào)即為線性調(diào)頻信號(hào),改變 的變化規(guī)律,就可實(shí)現(xiàn)不同規(guī)律的調(diào)頻,如雙曲、指數(shù)、對(duì)數(shù)調(diào)頻等。當(dāng) =1時(shí),DDS輸出最小頻率:

![]()

(4)式也是所謂的頻率分辨率。

3、系統(tǒng)硬件實(shí)現(xiàn)

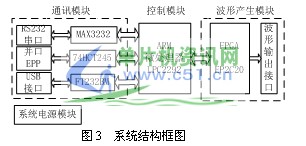

系統(tǒng)硬件設(shè)計(jì)采用模塊化結(jié)構(gòu),由通訊模塊、控制模塊、波形產(chǎn)生模塊和電源模塊四部分構(gòu)成,如圖3所示。

3.1 控制模塊及通訊模塊

ARM作為控制模塊的核心,選用Philips公司的ARM7TDMI系列微處理器LPC2292。控制模塊和通訊模塊實(shí)現(xiàn)了本系統(tǒng)與外部主控設(shè)備(一般為PC機(jī))的通信,通過RS232串口,并口EPP或USB通訊接口,接收主控設(shè)備發(fā)出的聲納波形信號(hào)的幅度、頻率、相位、帶寬等參數(shù)控制字,用以控制波形產(chǎn)生模塊產(chǎn)生相應(yīng)的聲納波形。

3.2 波形產(chǎn)生模塊

DDS技術(shù)的實(shí)現(xiàn)依賴于高速、高性能的數(shù)字器件,一般有兩種方案,一種是使用DDS專用芯片,另一種用可編程邏輯器件FPGA自行設(shè)計(jì)。DDS專用芯片控制方式固定,價(jià)格較高,而FPGA以其速度高、規(guī)模大、可編程,以及有強(qiáng)大EDA軟件支持等特性,十分適合實(shí)現(xiàn)DDS技術(shù)。本系統(tǒng)用FPGA實(shí)現(xiàn)DDS技術(shù)。FPGA選用Altera公司的Cyclone II系列的EP2C20F484C8N。

4、系統(tǒng)軟件開發(fā)

本系統(tǒng)的軟件主要分為主控設(shè)備應(yīng)用程序設(shè)計(jì),F(xiàn)PGA波形設(shè)計(jì)部分和ARM控制部分。

主控設(shè)備應(yīng)用程序是在X86平臺(tái)上,VC環(huán)境下開發(fā)的。主要功能是通過RS232串口,并口EPP或USB任何一種通訊接口,實(shí)現(xiàn)主控設(shè)備與ARM通信。ARM控制部分的程序?qū)崿F(xiàn)對(duì)通訊接口的訪問,并實(shí)現(xiàn)對(duì)FPGA的控制。

FGPA波形設(shè)計(jì)過程采用自頂向下模塊化的結(jié)構(gòu),主要包括時(shí)鐘模塊、寄存器讀寫及控制模塊、DDS模塊,如圖4所示。

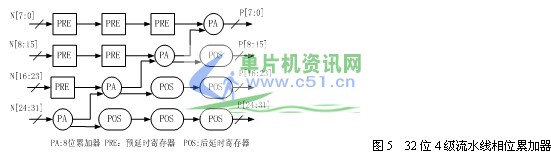

相位累加器是決定DDS性能的一個(gè)關(guān)鍵部分,相位累加器設(shè)計(jì)的好壞將直接影響到整個(gè)系統(tǒng)的性能,因此要從FPGA內(nèi)部結(jié)構(gòu)出發(fā),設(shè)計(jì)出既節(jié)約系統(tǒng)資源,又能大幅度提高系統(tǒng)速度和性能的累加器結(jié)構(gòu)[3]。在設(shè)計(jì)相位累加器的加法器模塊時(shí)不用庫(kù)中提供的lmp_add_sub模塊,而是采用流水線技術(shù),使用Verilog HDL編程實(shí)現(xiàn)。流水線示意圖見圖5。

相幅轉(zhuǎn)換采用ROM查找表法實(shí)現(xiàn)。主要考慮的問題是FPGA內(nèi)部存儲(chǔ)器容量的大小,而EP2C20內(nèi)部有大量的ROM資源可利用,因此可直接調(diào)用lpm_rom模塊來實(shí)現(xiàn)。

關(guān)鍵字:ARM FPGA 聲納波形產(chǎn)生

FPGA模塊化的設(shè)計(jì),為ARM對(duì)其配置提供了極大的方便,ARM可把FPGA視為外掛的一片SRAM,通過外部存儲(chǔ)器接口進(jìn)行控制。

5、軟硬件設(shè)計(jì)需要注意的幾點(diǎn)

在系統(tǒng)軟硬件設(shè)計(jì)中需要注意以下兩點(diǎn):

(1)當(dāng)LPC2292通過外部存儲(chǔ)器接口(EMC)控制FPGA時(shí),地址線的接法如圖6所示,即需要把LPC2292的地址線A0空出來不用。這是由于FPGA實(shí)現(xiàn)的波形產(chǎn)生模塊的數(shù)據(jù)位寬為16位,當(dāng)LPC2292外部存儲(chǔ)器總線配置為16位時(shí),A0地址需要空出來,當(dāng)總線配置為32位時(shí),地址A0,A1都需要空出來,當(dāng)總線配置為8位時(shí),地址從A0開始使用。

(2)EP2C20F484C8N的焊接問題,此型號(hào)為FinleLine BGA封裝,在焊接的時(shí)候要注意芯片的錫球是否含鉛,含鉛與否決定采用何種工藝流程將器件安裝在PCB板上,無鉛封裝要求焊接溫度更高,工藝更復(fù)雜。Altera公司生產(chǎn)的所有無鉛元件以其產(chǎn)品序號(hào)最后的“N”標(biāo)出。因此本系統(tǒng)選用的芯片為無鉛芯片,需要按無鉛工藝焊接,若按有鉛工藝焊接,將造成芯片的虛焊。

6、系統(tǒng)測(cè)試結(jié)果

對(duì)系統(tǒng)軟硬件進(jìn)行的測(cè)試表明,系統(tǒng)達(dá)到了預(yù)期的設(shè)計(jì)指標(biāo),能輸出7路方波信號(hào),頻率固定(CW波)或線性變化(LFM波),且各路信號(hào)可選擇關(guān)斷或選通。CW波的頻率在5~45kHz范圍內(nèi)任意可調(diào);LFM波在5kHz帶寬范圍內(nèi)任意可調(diào),中心頻率在5~45kHz范圍內(nèi)任意可調(diào);輸出脈沖信號(hào)寬度在0.5~100ms間任意可調(diào),相鄰各路信號(hào)的相位可超前和滯后,可選擇發(fā)射功率,且本系統(tǒng)已成功應(yīng)用于某工程項(xiàng)目中,工作正確可靠,得到了工程實(shí)際檢驗(yàn)。圖7為Tektronix邏輯分析儀采集到的對(duì)應(yīng)輸出的CW波。

7、結(jié)論

該系統(tǒng)很好的利用了ARM和FPGA兩者的長(zhǎng)處,ARM集中實(shí)現(xiàn)主控設(shè)備與FPGA通信的橋梁作用,接收主控設(shè)備發(fā)出的聲納波形參數(shù),并根據(jù)這些參數(shù)配置FPGA內(nèi)部的寄存器;FPGA充分體現(xiàn)了它在系統(tǒng)成本、體積上的優(yōu)勢(shì),設(shè)計(jì)靈活、方便,F(xiàn)PGA的使用為系統(tǒng)的升級(jí)帶來了很大方便。同時(shí)通訊接口的多樣性,極大改善了人機(jī)接口,提高了系統(tǒng)的靈活性。