摘要:為了解決高速數(shù)據(jù)采集以及數(shù)據(jù)傳輸問題,設(shè)計了基于USB通信的FPGA高速數(shù)據(jù)采集系統(tǒng)。方案以FPGA為控制核心,實(shí)現(xiàn)A/D控制、數(shù)據(jù)緩存雙口RAM和控制CY7C68013A三個功能。系統(tǒng)采用Verilog HDL語言,通過ISE軟件編程控制多個AD7356同時進(jìn)行數(shù)據(jù)采集,將采集所得數(shù)據(jù)存入雙口RAM,控制CY7C68013A將數(shù)據(jù)通過USB總線上傳到PC機(jī)。系統(tǒng)進(jìn)行實(shí)測實(shí)驗(yàn)表明,在CY7C68013A設(shè)定為16.7Mb/s的傳輸速率下,系統(tǒng)工作正常。

關(guān)鍵詞:USB;FPGA;高速數(shù)據(jù)采集;CY7C68013A;雙口RAM

0 引言

現(xiàn)代安全防衛(wèi)系統(tǒng)中及時發(fā)現(xiàn)和定位入侵行為具有重要的現(xiàn)實(shí)意義。傳統(tǒng)的安全防衛(wèi)系統(tǒng)存在監(jiān)測距離較短、抗電磁干擾能力弱、維護(hù)成本高等缺點(diǎn)。分布式光纖振動傳感器能測量整個光纖長度上隨時間變化的振動信息,具有檢測距離遠(yuǎn)、抗電磁干擾能力強(qiáng)、安裝后易維護(hù)等優(yōu)點(diǎn),已成為長距離管道監(jiān)測和安全防衛(wèi)領(lǐng)域最具有應(yīng)用前景的技術(shù)之一。

本系統(tǒng)中需要對多路信號進(jìn)行高速、高精度采集,然后將數(shù)據(jù)上傳到PC機(jī)中進(jìn)行數(shù)據(jù)處理。所以上位機(jī)(PC機(jī))和下位機(jī)(FPGA)如何高效、快速、方便地數(shù)據(jù)傳輸是本系統(tǒng)中的重要問題。目前常用的傳輸方法為RS 232串口通信方式,通信協(xié)議簡單,在交互數(shù)據(jù)量不大,傳輸速度要求不高的情況下使用非常方便。但是其通常傳輸速率在幾十Kb/s,在高速實(shí)時傳輸系統(tǒng)中無法達(dá)到要求。

本文研究基于USB接口的上、下位機(jī)通信方法,來解決數(shù)據(jù)的實(shí)時交換問題。通用串行總線(UniversalSerial Bus,USB)是計算機(jī)上的一種新型接口技術(shù),它使得計算機(jī)和外部設(shè)備的連接十分方便。USB接口已經(jīng)和串口、并口一樣,成為PC機(jī)的標(biāo)準(zhǔn)接口。目前最新的USB 2.0接口的最高傳輸可以達(dá)到480 Mb/s,遠(yuǎn)高于傳統(tǒng)的串、并口連接速度,可以滿足絕大多數(shù)情況的大數(shù)據(jù)量實(shí)時交換的需求。除此之外,USB接口還支持插拔,極大地方便了系統(tǒng)的開發(fā)調(diào)試和實(shí)際使用。

1 主要器件選擇

本系統(tǒng)為分布式光纖振動傳感器的數(shù)據(jù)采集和傳輸系統(tǒng),需要實(shí)現(xiàn)的主要功能有光電轉(zhuǎn)換、A/D轉(zhuǎn)換和USB通信。系統(tǒng)的總體結(jié)構(gòu)圖如圖1所示,可以看出系統(tǒng)以FPGA為處理核心,包含光電轉(zhuǎn)換、A/D轉(zhuǎn)換和USB通信等外圍功能模塊。

由于光纖微擾動傳感器的傳感采用的是光纖,所以首先需要將信號經(jīng)過光電轉(zhuǎn)換和A/D轉(zhuǎn)換,將信號轉(zhuǎn)換為數(shù)字信號。然后,在FPGA中進(jìn)行數(shù)據(jù)緩存,并對多路信號進(jìn)行排序后通過USB總線將存儲器中數(shù)據(jù)上傳到PC機(jī)中。

1.1 光電轉(zhuǎn)換和A/D轉(zhuǎn)換器件

光電轉(zhuǎn)換部分采用的是PINFET,PIN管反偏高、輸出阻抗與FET的高輸入阻抗得到很好匹配,同時減少了外部干擾和雜散電容,大大降低了熱噪聲,這對低噪聲器件是非常有益的。比起目前較通用的PIN器件來說,PINFET不需要復(fù)雜的后續(xù)電路,而且其模塊化設(shè)計,使輸出噪聲較小,輸出電壓較大,為后續(xù)A/D轉(zhuǎn)換器的采樣電壓提供較好的工作范圍。

A/D轉(zhuǎn)換模塊采用的是12位雙通道差分輸入SAR型AD7356,結(jié)構(gòu)簡單實(shí)用。AD7356為12位雙通道差分輸入SAR型AD。該AD為雙通道型,所以2路信號的轉(zhuǎn)換是同時進(jìn)行,減小了因轉(zhuǎn)換帶來的時間延遲。而且AD7356的采樣頻率由輸入時鐘信號決定,因此可以很方便的改變系統(tǒng)的采樣頻率,滿足系統(tǒng)1~5 MHz的采樣速率要求。另外該AD采用單2.5 V供電,可以與FPGA共用電源,使系統(tǒng)的供電系統(tǒng)簡潔。

1.2 FPGA

作為高速數(shù)據(jù)采集系統(tǒng)數(shù)據(jù)緩存的FPGA,由于系統(tǒng)需要對16路信號進(jìn)行高速實(shí)時緩存,所以FPGA的內(nèi)部存儲空間需要比較大。另外,系統(tǒng)由于下一步需要對于信號做初步處理以減輕PC的運(yùn)算量,提高處理的實(shí)時性,所以采用的是XC4VSX25。XC4VSX25的內(nèi)部塊RAM高達(dá)2 304 KB,分布式RAM高達(dá)160 KB,完全滿足系統(tǒng)需求。而且XC4VSX25中含有128個XtremeDSP Slice,而每個XtremeDSP Slice包含一個18×18位帶補(bǔ)數(shù)功能的有符號乘法器、加法器邏輯和一個48位累加器,每個乘法器或累加器都能獨(dú)立使用。XtremeDSP Slice可以通過IP核的形式方便的調(diào)用,在XC4VSX25中可以方便的將乘法器和累加器進(jìn)行組合,構(gòu)成所需要的數(shù)據(jù)處理結(jié)構(gòu),為下一步信號處理提供了基礎(chǔ)。

1.3 USB器件

USB接口使用方便,連接簡單,但是通信協(xié)議很復(fù)雜。因此,USB外設(shè)必須使用控制器芯片,管理數(shù)據(jù)通信USB控制器采用集成了8051單片機(jī)的CY7C68013A控制器芯片,該芯片遵從USB 2.0規(guī)范,有較快的傳輸速度,是目前比較通用的一種USB控制芯片。

CY7C68013A是Cypress公司EZ-USB FX2LP系列芯片中比較經(jīng)典的一款USB控制器,其內(nèi)部結(jié)構(gòu)如圖2所示。其中,主要包括USB 2.0收發(fā)器、串行引擎(SIE)、增強(qiáng)型8051內(nèi)核、16 KB的RAM、4 KB的FIFO存儲器、I/O接口、數(shù)據(jù)總線、地址總線和通用可編程接口(GPIF)。

EZ-USB FX2LP擁有非常獨(dú)特的結(jié)構(gòu),其串行接口引擎(SIE)負(fù)責(zé)完成串行數(shù)據(jù)的解碼、差錯控制、位填充等與USB有關(guān)的功能。串行接口引擎(SIE)能夠?qū)崿F(xiàn)大部分的功能,從而減輕了嵌入式增強(qiáng)型8051的負(fù)擔(dān),簡化了USB固件程序的開發(fā)。

2 系統(tǒng)軟硬件實(shí)現(xiàn)

2.1 A/D轉(zhuǎn)換

系統(tǒng)通過PINFET光電轉(zhuǎn)換為單端模擬信號,而A/D轉(zhuǎn)換器AD7356是差分輸入方式,所以需要對輸入方式進(jìn)行轉(zhuǎn)換。AD7356說明書中給出了詳細(xì)的轉(zhuǎn)換電路,按說明連接即可。由于AD7356供電電源為2.5 V,所以和FPGA之間的連接需要調(diào)整AD7356的信號電平,使得輸出電平與FPGA的3.3 V電平兼容。在電路設(shè)計時,可以通過將AD7356的Vdriver引腳連接到3.3 V,這樣使得輸出信號電平為3.3 V。

系統(tǒng)采用的AD7356采樣頻率由輸入時鐘信號決定,而采樣通過使能引腳CS控制。在設(shè)定好采樣頻率后,A/D轉(zhuǎn)換程序主要依靠對CS信號控制,并對輸入得兩路信號串并轉(zhuǎn)換即可。

2.2 數(shù)據(jù)緩存

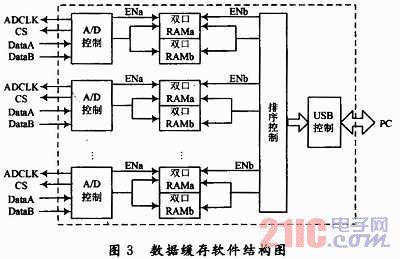

數(shù)據(jù)緩存主要是利用FPGA內(nèi)自帶的塊RAM對多路信號進(jìn)行排序、存儲,然后按USB數(shù)據(jù)包大小打包傳輸,因此對于硬件(FPGA)不再多做介紹。

數(shù)據(jù)緩存的軟件實(shí)現(xiàn)主要依靠FPGA內(nèi)的雙口RAM IP核。雙口RAM由于有2個單獨(dú)的數(shù)據(jù)輸入和輸出口,所以可以調(diào)節(jié)輸入輸出端口的速度,使得數(shù)據(jù)讀取與輸入速度可以方便的控制。另外,由于本系統(tǒng)有多路光信號,所以FPGA內(nèi)還需要對各個雙口RAM的讀取進(jìn)行控制,對各路信號讀取順序進(jìn)行,其軟件結(jié)構(gòu)圖如圖3所示。每路A/D都有兩個RAM輪流存儲采集數(shù)據(jù),一方面避免RAM出現(xiàn)數(shù)據(jù)溢出,保證數(shù)據(jù)不丟失;另一方面可以通過將RAM大小設(shè)定與USB數(shù)據(jù)包大小一致,使USB傳輸?shù)目刂坪唵巍?/p>

2.3 USB通信

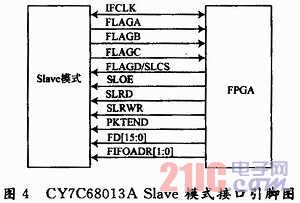

在系統(tǒng)中,USB控制器被配置為SlaVe FIFO模式,CY7C68013A Slave模式接口引腳的連接如圖4所示,這樣FPGA可以將USB控制器當(dāng)成FI-FO來控制,而不用考慮USB標(biāo)準(zhǔn)的各種規(guī)則。而USB控制器則將USB標(biāo)準(zhǔn)的各種規(guī)則通過許多特殊寄存器來設(shè)置,將USB控制簡化。

因此,此部分的軟件實(shí)現(xiàn)包括2個部分。從圖4可以看出,F(xiàn)PGA對各RAM輪流讀取數(shù)據(jù),由于RAM大小與USB數(shù)據(jù)包大小設(shè)定一致,直接把數(shù)據(jù)送入CY7C68013A即可。而FPGA把CY7C68013A當(dāng)成FIFO來控制,所以該部分程序比較簡單。而CY7C68013A內(nèi)程序設(shè)計主要是通過固件程序?qū)鬏斔俣取鬏敺绞健鬏斈J降冗M(jìn)行設(shè)置。

固件程序是指運(yùn)行在設(shè)備CPU中的程序,只有在該程序運(yùn)行時,外設(shè)才能稱之為具有給定功能的外部設(shè)備。系統(tǒng)把固件代碼固化到1片E2PROM中,外設(shè)加電后由FX2通過I2C總線下載到片內(nèi)RAM中自動執(zhí)行。固件架構(gòu)是由Keil C51編譯器與其整合開發(fā)工具所編寫和構(gòu)建。其主要文件包括:fw.c負(fù)責(zé)設(shè)備連接、重枚舉、設(shè)備初始化;periph.c負(fù)責(zé)響應(yīng)各種中斷事件,是主要的用戶函數(shù)應(yīng)用代碼;gpif.c含有GP IF波形描述符表,可以實(shí)現(xiàn)波形的傳輸;dscr.a(chǎn)51文件定義USB設(shè)備握手時需要的各種描述符;fx2.h定義各種二級中斷向量和描述符的數(shù)據(jù)結(jié)構(gòu);fx2 regs.h定義USB單片機(jī)中所有的寄存器。

USB支持4種傳輸類型:控制傳輸、中斷傳輸、等時傳輸、批量傳輸。批量傳輸可以是雙向的,也可以是單向的。它特別適合大數(shù)據(jù)量的傳輸,而且它對傳輸?shù)臏?zhǔn)確性要求較高。因此,通過固件程序設(shè)定本系統(tǒng)采用Slave FIFO模式,批量(BULK)傳輸方式進(jìn)行數(shù)據(jù)傳輸。

3 實(shí)驗(yàn)結(jié)果

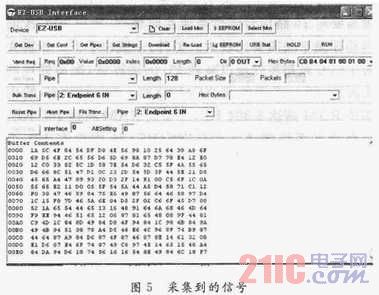

為了方便實(shí)驗(yàn),使用耦合器將一路光信號分為16路相同的信號,這樣所有采集到的信號波形基本相同。實(shí)驗(yàn)時,AD7356設(shè)定為1 MHz采樣速率,USB數(shù)據(jù)包大小為512 Kb,CY7C68013A采用異步SlaveFIFO模式發(fā)送數(shù)據(jù),上位機(jī)采用Cypress公司自帶的EZ-USB Interface軟件采集實(shí)驗(yàn)數(shù)據(jù)。采集到的信號如圖5所示,系統(tǒng)在16.7 Mb/s的傳輸速率下工作正常。

4 結(jié)語

本文采用目前使用最為廣泛的EZ-USB FX2LP芯片,給出了基于USB數(shù)據(jù)采集系統(tǒng)的設(shè)計。該系統(tǒng)充分表現(xiàn)了USB接口傳輸數(shù)據(jù)量大,傳輸速度快的特點(diǎn),非常的適合大批量數(shù)據(jù)實(shí)時的傳輸場合,尤其適合數(shù)據(jù)采集系統(tǒng)和主機(jī)的通信,能夠?qū)崟r的處理采集到的數(shù)據(jù)。這克服了以往數(shù)據(jù)采集速度慢,采集數(shù)量少,接口復(fù)雜等特點(diǎn),實(shí)現(xiàn)了數(shù)據(jù)采集的高速率、多通道。系統(tǒng)進(jìn)行實(shí)測實(shí)驗(yàn)表明,在CY7C68013A設(shè)定為16.7 Mb/s的傳輸速率下,系統(tǒng)工作正常。