美國(guó)國(guó)家標(biāo)準(zhǔn)委員會(huì)于1988年開(kāi)始制定的光纖通道(Fiber Channel,F(xiàn)C)是一種高速串行總線協(xié)議,不僅具有高帶寬、高可靠性、低延時(shí)、傳輸距離遠(yuǎn)、拓?fù)潇`活的優(yōu)點(diǎn),而且支持多種上層傳輸協(xié)議。光纖通道的這一優(yōu)點(diǎn)使得在同一物理接口上運(yùn)行多種上層通道標(biāo)準(zhǔn)和網(wǎng)絡(luò)協(xié)議成為可能。目前已經(jīng)實(shí)現(xiàn)的ML-STD-1553到光纖通道協(xié)議的映射,以及ML-STD-1553遠(yuǎn)程終端器件與光纖通道互聯(lián)方案的系統(tǒng)綜合,為未來(lái)航空電子系統(tǒng)中不同總線的互連提供了一條新的途徑,使得系統(tǒng)在保留傳統(tǒng)網(wǎng)絡(luò)拓?fù)浜蛥f(xié)議的同時(shí),獲得光纖通道所提供的高帶寬服務(wù)。

基于此設(shè)計(jì)思想,本文提出了一種IEEE1394到光纖通道傳輸協(xié)議的映射方案,在此工作基礎(chǔ)上,利用現(xiàn)場(chǎng)可編程邏輯陣列(FPGA),對(duì)所提出的協(xié)議映射方案進(jìn)行了硬件設(shè)計(jì)與實(shí)現(xiàn),設(shè)計(jì)了一個(gè)基于FC的IEEE1394光信號(hào)傳輸系統(tǒng)。

1 IEEE1394到光纖通道的協(xié)議映射

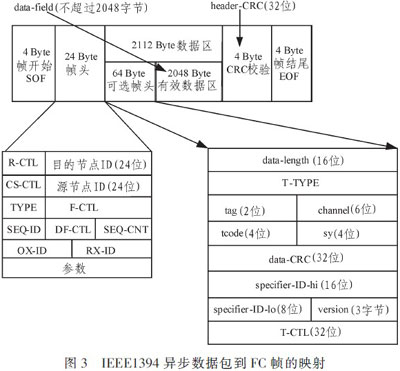

首先簡(jiǎn)要介紹本文提出的一種IEEE1394到光纖通道傳輸協(xié)議的映射方案,更詳細(xì)的說(shuō)明可參考文獻(xiàn)。所提協(xié)議映射方案的基本思想是:在IEEE1394到FC數(shù)據(jù)包的映射過(guò)程中,保留FC原來(lái)的幀格式形式,將FC幀頭部分中源節(jié)點(diǎn)和目的節(jié)點(diǎn)的地址分別映射為IEEE1394源節(jié)點(diǎn)和目的節(jié)點(diǎn)的地址,并將IEEE1394數(shù)據(jù)包中除了數(shù)據(jù)域外的其他信息映射到FC的64Byte可選幀頭上,數(shù)據(jù)域的信息映射到FC的有效數(shù)據(jù)區(qū)。此外,由于FC一個(gè)數(shù)據(jù)幀的有效數(shù)據(jù)區(qū)長(zhǎng)度只有2048Byte,而在通道傳輸速率大于200Mb/s,IEEE1394的等時(shí)數(shù)據(jù)包或傳輸速率大于400Mb/s時(shí),異步數(shù)據(jù)包的最大有效長(zhǎng)度將超出FC有效數(shù)據(jù)區(qū)的大小。因此,當(dāng)IEEE1394數(shù)據(jù)包的長(zhǎng)度超出了FC有效數(shù)據(jù)區(qū)長(zhǎng)度時(shí),應(yīng)該將該數(shù)據(jù)包映射成一個(gè)連續(xù)的FC數(shù)據(jù)幀序列。下面以IEEE1394異步數(shù)據(jù)包到FC數(shù)據(jù)幀的映射為例,說(shuō)明兩種協(xié)議的映射過(guò)程。

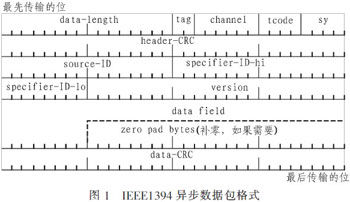

IEEE1394異步數(shù)據(jù)包及FC數(shù)據(jù)幀格式如圖1,圖2所示。圖3為IEEE1394數(shù)據(jù)幀到光纖通道幀格式映射關(guān)系。

對(duì)映射過(guò)程的說(shuō)明:

1)目的節(jié)點(diǎn)和源節(jié)點(diǎn)地址由IEEE1394的16位擴(kuò)充到24位,使網(wǎng)絡(luò)規(guī)模變得比單一的IEEE1394網(wǎng)絡(luò)要大。

2)T-TYPE用來(lái)指明交換消息的傳輸特性,包括交換的傳輸方向和終端-終端(NT-NT)交換的性能定義。在NT-NT類(lèi)型交換中,將為接收NT提供發(fā)送NT的地址,或者為發(fā)送NT提供接收NT的地址。

3)T—CTL用于實(shí)現(xiàn)FC網(wǎng)絡(luò)和IEEE1394網(wǎng)絡(luò)之間的消息傳輸,實(shí)現(xiàn)兩者之間的橋路連接,完成FC網(wǎng)絡(luò)終端或網(wǎng)絡(luò)控制器與IEEE1394節(jié)點(diǎn)之間的消息傳輸。

4)將IEEE1394中的幀頭CRC校驗(yàn)和數(shù)據(jù)CRC校驗(yàn)分開(kāi)。在IEEE1394數(shù)據(jù)傳輸中,首先進(jìn)行的是幀頭CRC校驗(yàn),如果發(fā)現(xiàn)錯(cuò)誤,則立即拋棄該幀。所以這里設(shè)想將IEEE1394數(shù)據(jù)CRC放在光纖通道數(shù)據(jù)幀的可選幀頭,將幀頭CRC放在光纖通道數(shù)據(jù)幀CRC校驗(yàn)中,這樣可以先檢測(cè)幀頭CRC,節(jié)省系統(tǒng)開(kāi)銷(xiāo)。

2 IEEE1394光信號(hào)傳輸系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

2.1 系統(tǒng)的構(gòu)架

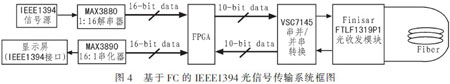

為在光纖通道傳輸IEEE1394信號(hào),構(gòu)建兩種總線互連的硬件平臺(tái),所設(shè)計(jì)的傳輸系統(tǒng)不僅要實(shí)現(xiàn)兩種數(shù)據(jù)幀格式的轉(zhuǎn)換,還要實(shí)現(xiàn)FC-0、FC-1、FC-2協(xié)議層中的部分功能。本文所設(shè)計(jì)的基于FC的IEEE1394光信號(hào)傳輸系統(tǒng)結(jié)構(gòu)如圖4所示,包括IEEE1394信號(hào)源,基于FPGA的1394-FC協(xié)議轉(zhuǎn)換器,必要的外圍接口器件以及光纖收發(fā)模塊,系統(tǒng)傳輸速率1.0625Gb/s。其中,光纖通道FC-0層的功能由光電轉(zhuǎn)換模塊和串并與并串轉(zhuǎn)換芯片實(shí)現(xiàn),而IEEE1394到FC數(shù)據(jù)幀映射及FC-1、FC-2層功能主要基于FPGA進(jìn)行硬件編程來(lái)實(shí)現(xiàn)。

2.2 基于FPGA的功能模塊設(shè)計(jì)與實(shí)現(xiàn)

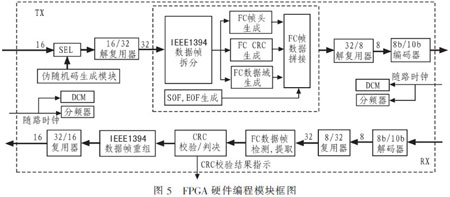

在所設(shè)計(jì)的系統(tǒng)中,F(xiàn)PGA主要實(shí)現(xiàn)IEEE1394到FC的數(shù)據(jù)幀映射以及FC-1、FC-2層功能。基于FPGA的功能模塊結(jié)構(gòu)如圖5所示。

1)FC-1層功能單元包括8b/10b編碼/解碼模塊和D/K類(lèi)型指示模塊。

2)FC-2層功能單元包括數(shù)據(jù)接收模塊,發(fā)送模塊及系統(tǒng)配置模塊。

3)IEEE1394到FC的數(shù)據(jù)幀映射模塊(協(xié)議轉(zhuǎn)換)是FPGA設(shè)計(jì)的核心部分。該部分能夠完成對(duì)信號(hào)源發(fā)出的IEEE1394數(shù)據(jù)幀到FC協(xié)議的數(shù)據(jù)幀的映射工作,即將IEEE1394數(shù)據(jù)幀轉(zhuǎn)換為FC幀格式。同時(shí)能從接收到的FC數(shù)據(jù)幀還原出IEEE1394數(shù)據(jù)幀。

4)FPGA片內(nèi)的發(fā)送(TX)部分和接收(RX)部分均加入了數(shù)字時(shí)鐘管理(DCM)和分頻器模塊,DCM可以使時(shí)鐘信號(hào)通過(guò)時(shí)鐘樹(shù)達(dá)到各個(gè)片內(nèi)寄存器,以減小片內(nèi)時(shí)鐘信號(hào)的抖動(dòng)和延時(shí),提高系統(tǒng)運(yùn)行速率。

此外,為了方便在沒(méi)有外接IEEE1394信號(hào)源的情況下對(duì)FPGA內(nèi)部的功能模塊進(jìn)行調(diào)試,在FPGA的TX前通過(guò)采用線性反饋移位寄存器IP核構(gòu)建了一個(gè)偽隨機(jī)序列發(fā)生器,可以用來(lái)模擬IEEE1394數(shù)據(jù)源,并通過(guò)1個(gè)二選一選擇器實(shí)現(xiàn)外部輸入信號(hào)與內(nèi)部偽隨機(jī)序列的選擇功能。

FPGA內(nèi)部的工作過(guò)程說(shuō)明如下:IEEE1394數(shù)據(jù)從16:32解復(fù)用器輸出之后,進(jìn)入IEEE1394數(shù)據(jù)拆分模塊,產(chǎn)生對(duì)應(yīng)于FC數(shù)據(jù)幀的SOF、DATA、CRC、EOF的數(shù)據(jù)段,生成符合FC幀格式的數(shù)據(jù)。在這之后,32:8復(fù)用模塊將32bit并行輸入的數(shù)據(jù)復(fù)用成8bit并行輸出的數(shù)據(jù)。隨后進(jìn)入8b/10b編碼模塊,完成8b/10b的編碼工作并以10bit位寬,106.25MHz的速率送入VSC7145串并/并串芯片,最后以1.0625Gbs的速率輸出到SFP光收發(fā)模塊,由光收發(fā)模塊將電信號(hào)調(diào)制成光信號(hào)輸出。

在RX接收部分,由光收發(fā)模塊還原成的電信號(hào)通過(guò)VSC7145串并/并串芯片后以10bit的并行數(shù)據(jù)形式輸入到FPGA中,由8b/10b解碼器解碼,輸出8bit并行數(shù)據(jù)(在解碼過(guò)程中,解碼器可以通過(guò)判斷碼流的極性來(lái)判別是否在傳輸過(guò)程中出現(xiàn)誤碼)。8b/10b解碼輸出后的數(shù)據(jù)通過(guò)1個(gè)8:32解復(fù)用模塊解復(fù)用成32bit的并行數(shù)據(jù),并行支路速率為26.5625MHz,隨后32位并行數(shù)據(jù)通過(guò)FC幀檢測(cè)提取模塊,生成標(biāo)識(shí)信號(hào)隨路輸出。在CRC校驗(yàn)/判決模塊中,數(shù)據(jù)通過(guò)CRC位運(yùn)算反映是否出現(xiàn)誤碼,并給出指示。在這之后,F(xiàn)C數(shù)據(jù)幀重組為IEEE1394數(shù)據(jù)幀,最后經(jīng)由32:16復(fù)用模塊將32bit并行IEEE1394幀數(shù)據(jù)重新復(fù)用成16bit并行數(shù)據(jù),與53.12MHz的隨路信號(hào)一同送出FPGA芯片。

3 FPGA功能驗(yàn)證

本設(shè)計(jì)已在Xilinx Spartan3系列的Xc3s200中實(shí)現(xiàn),并在Xilinx ISE 7.1仿真環(huán)境下進(jìn)行了功能和時(shí)序仿真驗(yàn)證。采用偽隨機(jī)序列發(fā)生器生成的偽隨機(jī)代碼模擬IEEE1394數(shù)據(jù)源,設(shè)定每1000Byte為一個(gè)數(shù)據(jù)包包長(zhǎng)。

3.1 功能仿真結(jié)果

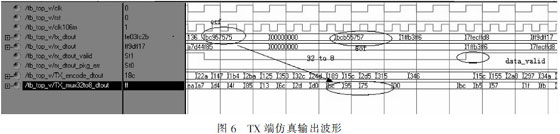

1)在發(fā)送端,IEEE1394數(shù)據(jù)包被拆封,重組成FC數(shù)據(jù)幀,并由8b/10b編碼器編碼后輸出,如圖6中仿真波形tx_dtout,和TX_encode_ dtout所示。

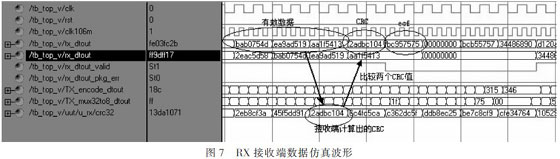

2)在接收端,F(xiàn)C幀結(jié)構(gòu)被正確檢測(cè)并提取,在CRC校驗(yàn)正確后重組成IEEE1394數(shù)據(jù)幀格式輸出,如圖7中仿真波形tx_dtout,crc32及rx_dtout所示。

經(jīng)仿真測(cè)試,F(xiàn)PGA實(shí)現(xiàn)IEEE1394到FC數(shù)據(jù)幀格式的映射功能,各模塊均正常工作,數(shù)據(jù)通信良好,無(wú)丟包現(xiàn)象。

3.2 時(shí)序仿真結(jié)果

該設(shè)計(jì)在Xc3s200上實(shí)現(xiàn)后,F(xiàn)PGA所使用的資源如表1所示,整個(gè)系統(tǒng)資源占用率較低,最高運(yùn)行速率能達(dá)到135.245MHz,滿足106.25MHz的片上最高運(yùn)行速率要求,設(shè)計(jì)達(dá)到了預(yù)期結(jié)果。

4 結(jié)束語(yǔ)

光纖通道具有支持多種上層傳輸協(xié)議的優(yōu)點(diǎn),本文在已有工作的基礎(chǔ)上,利用FPAG,對(duì)所提出的IEEE1394到光纖通道的協(xié)議映射方案進(jìn)行了硬件設(shè)計(jì),通過(guò)FPGA功能仿真及時(shí)序仿真驗(yàn)證了所提方案的可行性。利用此FPGA協(xié)議轉(zhuǎn)換模塊,本文還設(shè)計(jì)了基于FC的IEEE1394光信號(hào)傳輸系統(tǒng),給出了具體的硬件設(shè)計(jì)方案。目前,此系統(tǒng)的主要調(diào)試工作已完成,后續(xù)的工作將通過(guò)系統(tǒng)傳輸實(shí)驗(yàn),對(duì)系統(tǒng)性能進(jìn)行分析研究。