李炳乾,王勇,劉達,譚小虎

(空軍工程大學(xué) 航空航天工程學(xué)院,陜西 西安 710038)

摘要:航電光纖通道接口板是實現(xiàn)航電系統(tǒng)統(tǒng)一網(wǎng)絡(luò)的基礎(chǔ),在高速傳輸過程中,光纖通道接口板需要及時對未處理的幀進行緩存。文章基于DDR2的大容量、高速率存儲模塊為這一問題提出了解決方案。對DDR2的功能及結(jié)構(gòu)進行了簡要闡述,根據(jù)輸入和輸出需求,設(shè)計實現(xiàn)了DDR2芯片組電路,采用FPGA IP核實現(xiàn)DDR2控制器,測試仿真控制器的讀寫時序。測試結(jié)果表明,所設(shè)計的DDR2控制器能夠按照規(guī)則的時序進行操作,實現(xiàn)了高速讀寫,可以實現(xiàn)功能集成并節(jié)約成本,很好地滿足光纖通道接口板的設(shè)計需求。

關(guān)鍵詞:光纖通道;DDR2控制器;FPGA;IP核

中圖分類號:TP27文獻標識碼:ADOI: 10.19358/j.issn.16747720.2016.23.010

引用格式:李炳乾,王勇,劉達,等. 航電FC接口板存儲模塊設(shè)計與硬件電路實現(xiàn)[J].微型機與應(yīng)用,2016,35(23):35-37,41.

0引言

光纖通道(Fibre Channel,FC)總線接口板是綜合模塊化航電系統(tǒng)結(jié)構(gòu)中的重要組成部分,依據(jù)航電系統(tǒng)網(wǎng)絡(luò)中心化設(shè)計要求,光纖通道總線接口板要實現(xiàn)數(shù)據(jù)的接收與發(fā)送[1]。由于數(shù)據(jù)傳輸量巨大,為減輕主機CPU收發(fā)處理負擔(dān),還要具備包括數(shù)據(jù)緩存在內(nèi)的多種功能。數(shù)據(jù)緩存功能就是要構(gòu)建光纖通道接口板數(shù)據(jù)的接收和發(fā)送隊列,緩存未及時處理的數(shù)據(jù)和接口板狀態(tài)信息。

DDR2作為當(dāng)前主流的內(nèi)存芯片,具有存取速度快、儲量大、成本較低等特點[2-3],被廣泛地運用到通用計算機系統(tǒng)、嵌入式系統(tǒng)等電子行業(yè)的各大領(lǐng)域當(dāng)中。根據(jù)課題要求,采用DDR2可以滿足需求,因此,充分利用板上已有硬件資源,包括FPGA、DDR2芯片等,在FPGA中進行DDR2控制器設(shè)計,實現(xiàn)航電光纖通道接口卡上的存儲模塊設(shè)計。

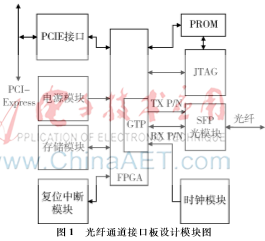

光纖通道接口板的整體功能模塊設(shè)計如圖1所示。

光纖通道接口板傳輸速率為1~2 Gb/s,緩存數(shù)據(jù)讀寫量大,必須采用高速電路設(shè)計,因此時序的嚴格約束十分必要,存儲模塊的合理設(shè)計占據(jù)光纖通道板卡設(shè)計十分關(guān)鍵的地位。

1DDR2性能與結(jié)構(gòu)特點

1.1DDR2性能特點

DDR2(全稱為Double Data Rate 2) 是一種可以在時鐘上升沿和下降沿進行數(shù)據(jù)傳輸?shù)膬?nèi)存技術(shù)標準,由電子設(shè)備工程聯(lián)合委員會(JEDEC)負責(zé)標準的開發(fā)和制定[1]。由于DDR2芯片采用4n-bit 預(yù)抽取架構(gòu)以實現(xiàn)高速操作[4],每個IO引腳被設(shè)計為每個時鐘周期可傳輸2個數(shù)據(jù)字,在不改變內(nèi)核時鐘頻率的情況下實現(xiàn)了數(shù)據(jù)傳輸速率的加倍增長。

1.2DDR2結(jié)構(gòu)特點

光纖通道接口板設(shè)計選用的是2G容量的DDR2芯片MT47H128M16RT[4],其芯片內(nèi)部包括控制邏輯、地址注冊、BANK控制邏輯、存儲陣列、IO接口和時鐘等,存儲陣列設(shè)有8個內(nèi)部Bank,每個Bank大小為16 384×256×64=256 MB,以實現(xiàn)并行讀寫操作。

在芯片外部,雙向數(shù)據(jù)選通引腳DQS和DQS#用于接收端及時獲取數(shù)據(jù),當(dāng)處于READ工作狀態(tài)時信號由DDR2發(fā)送出去,反之由存儲器控制器發(fā)送,本設(shè)計選取的芯片數(shù)據(jù)寬度為16 bit,分為高8位和低8位。此雙向數(shù)據(jù)選通分別由LDQS、LDQS#和UDQS、UDQS#信號進行控制。與此同時,DDR2 SDRAM工作于差分時鐘下,當(dāng)CK上升、CK#下降時,表示時鐘的正邊沿。控制命令(地址A[13:0]/BA[2:0]和控制信號CS#等)在時鐘的正邊沿觸發(fā),數(shù)據(jù)在DQS(同時也是時鐘CK)的雙邊沿觸發(fā)。

2光纖通道接口板存儲模塊硬件設(shè)計

2.1存儲模塊供電設(shè)計

光纖通道接口板采用美光(Micro)公司生產(chǎn)的MT47H128M16RT-25E:C型號84腳FBGA封裝DDR2 SDRAM芯片。DDR2工作電壓采用的SSTL_1.8標準較DDR的SSTL_2.5有較大的優(yōu)勢,能夠很好地減小板上功率消耗和熱量生成。設(shè)計中,將FPGA生成的1.8 V電源引腳接入DDR2電源引腳VDD、VDDQ、VDDL等,為DDR2芯片供電。

與此同時,DDR2芯片還需要直流0.9 V的參考電壓VREF輸入,參考了Xilinx公司ML555 developing kit中的電源電路設(shè)計,利用PTH05050Y芯片對DDR2的0.9 V供電電源進行穩(wěn)壓。由于DDR電路VREF消耗電流很小,因此將1.8 V直流電源電壓經(jīng)串聯(lián)電阻分壓處理,得到0.9 V作為芯片輸入?yún)⒖茧妷篤REF,PTH05050Y輸出電壓為0.9 V經(jīng)過穩(wěn)壓的DDR2參考電壓。

2.2接收/發(fā)送緩存芯片組設(shè)計

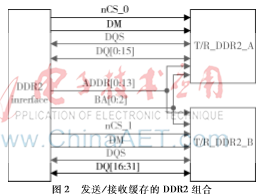

DDR2 SDRAM負責(zé)存儲從FC-1層發(fā)往FC-0層的待發(fā)送幀和從FC-0層發(fā)往協(xié)議層的接收幀,由于光纖傳輸速率快,需要大容量的緩存單元,同時,接收與發(fā)送端口同時對存儲器中某一地址進行操作可能引起未知錯誤,產(chǎn)生不可預(yù)測的后果。因此,利用4片MT47H128M16RT DDR2芯片兩兩組合分別設(shè)置為發(fā)送緩存和接收緩存,如圖2所示為兩片DDR2芯片組成的接收/發(fā)送數(shù)據(jù)緩存模塊。

兩片DDR2構(gòu)成的數(shù)據(jù)緩存需要32條數(shù)據(jù)線,而選用的MT47H128M16RT芯片只有16條數(shù)據(jù)引腳,因此將32位數(shù)據(jù)線分為高位和低位,分別接入兩片DDR2存儲芯片,存儲器控制器通過控制片選CS#、命令輸入RAS#、CAS#和WE#等引腳,實現(xiàn)數(shù)據(jù)的讀寫操作。

利用DDR2所具有的OCD、ODT和POST CAS功能可以很好地對輸出信號品質(zhì)進行控制和調(diào)整,使內(nèi)存單元模塊的設(shè)計更為簡化和精確。通過離線驅(qū)動調(diào)整(OCD)功能設(shè)置上拉/下拉電阻,實現(xiàn)對DQS和DQS#、DQ和DQ#的電壓調(diào)整,使DQ與DQS的電壓相同,減小DQ-DQS傾斜,提高信號完整性和信號品質(zhì)。參考上一節(jié)DDR2芯片內(nèi)部結(jié)構(gòu),DDR2芯片數(shù)據(jù)DQ、數(shù)據(jù)選擇DQS端引腳設(shè)有內(nèi)建核心終結(jié)電阻(ODT),因此在設(shè)計中,將ODT引腳經(jīng)下拉電阻接地,芯片初始化時接低電平,在讀寫數(shù)據(jù)時置高啟動ODT功能,減少主板上電阻的設(shè)置數(shù)量,同時也提高了信號質(zhì)量。

3DDR2控制器設(shè)計

3.1DDR2控制器功能

DDR2 SDRAM是光纖通道接口板的核心組件,硬件的搭建基于DDR2的接口板,更重要的是通過嚴整的時序和規(guī)范的操作控制對DDR2進行初始化、數(shù)據(jù)讀寫等,DDR2控制器就是完成這樣工作的部件[5]。根據(jù)實際使用需要,本文設(shè)計的DDR2控制器主要實現(xiàn)的功能如下:

(1)完成DDR2的初始化操作;

(2)可對DDR2參數(shù)進行配置;

(3)完成突發(fā)長度為4的讀寫操作;

(4)自動發(fā)送激活和預(yù)充電控制命令,減少用戶對底層控制時序的復(fù)雜定義;

(5)自動刷新操作。

3.2基于FPGA的DDR2控制器設(shè)計

DDR2控制器設(shè)計包含4個主要模塊:時鐘生成模塊、存儲控制模塊、數(shù)據(jù)鏈路模塊和用戶接口模塊,如圖3所示。

時鐘生成模塊為控制器提供時鐘信號,輸出多相位時鐘,同時對DQ與DQS間的時延進行校準,使DQS邊沿準確對齊DQ有效窗口的中心位置。

讀寫接口模塊負責(zé)將用戶數(shù)據(jù)DQ和數(shù)據(jù)選擇DQS信號按照規(guī)定時序?qū)懭隓DR2;從DDR2讀取數(shù)據(jù)時,DDR2發(fā)送DQ和DQS信號,F(xiàn)PGA將DQS信號經(jīng)延時校準后作為其寫時鐘,讀取DDR2數(shù)據(jù)。

存儲控制模塊為數(shù)據(jù)讀寫提供地址和命令信號。組成在DDR2上電復(fù)位后進入初始化進程。DDR2經(jīng)過20 μs的穩(wěn)定期,CKE時鐘使能信號置高,400 ns后開始預(yù)充電操作,配置寄存器后再次預(yù)充電和刷新,判斷時鐘是否鎖定后配置離線驅(qū)動電壓,完成初始化。在初始化完成后,可進行數(shù)據(jù)讀寫。刷新操作優(yōu)先級高于讀寫操作,因此兩者沖突時控制器將通知用戶停止發(fā)送讀寫命令,待刷新操作完成后進行讀寫操作。

DDR2讀寫操作采用的是突發(fā)(burst)模式,需要讀寫命令、讀寫數(shù)據(jù)和讀寫地址,在讀寫突發(fā)操作完成時發(fā)送突發(fā)信號完成(burst_done),保持兩個時鐘周期有效后終止讀寫操作。

光纖通道板卡采用Xilinx公司生產(chǎn)的Virtex-5系列XC5VLX85T進行邏輯設(shè)計,在設(shè)計光纖通道協(xié)議邏輯后,F(xiàn)PGA的空置邏輯可以進行DDR2控制器的邏輯設(shè)計,在充分利用FPGA上資源的同時節(jié)約了板上另外焊接專用DDR2控制器芯片的成本和空間。

在Xilinx ISE開發(fā)套件中提供有存儲器接口生成器(Memory Interface Generator,MIG)IP核開發(fā)工具,可以直接根據(jù)用戶需求例化與硬件設(shè)備相適應(yīng)的DDR2存儲控制器設(shè)計模塊[6]。MIG具有GUI界面,根據(jù)需要可以對存儲器件的類型、位寬、速度級別、控制參數(shù)和引腳分配進行準確配置,大大縮短設(shè)計DDR2控制器的時間周期,尤其對系統(tǒng)設(shè)計很有幫助。

在設(shè)計過程中無需再了解DDR2嚴格的物理層時序及工作特性就可以設(shè)計實現(xiàn)DDR2的讀寫功能,用戶操作流程如圖4所示,滿足設(shè)計需求。

上電后,通過初始化配置,得到置高的init_over信號,說明初始化成功;將標識START信號置1,并通過WRITE_BUSY[1]和READ_BUSY[1]信號判斷是否滿足命令發(fā)送條件,當(dāng)兩位均為1時允許命令發(fā)送。若發(fā)送命令條件滿足,則通過用戶接口發(fā)送CMD、操作首地址CMD_ADDR和數(shù)據(jù)操作計數(shù)CMD_CNT,若WRITE_BUSY[0]和READ_BUSY[0]互斥取0值時,用戶接口完成響應(yīng)的寫入或讀取數(shù)據(jù)的操作。

4調(diào)試過程與結(jié)果分析

4.1測試過程

設(shè)計采用內(nèi)部狀態(tài)機實現(xiàn)對FPGA DDR2 IP核控制信號、讀寫數(shù)據(jù)信號、地址信號輸出和輸入的數(shù)據(jù)采集。測試機理為:利用FPGA上DDR2控制器對外部硬件DDR2執(zhí)行一個burst寫操作,然后在同一地址執(zhí)行相同burst的讀操作,讀取剛寫入的數(shù)據(jù),對比寫入數(shù)據(jù)與讀出數(shù)據(jù)是否一致。

DDR2硬件驗證測試流程如下:

(1)系統(tǒng)復(fù)位;

(2)等待用戶接口信號“init_over”為高;

(3)對DDR2進行寫操作;

(4)對DDR2進行讀操作;

(5)對比讀出數(shù)據(jù)與寫入數(shù)據(jù)是否相同,若相同ERROR置0,反之置1。

4.2調(diào)試結(jié)果

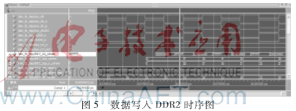

測試程序向DDR2中發(fā)送一個Burst=4的數(shù)據(jù),寫入數(shù)據(jù)的時序如圖5所示。

然后對數(shù)據(jù)進行讀取,讀取數(shù)據(jù)的時序如圖6所示。

在init_over得到高電平后,初始化完成,在相同地址進行數(shù)據(jù)的寫入和讀取,從中可以看到寫入DDR2和讀取到FPGA中的數(shù)據(jù)一致,說明數(shù)據(jù)操作正確。

5結(jié)束語

基于FPGA設(shè)計的DDR2控制器可以很好地滿足時序關(guān)系,經(jīng)過對輸入輸出數(shù)據(jù)的比較表明,數(shù)據(jù)一致,讀寫速度達到了光纖通道接口板的設(shè)計需求。

參考文獻

[1] 支超有,唐長紅.機載數(shù)據(jù)總線技術(shù)及其應(yīng)用[M].北京:國防工業(yè)出版社,2009.

[2] 陳平,張春,張一山,等.DDR2 SDRAM 控制器IP功能測試與FPGA驗證[J].微電子學(xué),2016,46(2):251-254.

[3] JEDEC solid state technology association. JEDEC Standard: DDR2 SDRAM Specification[EB/OL].(2006-07-01)[2016-07-10], http://www.jedec.org/download/search/JESD792C .pdf.

[4] Micron. DDR2 SDRAM MT47H128M16XX Datasheet,2010[EB/OL].[2016-07-01].http://download.micron.com/pdf/datasheet/dram/2g_ddr2.pdf.

[5] Xilinx Inc. Ug086.pdf. 2011[EB/OL].(2006-07-01)[2016-07-10].http://www.xilinx.com/support/documentation/ip_documentation.

[6] 范澤明.DDR2 SDRAM 控制器設(shè)計與驗證[D].西安:西安電子科技大學(xué),2009.