1 ADSP簡介

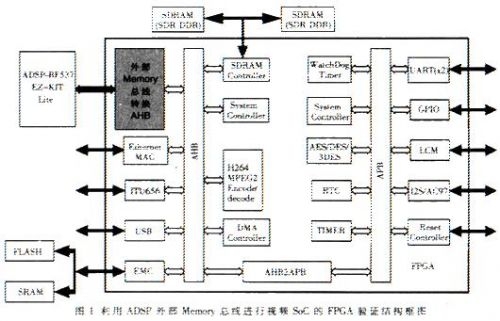

ADSP是ADI(Analog DeviceInc.)公司推出的一系列高性能低功耗DSP芯片,而基于Blackfin處理器的ADSP-BF533一經(jīng)推出便被很多國家的設(shè)計(jì)人員立即采用,后續(xù)系列產(chǎn)品ADSP-BF5xx也被更多的系統(tǒng)設(shè)計(jì)廠家應(yīng)用到各自的產(chǎn)品中。正是因?yàn)锳DSP-BF5xx系列芯片是以功能強(qiáng)大性能卓越的Blackfin處理器為內(nèi)核而推出的高效DSP芯片,使得人們可以采用ADSP-BF5xx系列芯片作為處理器進(jìn)行視頻SoC的FPGA實(shí)時(shí)驗(yàn)證。Blackfin處理器集成了一個(gè)由ADI公司和Intel公司聯(lián)合開發(fā)的基于MSA(MicroSignalArchitecture)的16/32位嵌入式處理器,支持32位RISC指令集,采用10級(jí)流水線,集成了兩個(gè)16位乘法加速器,內(nèi)核主頻最高可以達(dá)到600MHz『1』。

2 ADSP外部Momory總線介紹

ADSP外部Memory總線可以進(jìn)行同步或異步操作,前者是通過時(shí)鐘輸出端CLKOUT進(jìn)行同步的。本文所采用的ADSP-BF537Ez-kitLite開發(fā)套件的外部Memory總線的可用地址僅為19位(ADDR『19:1』),并且采用AMS『3:0』選中相應(yīng)的外部區(qū)域。ADSP-BF537的四個(gè)選通信號(hào)線對(duì)應(yīng)的外部Memory地址范圍如表1所示『2』。可以看出,直接利用ADSP外部Memory總線操作的地址空間只有4MB容量,顯然不能滿足SoC的選址需求,必須進(jìn)行接口總線的轉(zhuǎn)換來提高尋址范圍。

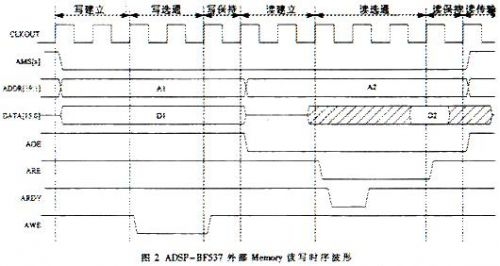

ADSP-BF537外部Memory讀寫時(shí)序波形如圖2所示,其中的ARDY信號(hào)是由外設(shè)產(chǎn)生的。ADSP通過設(shè)置EBIU_AMBCTLx寄存器,允許傳輸過程中使用ARDY握手信號(hào),用來增強(qiáng)系統(tǒng)運(yùn)行的準(zhǔn)確度。ARDY信號(hào)的有效電平是可以設(shè)置的。

EBIU_AMBCTLx寄存器還可以改變ADSP對(duì)外讀寫操作的時(shí)序,包括數(shù)據(jù)建立時(shí)間、讀寫通路時(shí)間以及數(shù)據(jù)保持時(shí)間。例如,圖2所示的寫操作建立時(shí)間、通路時(shí)間和保持時(shí)間分別是2個(gè)周期、2個(gè)周期和1個(gè)周期。如果使能ARDY信號(hào),并設(shè)置為高電平有效,則在設(shè)定的讀寫時(shí)間內(nèi),ARDY為低電平表示外設(shè)不能寫入或者讀出數(shù)據(jù),需要ADSP繼續(xù)保持相應(yīng)的讀寫等待狀態(tài),直到ARDY信號(hào)被拉為高電平;只有當(dāng)ADSP檢測(cè)到ARDY為高電平時(shí),才能將DATA數(shù)據(jù)作為有效數(shù)據(jù)。上述過程如圖2中的讀操作,ARDY信號(hào)被拉低了一個(gè)周期。

ADSP-BF537的外部Memory地址總線位寬是ADDR『19:1』,這樣可以使ADSP靈活地對(duì)16/32位數(shù)據(jù)進(jìn)行地址選址。例如,如果對(duì)連續(xù)地址進(jìn)行16位數(shù)據(jù)的讀寫操作,ADDR『19:1』只需依次加1,而ADSP軟件開發(fā)工具中相應(yīng)的內(nèi)部變量數(shù)據(jù)類型定義為short即可『3』;類似地,如果要讀寫的數(shù)據(jù)類型為int(32位)數(shù)據(jù),則每次訪問外部地址時(shí),ADSP會(huì)連續(xù)產(chǎn)生兩次讀寫操作,并且地址總線ADDR『19:1』是連續(xù)的。

3 AHB總線介紹

AHB(Advanced High-performanceBus)是AMBA總線中用途最為廣泛的一種高速總線,因其協(xié)議簡單、可綜合性強(qiáng)、支持主頻高、功耗低,已經(jīng)被很多SoC芯片作為內(nèi)部高速系統(tǒng)總線。大多數(shù)第三方IP廠商提供的功能模塊的接口都支持AMBA總線協(xié)議。AHB基本傳輸時(shí)序如圖3所示『4』。

4消除信號(hào)的亞穩(wěn)態(tài)現(xiàn)象

在本次視頻SoC的FPGA驗(yàn)證方案中,采用ADSP的外部Memory總線,F(xiàn)PGA既可以利用同步時(shí)鐘輸出CLKOUT進(jìn)行同步設(shè)計(jì),也可以采用異步總線讀寫。如果不使用CLKOUT而采用異步設(shè)計(jì),則在總線轉(zhuǎn)換接口模塊設(shè)計(jì)中,首先需要保證消除讀寫信號(hào)亞穩(wěn)態(tài)現(xiàn)象。ADSP內(nèi)核主頻可以達(dá)到600MHz,外部Memory總線的采樣時(shí)鐘(CLKOUT)動(dòng)態(tài)調(diào)整范圍也很大,因此對(duì)異步輸入信號(hào)可以采用增加同步觸發(fā)器進(jìn)行鎖存延時(shí)的方法來消除亞穩(wěn)態(tài)『5』。具體實(shí)現(xiàn)方法是在異步輸入信號(hào)的前端加2-3級(jí)同步觸發(fā)器。FPGA驗(yàn)證證明:當(dāng)CLKOUT頻率為50MHz,F(xiàn)PGA系統(tǒng)主頻為25MHz時(shí),3級(jí)同步鎖存完全可以消除亞穩(wěn)態(tài),從而保證ADSP在外部Memory總線上正確進(jìn)行數(shù)據(jù)傳輸。

5總線轉(zhuǎn)換狀態(tài)機(jī)設(shè)計(jì)

目前,大多數(shù)采用AMBA總線的SoC系統(tǒng)內(nèi)部的總線位寬是32位,多數(shù)嵌入式CPU和第三方IP核總線位寬也均為32位,因?yàn)?2位地址總線和數(shù)據(jù)總線已經(jīng)可以滿足絕大多數(shù)SoC系統(tǒng)的存儲(chǔ)器映射寄存器的地址分配和數(shù)據(jù)交換以及外部SDRAM和FLASH的尋址需求。ADSP-BF537的外部Memory數(shù)據(jù)總線是16位,并且地址總線只有19位,因此必須通過增加必要的狀態(tài)來解決總線位寬的不匹配問題。

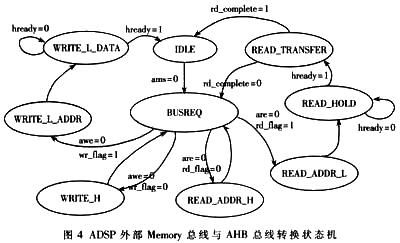

為了實(shí)現(xiàn)ADSP對(duì)外進(jìn)行32位的地址操作和數(shù)據(jù)操作,可以利用Blackfin處理器分兩次進(jìn)行讀寫操作。寫操作分兩次進(jìn)行,第一次寫,先傳輸?shù)刂泛蛿?shù)據(jù)的高16位,第二次寫才將32位的地址和數(shù)據(jù)信號(hào)傳輸?shù)紸HB總線上;進(jìn)行讀操作時(shí),需要AHB產(chǎn)生兩次讀動(dòng)作,這樣才能使有效的32位數(shù)據(jù)被Blackfin處理器正確接收。第一次讀到有效的32位數(shù)據(jù)后傳輸高位,第二次讀到后傳輸?shù)臀唬⑶颐看巫x操作都需要Blackfin發(fā)出兩次讀動(dòng)作,以便組合出AHB的32位地址。這樣就可以突破ADSP-BF537對(duì)外只能進(jìn)行4MB空間存取的限制。以上描述過程的狀態(tài)機(jī)轉(zhuǎn)換圖如圖4所示。

利用ADSP作為SoC系統(tǒng)處理器進(jìn)行SoC驗(yàn)證時(shí),ADSP進(jìn)行的主要操作是讀寫系統(tǒng)內(nèi)部各個(gè)功能模塊的Memory映射控制寄存器,并且通過SDRAM控制器對(duì)SoC系統(tǒng)的外部SDRAM進(jìn)行數(shù)據(jù)交換操作。因此總線轉(zhuǎn)換狀態(tài)機(jī)分成讀傳輸和寫傳輸兩大部分。

當(dāng)ADSP需要進(jìn)行外部Memory總線傳輸時(shí),首先會(huì)把相應(yīng)的ams信號(hào)拉低,這時(shí)總線轉(zhuǎn)換狀態(tài)機(jī)應(yīng)該使AHB進(jìn)入BUSREQ狀態(tài),要求仲裁器釋放AHB總線給CPU(ADSP)。

對(duì)于一個(gè)寫操作,需定義一個(gè)wr_flag標(biāo)志位來確定是否產(chǎn)生AHB寫動(dòng)作。ams信號(hào)拉低后,經(jīng)過可配置的寫建立時(shí)間后,寫控制信號(hào)awe被拉低,初始化的wr_flag為0,表明ADSP進(jìn)行的是第一次寫操作。進(jìn)入的WRITE_H狀態(tài)用來鎖存寫地址和寫數(shù)據(jù)的高16位,同時(shí)會(huì)把wr_flag置為1,但并不向AHB總線發(fā)出寫命令。一個(gè)周期后重新進(jìn)入BUSREQ狀態(tài),等待ADSP下一個(gè)寫命令。ADSP發(fā)出第二次寫命令后,狀態(tài)機(jī)檢測(cè)到awe=0和wr_flag=1后進(jìn)入WRITE_L_ADDR狀態(tài),表明需要向AHB發(fā)出寫命令,包括hwrite、haddr、htrans、hsize等AHB控制信號(hào)。haddr是兩次寫操作地址(16位)組合而成的32位地址,htrans=2和hsize=2,表明是非連續(xù)傳輸,傳輸數(shù)據(jù)位寬是32位。下一個(gè)周期,狀態(tài)進(jìn)入WRITE_L_DATA,兩次寫操作數(shù)據(jù)也相應(yīng)組合成32位。如果AHBslave的hready為高,則32位數(shù)據(jù)釋放到AHB總線上,同時(shí)復(fù)位AHB控制信號(hào),下一個(gè)周期返回IDLE狀態(tài);如果hready為低,則繼續(xù)保持WRITE_L_DATA狀態(tài),直到AHBslave把hready拉高有效。如果等待時(shí)間過長,可以增加一個(gè)計(jì)數(shù)器使?fàn)顟B(tài)機(jī)在一定時(shí)間后自動(dòng)返回IDLE狀態(tài),并標(biāo)記相應(yīng)的error狀態(tài)寄存器。例如,需要通過ADSP向haddr『31:0』=0x1234_5678地址內(nèi)寫入hwdata『31:0』=0xaabb_ccdd,則測(cè)試平臺(tái)(采用vmtslave)模擬ADSP對(duì)外進(jìn)行兩次寫操作,第一次向addr『18:0』=0x1234內(nèi)寫0xaabb,第二次向addr『18:0』=0x5678內(nèi)寫0xccdd,如圖5所示。第二次寫操作后正確產(chǎn)生AHB寫操作。

同樣,對(duì)于一個(gè)讀操作,狀態(tài)機(jī)也需要兩次對(duì)AHB發(fā)出讀動(dòng)作,把讀到的slave數(shù)據(jù)分高低位兩次傳輸給ADSP,不同的是,為了保證AHB讀地址是32位,而不僅僅是ADSP外部Memory地址總線的19位,每次AHB的讀命令,需要ADSP兩次讀動(dòng)作,第一次讀用來傳輸高位地址,第二次讀才能把完整的32位地址傳送到AHB上,使AHB產(chǎn)生讀操作。上述過程的狀態(tài)依次是圖4中的READ_ADDR_H、READ_ADDR_L、READ_HOLD、READ_TRANSFER。標(biāo)志位rd_complete用來區(qū)分AHB的兩次讀動(dòng)作,為0時(shí)在READ_TRANSFER狀態(tài)傳輸讀取數(shù)據(jù)的高16位,被ADSP讀取,下一個(gè)周期后進(jìn)入BUSREQ狀態(tài)等待下一個(gè)讀命令;為1時(shí)在READ_TRANSTER狀態(tài)傳輸讀取數(shù)據(jù)的低16位,并返回IDLE狀態(tài)。例如需要讀取上述已經(jīng)被寫入地址haddr『31:0』=0x1235_5678的值時(shí),第一次ADSP發(fā)出讀addr『18:0』=0x1234,第二次發(fā)出讀addr『18:0』=0x5678,這時(shí)ADSP的data只傳輸高位數(shù)據(jù)0xaabb,ADSP再發(fā)兩次相同的讀命令后,data才傳輸?shù)臀粩?shù)據(jù)0xccdd。對(duì)應(yīng)的讀操作的仿真波形如圖6所

如前所述,ADSP外部Memory總線在對(duì)外讀寫時(shí)可以通過EBIU_AMBCTlx寄存器來選擇是否選通握手信號(hào)ARDY。為了提高傳輸?shù)目煽啃院蜏?zhǔn)確度,在設(shè)計(jì)轉(zhuǎn)換模塊時(shí)需要考慮ARDY,如圖5、圖6中的讀寫操作時(shí)序圖所示,在每一次數(shù)據(jù)傳輸完成的最后一個(gè)狀態(tài),需要將ARDY信號(hào)置1,然后在下一個(gè)IDLE或BUSREQ狀態(tài)將ARDY清0,這樣可以保證ADSP能正確讀到ADSP外部Memory數(shù)據(jù)總線上的有效數(shù)據(jù),防止因ADSP對(duì)外讀寫時(shí)序設(shè)置不合理而造成系統(tǒng)不能正常運(yùn)行。

6 FPGA實(shí)現(xiàn)

本模塊的設(shè)計(jì)是用于FPGA驗(yàn)證用途的,對(duì)于大型視頻SoC系統(tǒng)的FPGA實(shí)時(shí)驗(yàn)證,往往需要采用大容量的FPGA,因此本設(shè)計(jì)采用AlteraStratix IIEP2S60器件進(jìn)行FPGA驗(yàn)證。采用Quartus綜合和布局布線后,一共需要140個(gè)ALUT和131個(gè)寄存器,最快時(shí)鐘可以達(dá)到300MHz。因?yàn)锳DSP可以設(shè)置外部Memory總線的讀寫時(shí)序,所以對(duì)外訪問的速率不是惟一的。為了實(shí)現(xiàn)16位到32位的轉(zhuǎn)換雖然增加了讀寫的次數(shù),但因?yàn)锳DSP外部Memory同步時(shí)鐘頻率調(diào)整范圍很大,因此本設(shè)計(jì)完全可以滿足IP核功能驗(yàn)證對(duì)頻率的要求,對(duì)于視頻SoC內(nèi)部基本AHB總線和APB總線上的功能模塊都能正確實(shí)時(shí)驗(yàn)證。基于ADSP-BF537內(nèi)部嵌入的Blackfin處理器及其DSP接口,已經(jīng)利用本接口模塊成功地驗(yàn)證了AHB總線上的H264和MPEG一2的encode與decode加速器、EthernetMAC控制器、SDRAM控制器以及APB總線上的UART、TIMER、AC97、GPIO和LCD控制器等低速外設(shè)。

隨著驗(yàn)證環(huán)節(jié)在SoC產(chǎn)品開發(fā)過程中所占時(shí)間和開銷的迅速增加,Altera和Xilinx在其大容量FPGA芯片產(chǎn)品中,都集成了特定類型的CPU作為系統(tǒng)處理器,但它們都受到特定FPGA器件的限制『6』。因此利用ADSP內(nèi)嵌的強(qiáng)大Blackfin處理器和豐富的DSP外設(shè),可以有效地提高驗(yàn)證的效率和功能的完整性。本文的總線接口模塊的設(shè)計(jì)對(duì)具有不同讀寫時(shí)序的驗(yàn)證板的正常工作起著重要的作用,SoC原型的搭建必然要求本模塊能真實(shí)反映實(shí)際AHB總線的動(dòng)作,這樣對(duì)于保證各個(gè)功能模塊的完整性和實(shí)時(shí)工作將起很大的作用。