由于DVB-ASI信號(hào)的平均傳輸速率為270 Mbps,而DVB傳輸流又要求保證接收的實(shí)時(shí)性,因此本文選擇了PCI總線。33MHz、32位的PCI總線的數(shù)據(jù)傳輸速率最高可達(dá)133MBps, 完全可以滿足高速實(shí)時(shí)傳輸?shù)男枨蟆_x擇了Altera公司的PCI編譯器軟件包來(lái)實(shí)現(xiàn)PCI接口控制電路。該軟件包為PCI接口提供了一個(gè)完整的解決辦法,包含了PCI控制電路的所有功能。用戶可以通過(guò)修改參數(shù)生成所需的IP核模塊,以設(shè)計(jì)自己的外部設(shè)備接口邏輯。本文選擇了其生成的PCI_MT32功能模塊。

系統(tǒng)硬件模塊設(shè)計(jì)

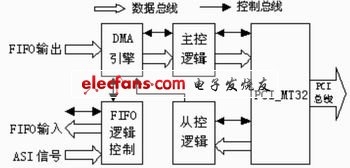

系統(tǒng)的硬件電路設(shè)計(jì)要求:能將傳輸速率為270 Mbps的串行DVB—ASI碼流實(shí)時(shí)、無(wú)損地通過(guò)PCI接口傳輸?shù)絇C,以供PC上的應(yīng)用程序做進(jìn)一步處理。在操作和使用上要方便,在設(shè)計(jì)上要求結(jié)構(gòu)緊湊、接口簡(jiǎn)單、性能可靠、易于升級(jí)。系統(tǒng)硬件框圖如圖1所示。

從圖中可以看出,由于使用了FPGA及PCI IP核,使整個(gè)硬件電路顯得特別簡(jiǎn)潔。它主要由DVB碼流輸入模塊和核心控制模塊組成。串行DVB傳輸流經(jīng)同軸電纜進(jìn)入DVB碼流輸入模塊,轉(zhuǎn)換為8位并行輸出。核心控制模塊對(duì)并行數(shù)據(jù)進(jìn)行緩存,并采用DMA方式傳輸給PCI總線,完成本地總線和PCI總線的可靠通信。

DVB碼流輸入模塊

本文選用ASI接口。ASI信號(hào)由同軸電纜經(jīng)BNC接頭輸入,經(jīng)過(guò)互感(用PE65508芯片)轉(zhuǎn)換為PECL(正向發(fā)射極耦合邏輯)差分電平信號(hào),再經(jīng)過(guò)耦合電路,到達(dá)CY7B933的差分線輸入端。 CY7B933是Cypress公司的一種用于點(diǎn)對(duì)點(diǎn)高速串行數(shù)據(jù)通信的接收芯片,它完成碼流輸入模塊的核心功能。它有三種工作模式,這里選用它的解碼模式對(duì)輸入信號(hào)進(jìn)行8B/10B解碼和串并轉(zhuǎn)換。最后輸出經(jīng)過(guò)字節(jié)對(duì)齊的8位并行TLL信號(hào),輸出的信號(hào)包括 MPEG-2傳輸流和作為同步字使用的逗號(hào)字符(在8B/10B傳輸碼規(guī)則中定義為 K28.5專用字符),其輸出速率恒定為27MBps。

圖1 系統(tǒng)硬件框圖

核心控制模塊

核心控制模塊由FPGA控制電路和異步FIFO組成。主要完成對(duì)輸入ASI信號(hào)的緩存和對(duì)PCI總線信號(hào)的控制的功能。其中最主要的部分是FPGA控制電路。基于整個(gè)系統(tǒng)的性能的考慮,選擇Altera公司的EP1C12。這款芯片有12060個(gè)邏輯單元,52個(gè)RAM塊等資源,完全可以支持本設(shè)計(jì)的要求。

FPGA控制電路內(nèi)部框圖如圖2所示,它是本設(shè)計(jì)的核心部分,對(duì)輸入的ASI信號(hào)保留有效的DVB傳輸流,發(fā)送到FIFO輸入端進(jìn)行緩存。并將FIFO緩存后輸出的數(shù)據(jù)用DMA傳輸方式通過(guò)PCI總線實(shí)現(xiàn)對(duì)PC內(nèi)存的存取,同時(shí)利用FIFO的標(biāo)志信號(hào)控制DMA傳輸過(guò)程。下面對(duì)FPGA控制電路的各模塊進(jìn)行介紹。

PCI_MT32功能模塊

本文在選擇PCI接口芯片時(shí),選擇了Altera公司的PCI 編譯器軟件包,它可以參數(shù)化地生成用于PCI接口的IP核----MegaCore。這個(gè)可編譯和綜合的MegaCore有以下4種宏功能模塊:PCI_MT64、PCI_MT32、PCI_T64和PCI_T32。它們都可以完成總線協(xié)議的轉(zhuǎn)換,將復(fù)雜的、電氣和時(shí)序要求高的PCI總線邏輯轉(zhuǎn)換為易于操作的本地接口邏輯,遵循PCI總線協(xié)議2.2版,經(jīng)過(guò)嚴(yán)格的工業(yè)級(jí)驗(yàn)證并支持多款優(yōu)化FPGA。其中,PCI_MT32是支持33/66MHz工作頻率、32位PCI總線、支持主/從模式的PCI IP功能模塊。考慮到市場(chǎng)的需求,通常的PC主板都支持32位PCI,且在主模式下DMA控制器才能工作,因此選擇了PCI_MT32。本地信號(hào)都以l (local)開(kāi)頭,其中以lt_開(kāi)頭的是從控信號(hào),以lm_開(kāi)頭的是主控信號(hào)。

要使用PCI_MT32功能模塊就要了解其配置寄存器,配置寄存器中的基址寄存器最為重要,PCI_MT32共提供了6個(gè)基址寄存器,可以映射6個(gè)存儲(chǔ)器或I/O 空間。在操作系統(tǒng)啟動(dòng)前后,基址寄存器分別起到兩個(gè)作用。在操作系統(tǒng)啟動(dòng)前,基址寄存器存放定義的空間長(zhǎng)度。以使加電軟件以確定在系統(tǒng)中有多少存儲(chǔ)器以及系統(tǒng)中的 I/O 控制器要求多少地址空間,然后才可以把 I/O 控制器映射到合理的地址空間并引導(dǎo)系統(tǒng)。在操作系統(tǒng)啟動(dòng)后,基址寄存器又要起到存放基地址的作用,通過(guò)對(duì)要存取的基址寄存器用配置寫操作寫入基地址,再通過(guò)基地址加偏移量就可以訪問(wèn)想要存取的空間。

圖2 FPGA控制電路內(nèi)部框圖

主控邏輯模塊

當(dāng)PCI_MT32作為PCI總線主設(shè)備進(jìn)行主模式操作時(shí),主控邏輯模塊對(duì)PCI_MT32本地側(cè)信號(hào)進(jìn)行控制以執(zhí)行PCI主模式寫事務(wù),將FIFO的數(shù)據(jù)傳送給從設(shè)備。同時(shí)還為DMA引擎提供PCI總線所處的狀態(tài),如總線是否處于數(shù)據(jù)階段,是否有從設(shè)備終止等。

模塊的主要設(shè)計(jì)思路:當(dāng)PCI總線仲裁器允許PCI_MT32成為總線主設(shè)備時(shí),PCI_MT32功能模塊在本地側(cè)輸出lm_adr_ackn信號(hào),表明地址階段開(kāi)始,此時(shí)主控邏輯模塊應(yīng)在l_adi線提供PCI地址,并在l_cbeni線提供PCI命令。在接下來(lái)的數(shù)據(jù)階段,如果本地側(cè)數(shù)據(jù)已準(zhǔn)備好,就使lm_rdyn(本地側(cè)主設(shè)備準(zhǔn)備好)信號(hào)有效,并在l_adi線提供數(shù)據(jù),在l_cbeni線提供字節(jié)使能。如果從設(shè)備被選中且準(zhǔn)備好,數(shù)據(jù)傳輸就開(kāi)始了。最后,通過(guò)通知PCI總線當(dāng)前周期是本地側(cè)最后的數(shù)據(jù)階段,在完成這次數(shù)據(jù)傳輸后就進(jìn)入總線空閑狀態(tài),PCI_MT32不再是總線主設(shè)備,一次數(shù)據(jù)傳輸也就結(jié)束了。

從控邏輯模塊

當(dāng)PCI_MT32作為PCI總線從設(shè)備進(jìn)行目標(biāo)事務(wù)操作時(shí),從控邏輯模塊對(duì)PCI_MT32本地側(cè)信號(hào)進(jìn)行控制。PC通過(guò)讀本地側(cè)相應(yīng)寄存器,了解當(dāng)前狀態(tài),通過(guò)對(duì)相應(yīng)DMA寄存器的寫操作,來(lái)啟動(dòng)DMA引擎。由于對(duì)寄存器的讀寫只用到目標(biāo)單周期事務(wù),且大部分信號(hào)由主機(jī)控制,從控邏輯相對(duì)簡(jiǎn)單。主要是保證在要存取的目標(biāo)地址命中,且frame信號(hào)有效時(shí),trdyn(從設(shè)備準(zhǔn)備好)信號(hào)有效。

圖3 DMA狀態(tài)機(jī)流程圖

DMA引擎模塊

DMA引擎模塊由DMA寄存器、DMA狀態(tài)機(jī)等模塊構(gòu)成,當(dāng)PCI_MT32作為PCI總線主設(shè)備進(jìn)行主模式寫操作時(shí),它與主控邏輯模塊共同將FIFO緩存輸出的數(shù)據(jù)通過(guò)DMA操作發(fā)送到PCI_MT32本地信號(hào)側(cè)。其中,DMA寄存器的地址直接映射到PCI的地址空間,其基地址由PCI_MT32中的配置寄存器Bar0決定。主機(jī)通過(guò)訪問(wèn)這些寄存器來(lái)控制DMA操作。寄存器包括控制狀態(tài)寄存器、PCI地址寄存器和中斷狀態(tài)寄存器。DMA狀態(tài)機(jī)模塊流程如圖3所示。

以下對(duì)DMA狀態(tài)機(jī)進(jìn)行簡(jiǎn)要描述:狀態(tài)機(jī)無(wú)數(shù)據(jù)傳輸時(shí)默認(rèn)停留在空閑狀態(tài)。當(dāng)PC寫控制狀態(tài)寄存器中的啟動(dòng)位,就啟動(dòng)狀態(tài)機(jī),進(jìn)入裝載寄存器狀態(tài)。自動(dòng)裝載PCI地址寄存器后進(jìn)入等待請(qǐng)求狀態(tài)。如果FIFO中的數(shù)據(jù)已經(jīng)半滿,進(jìn)入請(qǐng)求狀態(tài)申請(qǐng)占用PCI總線,接著進(jìn)入等待允許狀態(tài),等待PCI設(shè)備獲得總線的控制權(quán)。當(dāng)PCI設(shè)備成為總線主設(shè)備,就進(jìn)入準(zhǔn)備狀態(tài)。判斷PCI總線的地址階段結(jié)束將要進(jìn)入數(shù)據(jù)階段,則進(jìn)入傳輸狀態(tài),進(jìn)行數(shù)據(jù)傳輸。此時(shí),如果從設(shè)備提出終止,則返回寄存器有效狀態(tài),根據(jù)情況重新申請(qǐng)總線的控制權(quán);如果本次DMA數(shù)據(jù)傳輸結(jié)束或出現(xiàn)PCI異常中斷、PCI系統(tǒng)錯(cuò)誤、PCI奇偶校驗(yàn)錯(cuò)誤、FIFO滿等錯(cuò)誤時(shí),則分別進(jìn)入結(jié)束狀態(tài)或錯(cuò)誤狀態(tài),寫中斷狀態(tài)寄存器的相應(yīng)位,同時(shí)發(fā)出中斷信號(hào)。PC收到中斷后,讀中斷狀態(tài)寄存器確定中斷類型,以進(jìn)行下一步操作。最后返回空閑狀態(tài),并清除中斷。

圖4 PCI DMA傳輸仿真波形圖

FIFO邏輯控制模塊

FIFO邏輯控制模塊根據(jù)CY7B933輸出的狀態(tài)信號(hào),刪除同步字K28.5,只將有效的數(shù)據(jù)讀入,并將數(shù)據(jù)送入異步FIFO緩存。當(dāng)FIFO空、半滿、滿時(shí),對(duì)相應(yīng)寄存器進(jìn)行操作或通知DMA引擎模塊,以防止數(shù)據(jù)的溢出或空讀。

異步FIFO在核心控制模塊中,主要起到兩個(gè)作用。一是數(shù)據(jù)緩存,在系統(tǒng)進(jìn)行DMA操作,將數(shù)據(jù)從ASI接口寫入PC內(nèi)存時(shí),DVB-ASI數(shù)據(jù)仍在源源不斷地輸入系統(tǒng),F(xiàn)IFO可以將這些數(shù)據(jù)緩存,以防止數(shù)據(jù)丟失。二是時(shí)鐘隔離作用,輸入的ASI信號(hào)時(shí)鐘是27MHz,而PCI時(shí)鐘達(dá)到33MHz,這就要求對(duì)兩個(gè)頻率不同的時(shí)鐘進(jìn)行同步,異步FIFO的數(shù)據(jù)輸入和輸出分別使用不同的時(shí)鐘,從而實(shí)現(xiàn)時(shí)鐘的隔離和無(wú)縫拼接。由于本設(shè)計(jì)對(duì)FIFO容量的要求較大,因此不采用Megafunction技術(shù)構(gòu)造,而使用專門的高速FIFO芯片。

設(shè)計(jì)結(jié)果

在Quartus-II中進(jìn)行了vhdl源程序仿真。圖4是用DMA方式進(jìn)行PCI傳輸結(jié)果的仿真波形圖。其中ASI_D為模擬輸入的8位ASI碼流,在對(duì)相應(yīng)的DMA寄存器進(jìn)行操作后,啟動(dòng)DMA引擎,圖中①處PCI_MT32通過(guò)拉低reqn信號(hào)發(fā)出總線占用請(qǐng)求信號(hào),②處PCI總線仲裁器通過(guò)拉低gntn信號(hào)允許PCI_MT32成為主設(shè)備。③處進(jìn)入地址階段,PCI_MT32在ad線上提供地址,在cben線上提供總線命令。在接下來(lái)的多個(gè)數(shù)據(jù)階段(圖中④處),PCI_MT32在ad線和cben線上分別提供ASI_D輸入的數(shù)據(jù)和字節(jié)使能,由于輸入ASI信號(hào)是8位,而ad線為32位,因此利用ad信號(hào)的低8位來(lái)傳輸數(shù)據(jù),可見(jiàn),輸出數(shù)據(jù)與ASI_D輸入的數(shù)據(jù)相同。由于DMA傳輸長(zhǎng)度的關(guān)系,本圖最后通過(guò)模擬從設(shè)備斷開(kāi)(圖中⑤處),終止了這次傳輸。由于DMA傳輸沒(méi)有結(jié)束,在終止后,DMA狀態(tài)機(jī)根據(jù)判斷狀態(tài),還會(huì)自動(dòng)繼續(xù)傳輸。從圖中可以看出,framen、irdyn、trdyn、devseln等接口控制信號(hào)完全符合PCI時(shí)序的要求。實(shí)現(xiàn)了將ASI信號(hào)通過(guò)PCI總線與PC進(jìn)行實(shí)時(shí)數(shù)據(jù)傳輸?shù)哪康摹D中32位ad信號(hào)的高位沒(méi)有得到充分利用,如果需要,可以很方便地利用它們將電路升級(jí)為兩路或4路的多路DVB-ASI碼流接收卡。如果使用支持64位PCI總線的PCI_MT64功能模塊,則最多可以實(shí)現(xiàn)8路ASI信號(hào)的接收。

結(jié)語(yǔ)

本系統(tǒng)采用FPGA加PCI IP核的模式實(shí)現(xiàn)對(duì)高速、大容量DVB傳輸流的實(shí)時(shí)傳輸,實(shí)現(xiàn)了系統(tǒng)設(shè)計(jì)的目標(biāo)。選擇PCI總線可以保證在足夠的帶寬下進(jìn)行數(shù)據(jù)傳輸。FPGA的應(yīng)用易于在線升級(jí)電路,擴(kuò)充平臺(tái)的功能。IP核的使用使硬件電路更為簡(jiǎn)潔、可靠。經(jīng)過(guò)驗(yàn)證,本文設(shè)計(jì)的系統(tǒng)可以很好地實(shí)現(xiàn)DVB-ASI信號(hào)的接收功能,同時(shí),也可以作為其它DVB-ASI應(yīng)用的基礎(chǔ)平臺(tái),有著良好的應(yīng)用前景。