0 引言

在雷達射頻接收系統(tǒng)中,,對系統(tǒng)性能指標的要求越來越高,,其中低噪聲放大器是影響著整個接收系統(tǒng)的噪聲指標的重要因素。與普通的放大器相比,,低噪聲放大器作用比較突出,,一方面可以減少系統(tǒng)的雜波干擾,提高系統(tǒng)的靈敏度,;另一方面可以放大系統(tǒng)的射頻信號,,保證系統(tǒng)正常工作。因此,,低噪聲放大器的性能制約著整個接收系統(tǒng)的性能,,對整個接收系統(tǒng)性能的提高起了決定性的作用。因此,,研制寬頻帶,、高性能、更低噪聲的放大器,,已經成為微波技術中發(fā)展的核心之一,。

本文介紹的新型寬帶低噪聲放大器就是在當前工程技術發(fā)展需求的前提下,從放大器本身的特性出發(fā),,采用薄膜混合集成電路和先進的共晶微組裝工藝,,應用平衡式放大電路,精心研制而成的,。

1 電路設計

1.1 電路原理

設計要求整個低噪聲放大器的噪聲系數小于2 dB,,增益在32 dB以上,根據單片放大器目前的增益,,需要設計三級放大鏈路,設計框圖如圖1所示,。

要達到這種要求,,輸入匹配網絡設計時必須按最小噪聲系數匹配。實際上要得到最小噪聲,輸入網絡往往都是失配的,。但是由于指標要求駐波比要小于2,,因此,輸入網絡首先要兼顧端口駐波比,。對于級間匹配一,,既要保證噪聲要低,后級對前級的噪聲貢獻要低,,又要保證較高的增益,,其次還要兼顧兩級放大器管芯間駐波比情況。對于級間匹配二,,則要求保持較高的增益以及合理的增益平坦度,。對于輸出匹配網絡,除了要保證輸出功率外,,還要保證整個帶內的增益平坦度,,以及良好的輸出駐波比。

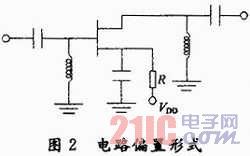

1.2 偏置電路形式

本文采用共源極接法,,自偏置電路形式,,單電源供電,其結構如圖2所示,。此處偏置網絡是一個電阻電源,。其優(yōu)點是能夠提供自動瞬時保護功能,而且,,單電源供電方便,。但是,電阻電源同時也會使噪聲性能惡化,,而且電源的旁路電容會產生低頻振蕩,,因此,在匹配直流電路時,,需要優(yōu)化設計采用合適的偏置電阻,,使噪聲性能惡化最小。

1.3 平衡電橋設計

1.3.1 耦合器設計原理

由于采用了平衡式電路,,所以,,首先需要設計3 dB定向耦合器。在此選用交指線耦合器,。交指線耦合器是一種多導體耦合器,,其優(yōu)點是:體積小,;與雙耦合線器件比較,,它的線間距離較大,,容易實現;與分支線耦合比較,,它帶寬寬,。關于這種3 dB交指線耦合器在目前尚沒有精確的設計方法。一般情況下,,其耦合度按以下的三個設計方程來計算,,電路的作用就是完成這種阻抗轉換的。

根據以上的方程,,只要知道了Zoo和Zoe,,查表便可以求出物理尺寸之比,再經過仿真進行優(yōu)化設計,。

1.3.2 平衡電橋仿真

采用精細陶瓷基片,,其介電常數為εr=9.8。利用ADS軟件進行仿真如圖3所示,,仿真結果如圖4所示,。

1.4 系統(tǒng)仿真設計

1.4.1 穩(wěn)定性設計和寬帶設計

由于采用平衡電路,因此,,輸入,、輸出駐波比可以放在最后整體仿真時考慮。仿真時,,重點考慮穩(wěn)定性,、噪聲系數、增益和增益平坦度,。

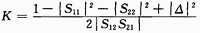

首先,,進行穩(wěn)定性設計。根據絕對穩(wěn)定的充分必要條件:K>1和|△|<1,。

根據其S參數(見表1),,計算可得,在4~8 GHz的帶寬內,,0

再次,需要對放大器進行寬帶內的設計,。從本質上講,,寬帶低噪聲放大器的設計就是要求在一個相對較寬的頻率范圍內,保持放大器的增益不變,。為此,,應適當地設計匹配網絡或者反饋網絡,在保持最佳噪聲系數的情況下補償|S21|隨頻率的變化,。一般來講,,設計寬帶低噪聲放大器有兩種通用技術:補償匹配網絡及運用負反饋電路。在平衡電路中,,噪聲通常是按最佳噪聲來設計的,。但是,由于按最佳噪聲設計往往以犧牲增益為前提,,而如果按最大增益設計,,往往噪聲性能又將惡化。所以,,為了二者兼顧,,折衷考慮。按最佳噪聲設計出的放大器帶寬往往是很窄的,,所以在做寬帶匹配電路時,,輸入、輸出端往往是失配的,。本文的設計思路是:采用補償匹配網絡與負反饋電路相結合的技術,,利用平衡電橋來獲得最佳輸入和輸出VSWR;利用負反饋來補償隨頻率變化的|S21|,,提高系統(tǒng)的穩(wěn)定性,。二者結合最終達到所需要的設計目標。

最后,,將對上述的低噪聲晶體管,,利用ADS進行仿真設計成一個單片,并保證良好的輸入/輸出比,、低的噪聲系數,、高的增益,并把設計好的單片作為放大器的第一級,。在這個前提下,,再進行級聯,,而且,級聯的第二級也需要保證設計的噪聲系數小,。由于總增益在32 dB以上,,根據晶體管的S參數,兩級增益達不到要求,,因此,,需要三級級聯。最后一級,,要有高的增益特性和良好的線性度,。這樣,放大器的增益特性,、噪聲特性,、輸入/輸出特性,功率特性等都可以保證實現,。

1.4.2 整體仿真

采用精細陶瓷基片,,介電常數εr=9.8。選取富士通FHX系列,,利用ADS進行仿真,,電路原理圖如圖5所示。

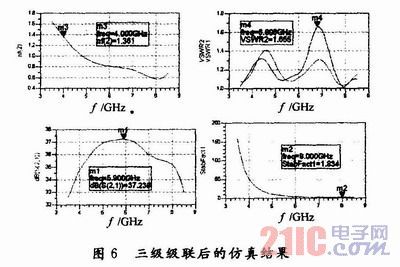

三級級聯后,,仿真結果如圖6所示,。

根據指標要求,整個電路的噪聲小于1.6 dB,,輸入輸出駐波比小于1.7,,增益在35~37.1 dB之間。設計滿足指標要求,。

2 裝配和測試結果

2.1 裝配和調試

各單片加工完成之后,,采用共晶工藝進行焊接,并利用導電膠將芯片粘接在底部基片上,。共晶工藝具有機械強度高,、熱阻小、穩(wěn)定性好,、可靠性高等一系列的優(yōu)點,,是目前國際上比較先進的工藝。導電膠粘接技術工藝性好,、固化容易,、固化物致密、粘接力強。由于其耐熱

性有限,,因此導電膠的固化溫度和固化時間的長短對粘接強度影響較大,。一般采用合適的溫度和時間來固化達到較理想的效果。

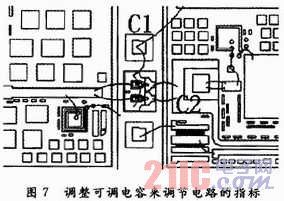

設計完成后,,對帶內平坦度進行調試,。通過在電路中敏感部位改變容性和感性的大小來調節(jié)平坦度,使其滿足指標,,如圖7所示,。

2.2 測試結果

噪聲系數測試結果見表2。

增益和駐波比測試結果如圖8所示,。

1dB壓縮點測試,結果見表3,。

測試結果表明,,實驗值與理論設計值吻合得較好,表明這種設計方法可取,。

3 結論

C波段寬帶低噪聲放大器設計在國內外已有一些研究,,但是該滿足寬帶高性能指標要求的工程設計案例還不多。該設計的寬帶低噪聲放大器的噪聲系數,、增益,、增益平坦度、輸入輸出駐波比以及1 dB壓縮點的功率均達到和超過指標要求,,并且該放大器在整個C波段表現性能優(yōu)良,。因此,在雷達和電子對抗等工程領域可以得到廣泛應用,。另外,,在C波段寬帶低噪聲放大器的小型化和集成化設計上還需進一步探索。