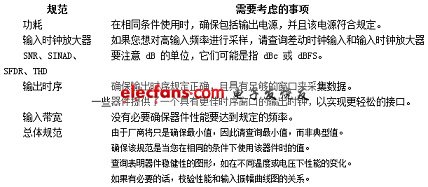

本文的目的就在于突出不同廠商或同一廠商在為不同的高速模數(shù)轉(zhuǎn)換器 (ADC) 撰寫產(chǎn)品說(shuō)明書時(shí)所采用的標(biāo)準(zhǔn)之間的差異。表 1 是選擇正確器件時(shí)可以使用的速查表。

表 1 選擇高速 ADC 的速查表

dB、dBc 與 dBFS 的比較

評(píng)估高速 ADC 產(chǎn)品說(shuō)明書所示性能的一個(gè)主要標(biāo)準(zhǔn)是動(dòng)態(tài)特性或諸如 SNR, SINAD、THD 以及 SFDR 的交流可調(diào)規(guī)范。例如,假設(shè) SINAD(也稱為 SNDR 或 SNRD)為信噪比" title="信噪比">信噪比,即信號(hào)功率與其他頻段功率(失真與噪聲)總和的比值。通常,把這個(gè)比值轉(zhuǎn)換成對(duì)數(shù)值并以 dB 表示。

產(chǎn)品說(shuō)明書間最大的差異在于單位的選擇,特別應(yīng)用于選擇信號(hào)功率的標(biāo)準(zhǔn)。撇開(kāi)導(dǎo)致這種差異的細(xì)節(jié),我們來(lái)看一下信號(hào)功率完全可以用于測(cè)量的信號(hào)功率3,或者可以是類似滿量程的信號(hào)的外推功率。為了避免混淆,TI 將第一種情況下的單位記作 dBc(dB 與載波的比),將第二種情況記作 dB(用于較早的產(chǎn)品說(shuō)明書)或 dBFS(dB 與滿量程的比,用于最新的產(chǎn)品說(shuō)明書)。雖然兩者之間沒(méi)有主次之分,并且下文將說(shuō)明它們之間可以彼此推導(dǎo),但是當(dāng)廠商只以“dB”為單位進(jìn)行說(shuō)明的時(shí)候還是會(huì)產(chǎn)生混淆。在 TI 的兩家競(jìng)爭(zhēng)對(duì)手撰寫的產(chǎn)品說(shuō)明書中,“dB”等于 dBc,而在第三家競(jìng)爭(zhēng)對(duì)手撰寫的產(chǎn)品說(shuō)明書中,“dB”等于 dBFS。

什么因素會(huì)影響最終的比較結(jié)果呢?假設(shè)以-1 dBFS 的輸入振幅測(cè)量來(lái)自不同廠商的兩個(gè)轉(zhuǎn)換器。這就意味著在測(cè)試期間,輸入值是在滿量程以下 1dB 的正弦曲線,換句話說(shuō),振幅 (A) 約為 ADC 滿動(dòng)態(tài)量程的 90%。再假設(shè)兩個(gè)轉(zhuǎn)換器性能相同,因此具有相同的噪聲與失真功率。在第一種情況下(“dB”等于dBc),廠商用輸入功率 (A) 除以噪聲加失真功率 (N+D) 來(lái)計(jì)算信噪比SINAD1。在第二種情況下(“dB”等于 dBFS),廠商推導(dǎo)信號(hào)功率至滿量程,在這種情況下導(dǎo)致最終的數(shù)值增加了 1dB(當(dāng)輸入為 -1dBFS 時(shí))。因此,SINAD2 = SINAD1 + 1。第一家廠商的器件看起來(lái)似乎差了 1dB,但實(shí)際上與第二家廠商的器件是相同的。dBc 的值可以從 dBFS 值求得,只要加上輸入振幅(以 dBFS 為單位):以 dBc 為單位的規(guī)范=以 dBFS 為單位的規(guī)范+以 dBFS 為單位的AIN。

當(dāng)我們比較以 dBc 規(guī)范表示的兩個(gè)轉(zhuǎn)換器時(shí),另一點(diǎn)值得注意的是輸入振幅也會(huì)因器件的不同而不同。很顯然,隨著輸入振幅的減小,信號(hào)值(在 dBc 規(guī)范中)也極可能變得很小(因?yàn)樾盘?hào)功率減小時(shí)一些噪聲底限的組成卻保持不變)。因此,為了使之比較有意義,兩個(gè)輸入振幅必須相等。只要將兩個(gè)輸入振幅的差異添加到由較小的輸入振幅獲得規(guī)范,就可以做出很好的推斷。

顯然由于大多數(shù)轉(zhuǎn)換器的規(guī)定信號(hào)都接近于滿量程,最后信號(hào)水平的差異(取決于所使用的單位)通常不會(huì)大于 2 dB。但是信號(hào)水平的差異不僅可以代表某些應(yīng)用相當(dāng)大的差異,而且還會(huì)影響最終產(chǎn)品設(shè)計(jì)的增益甚至影響整個(gè)設(shè)計(jì)。

最終的問(wèn)題是如何分辨 ADC 產(chǎn)品說(shuō)明書中的 dB 是 dBc 規(guī)范還是 dBFS 規(guī)范。一個(gè)最簡(jiǎn)單的方法是直接詢問(wèn)廠商;如果行不通,設(shè)計(jì)人員可以查看產(chǎn)品說(shuō)明書的典型性能的曲線圖部分。廠商通常都會(huì)針對(duì) dBc 和 dBFS 規(guī)范給出不同的曲線圖,可以根據(jù)曲線圖的數(shù)值與產(chǎn)品說(shuō)明書中規(guī)定的數(shù)值進(jìn)行比較。功耗規(guī)范

功耗是產(chǎn)品說(shuō)明書的另一個(gè)常見(jiàn)的差異點(diǎn)。TI 習(xí)慣上在產(chǎn)品說(shuō)明書的首頁(yè)列出典型工作狀態(tài)下轉(zhuǎn)換器的總功耗。這些狀態(tài)包括在最高采樣速率下的輸入差與低頻或直流的比較,以及在數(shù)字側(cè)每一引腳上施加 10-pF 的負(fù)載。當(dāng)然,TI 也開(kāi)始分離內(nèi)核功耗(模擬,AVDD)與數(shù)字供電損耗(輸出 DVDD)。這主要是因?yàn)槠渌麖S商幾乎都只標(biāo)注了模擬功耗而不包括接口功耗。一些廠商在產(chǎn)品說(shuō)明書里列出了接口功耗,但是用戶必須注意一些測(cè)量條件,例如輸入頻率,每個(gè)引腳的輸出負(fù)載以及輸出電壓,這些都會(huì)顯著的影響測(cè)量值。

此外,還必須特別注意 ADC 可能有的特有模式。并不只是 TI 的產(chǎn)品說(shuō)明書存在這種情況,一些廠商的轉(zhuǎn)換器在模式 A 下進(jìn)行功耗測(cè)量并在產(chǎn)品說(shuō)明書中列出,但是其他動(dòng)態(tài)規(guī)范卻在模式 B 下給出。再例如,對(duì)于那些可承受較寬數(shù)字電源電壓的轉(zhuǎn)換器而言,產(chǎn)品說(shuō)明書在最高 DVDD 電壓下給出時(shí)序規(guī)范,但卻在最低 DVDD 電壓下給出功耗值。

最后,還必須注意轉(zhuǎn)換器對(duì)功率的貢獻(xiàn)。一些轉(zhuǎn)換器可能以丟失內(nèi)部信息為代價(jià)來(lái)節(jié)省功率損耗,例如接受差動(dòng)時(shí)鐘(為了實(shí)現(xiàn)更低的噪聲/抖動(dòng))所需要的參考電壓或時(shí)鐘放大器、諸如 PECL 或 LVDS 的小擺幅時(shí)鐘電平,或者截平濾波時(shí)鐘(正弦曲線)。這個(gè)問(wèn)題將在下文進(jìn)一步闡述。

時(shí)鐘信號(hào)

為了獲得最佳的 ADC 性能4,時(shí)鐘信號(hào)" title="時(shí)鐘信號(hào)">時(shí)鐘信號(hào)是最令人擔(dān)心的問(wèn)題。雖然所有的 ADC 都有一個(gè)時(shí)鐘輸入端,但其中一些要比另一些更容易使用。最關(guān)鍵的問(wèn)題是時(shí)鐘抖動(dòng)、占空比以及必須的時(shí)鐘電平,當(dāng)用高輸入頻率進(jìn)行采樣時(shí),能夠大體上獲得較好的性能參數(shù)。

為了實(shí)現(xiàn)低抖動(dòng),用戶通常使用帶通濾波器過(guò)濾時(shí)鐘信號(hào)來(lái)達(dá)到該目的。這還將產(chǎn)生 50% 的占空比,接近于許多 ADC 的最佳條件。不過(guò),由于該濾波器的插入損耗時(shí)鐘信號(hào)振幅將受到影響,且時(shí)鐘信號(hào)將變成正弦曲線而不是方波。為了接收高質(zhì)量的時(shí)鐘信號(hào),TI 和其他一些廠商在 ADC 的輸入端添加了時(shí)鐘放大器。它的作用是將正弦曲線修正成方波并為內(nèi)部電路的時(shí)鐘循環(huán)提供所需的增益。此外,時(shí)鐘放大器還提供了差動(dòng)接口,能夠減小時(shí)鐘信號(hào)線路中噪聲耦合的影響,從而減小抖動(dòng)。當(dāng)然,這是以增加 ADC 的功耗為代價(jià)的。

然而,一些 ADC 可能還需要 CMOS 電平的方波時(shí)鐘信號(hào)。這類 ADC 的輸入必須是單端口的,而且能夠抑制外部噪聲源與時(shí)鐘路徑耦合。大部分此類 ADC 是為了對(duì)低輸入頻率(50 MHz 以下)進(jìn)行采樣并且能夠獲得很好的性能。醫(yī)學(xué)超聲波就是此類 ADC 的一種典型應(yīng)用。不過(guò),用戶在更高的輸入頻率(例如通訊應(yīng)用中)下為了獲得高信噪比(大于 60s),就需要提供外部元件來(lái)使時(shí)鐘信號(hào)變成方波,并有效地增大功率與電路板面積。即使有了這些外部元件,用戶仍然必須考慮單端接口,而且最終的設(shè)計(jì)很可能不能獲得 ADC 采用內(nèi)部時(shí)鐘放大器時(shí)所能達(dá)到的最優(yōu)性能。

為了提供一致的產(chǎn)品說(shuō)明書,TI 在相同時(shí)鐘條件下的產(chǎn)品說(shuō)明書中使用了相同的圖表與性能參數(shù)。對(duì)于具有差動(dòng)輸入時(shí)鐘信號(hào)的器件而言,通常采用正弦曲線,雖然它并不是 ADC 的最佳條件(由于時(shí)鐘邊緣壓擺率的限制)。為了涵蓋轉(zhuǎn)換器所有可能的應(yīng)用情況,TI 開(kāi)始在產(chǎn)品說(shuō)明書中引入了 3D 等高線圖表(請(qǐng)參見(jiàn)圖 1),這就允許用戶可以得到在給定輸入與采樣頻率" title="采樣頻率">采樣頻率下的典型性能。我們知道,輸入時(shí)鐘信號(hào)的所有條件在試驗(yàn)時(shí)都是保持不變的,除非改變采樣頻率。這意味著如果使用正弦波時(shí)鐘信號(hào),減小采樣頻率將會(huì)使時(shí)鐘邊緣變慢,從而加劇實(shí)際的抖動(dòng)。這是每個(gè) ADC 普遍存在的現(xiàn)象,4但是 TI 設(shè)計(jì)的 ADC 能夠盡可能地將抖動(dòng)最小化。雖然這是最壞的情況,而且減小抖動(dòng)的技術(shù)有很多種,但是在實(shí)驗(yàn)中改變時(shí)鐘條件是不公平的;同樣的,如果保持時(shí)鐘條件不變,那么信噪比 SNR 將隨著抖動(dòng)的增加而降低。用戶必須要知道,如果沒(méi)有時(shí)鐘放大器,性能的降低可能更多。此外,用戶還必須要清楚如果能夠提供一個(gè)抖動(dòng)很小的方波時(shí)鐘信號(hào),那么 ADC 的性能就會(huì)有很大的提高。

圖 1 SNR 與輸入和采樣頻率5的曲線關(guān)系

輸出時(shí)序

為了捕捉傳輸?shù)?FPGA、ASIC、DDC 或其他跟隨 ADC 的邏輯器件的輸出數(shù)據(jù),用戶必須要知道輸出數(shù)據(jù)的窗口是穩(wěn)定的。不過(guò),重點(diǎn)是大多數(shù)廠商均致力于提供一致且完善的產(chǎn)品說(shuō)明書限制。這是因?yàn)橛糜谏a(chǎn)的最終測(cè)試結(jié)果受一些因素的影響,例如自動(dòng)測(cè)試設(shè)備的精度、不能直接訪問(wèn)輸出端(數(shù)據(jù)正在緩沖中)、很難像產(chǎn)品說(shuō)明書一樣設(shè)置相同的條件(例如數(shù)字負(fù)載)等等。為了克服這些局限性,TI 通過(guò)設(shè)計(jì)與特征化(即用統(tǒng)計(jì)方法來(lái)設(shè)置這些參數(shù)),當(dāng)生產(chǎn)中不對(duì)設(shè)備進(jìn)行測(cè)試時(shí),這能促使我們?cè)O(shè)置更寬的防護(hù)頻帶。而如果將相同的限制條件用于其他廠商的話,經(jīng)常會(huì)導(dǎo)致不完善或不精確的產(chǎn)品說(shuō)明書。

設(shè)計(jì)人員應(yīng)對(duì)沒(méi)有任何質(zhì)保書的器件、有質(zhì)保書但是條件不切實(shí)際的器件(例如 0-pF 負(fù)載)、沒(méi)有明確用于捕獲數(shù)據(jù)所需的參數(shù)的器件(例如,給出了建立時(shí)間但沒(méi)有給出保持時(shí)間)、沒(méi)有說(shuō)明規(guī)范所使用的 VOH 和 VOL電平的器件(例如,給出從 50% 到 50% 的信息,但是要推導(dǎo)出 VIH/VIL 邏輯電平卻很麻煩)、或者沒(méi)有說(shuō)明對(duì)整個(gè)工作溫度范圍內(nèi)詳細(xì)參數(shù)的器件進(jìn)行明確的詢問(wèn)。

此外,為了改進(jìn)數(shù)據(jù)捕獲窗口,TI 與其他廠商均提供了一款輸出時(shí)鐘,與輸入時(shí)鐘相比該時(shí)鐘能夠更好地跟蹤輸出數(shù)據(jù)。使用輸出時(shí)鐘可以減小應(yīng)用中的時(shí)序局限。

最后,請(qǐng)注意,建立與保持時(shí)間的定義和門電路" title="門電路">門電路建立與保持時(shí)間的對(duì)應(yīng)部分相同。在門電路中,建立時(shí)間表示數(shù)據(jù)在門電路輸入端準(zhǔn)備好的時(shí)間比時(shí)鐘邊緣閉鎖它的時(shí)間提前了多少。時(shí)間提前得越多,使用該閉鎖門電路就越困難。在 ADC 中,建立時(shí)間表示數(shù)據(jù)穩(wěn)定時(shí)間比輸入或輸出 ADC時(shí)鐘邊緣提前了多少。建立時(shí)間越長(zhǎng),捕獲數(shù)據(jù)就越容易。這些規(guī)則在保持時(shí)間上也同樣適用。

過(guò)程增益

與 SNR 的兩個(gè)參數(shù)相比較,用戶必須考慮到 ADC 的采樣速率。信噪比可通過(guò)對(duì)收斂于奈奎斯特曲線的總體噪聲底限進(jìn)行積分得到。當(dāng)然,用戶的信號(hào)只會(huì)占據(jù)一些帶寬;只有在這個(gè)帶寬上的噪聲才會(huì)影響到信號(hào),而其他噪聲可由數(shù)字濾波器濾除。對(duì)于相同的 SNR 而言,采樣速率高的 ADC 噪聲底限比較低。例如,一個(gè) 200kHz 帶寬,信噪比為 90-dBFS 的 ?∑ 型 ADC 的性能在理論上比產(chǎn)品說(shuō)明書中規(guī)定的信噪比為 75-dBFS、100 MSPS 的 14 位 ADC——ADS5424 要好。當(dāng)然,如果在使用 ADS5424 對(duì) 200-kHz 帶寬進(jìn)行采樣之后(明顯超過(guò) 100 MSPS 的采樣率),我們采用數(shù)字濾波來(lái)濾除帶寬外的噪聲(從 200 kHz 直到 50 MHz),ADS5424 的等效信噪比在這一帶寬上為:

SNR200 kHz = 75 + 10×log10(50×106/200×103) = 99 dBFS >> 90 dBFS。

ADS5424 的信噪比將明顯優(yōu)于 ?∑ 型 ADC(為了示例,假設(shè)噪聲在奈奎斯特曲線上均勻分布,也就是說(shuō)沒(méi)有明顯的閃爍噪聲影響)。前述方程式的第二項(xiàng)稱為過(guò)程增益。隨著過(guò)采樣比的增加,用戶在相同信噪比每增加采樣率一倍,噪聲底限就會(huì)降低 3 dB。換言之,相關(guān)頻帶上的等效精度將增加 0.5 比特。

數(shù)據(jù)適用的條件與最小值

如果沒(méi)有明確的條件,那么規(guī)范將是沒(méi)有意義的。在廣告業(yè)、市場(chǎng)營(yíng)銷材料以及選擇參數(shù)表中這一點(diǎn)尤其重要,條件能夠簡(jiǎn)化產(chǎn)品說(shuō)明書顯示的信息,但在某些情況下,并沒(méi)有提到測(cè)量條件。

同時(shí),典型值通常代表了分布的平均值。不過(guò),用戶應(yīng)注意看一下最小值,特別是當(dāng)器件在某一特定范圍內(nèi)工作(例如多變的溫度環(huán)境)時(shí)。在典型與最小參數(shù)之間的大范圍變化會(huì)出現(xiàn)一些問(wèn)題。變化是否由最終測(cè)試結(jié)果的局限性引起?如果是,則該器件可能適用,但是這樣做的風(fēng)險(xiǎn)是只能保證最小值。最差的情況是器件本身所導(dǎo)致的局限性,工藝的變化(不同器件之間)可以導(dǎo)致設(shè)計(jì)的不耐用性。為了使器件具有較好的穩(wěn)健性并屏蔽此類問(wèn)題的一個(gè)不錯(cuò)的做法是查看產(chǎn)品說(shuō)明書中的典型性能變化與電源電壓或溫度的關(guān)系曲線圖,如圖 2 中的示例所示。

圖 2 ADS5424 SFDR 與模擬電源和溫度范圍的關(guān)系曲線6

與功率參數(shù)一樣,在相同的產(chǎn)品說(shuō)明書中查找不同的參數(shù)(例如 SNR 和 SFDR)時(shí),必須確保它們是在相同條件下給出的參數(shù)。例如,某些器件的 SFDR 模式以犧牲 SNR 為代價(jià)來(lái)改善 SFDR;或者它們有不同的輸入范圍,這會(huì)影響到 SFDR(在較小輸入范圍內(nèi)較好)和 SNR(在較大輸入范圍內(nèi)較好)。

最后,需注意的是,大多數(shù)規(guī)范在是在接近滿量程范圍內(nèi)給出的。然而,SFDR(在 dBFS 規(guī)范中)在輸入振幅減小時(shí)可能變好也可能變得更糟糕。廠商在最終測(cè)試中不能屏蔽很多條件,因?yàn)槟菢訒?huì)增加測(cè)試時(shí)間和測(cè)試成本;但他們通常會(huì)給出說(shuō)明各種條件影響的典型圖表。

輸入帶寬

通常,輸入帶寬代表了 ADC 響應(yīng)平坦度與輸入頻率的關(guān)系。其并沒(méi)有表明該器件在這些輸入頻率下能夠保持應(yīng)有的性能。用戶必須從圖表中核實(shí)相關(guān)性能;如果圖表中沒(méi)有,用戶必須從廠商那里尋求支持或者對(duì)器件本身進(jìn)行評(píng)估。

結(jié)論

本文詳細(xì)說(shuō)明了廠商用于編寫高速 ADC 產(chǎn)品說(shuō)明書的規(guī)范之間的主要差異,提早考慮這些差異有助于設(shè)計(jì)人員避免在設(shè)計(jì)過(guò)程中出現(xiàn)突發(fā)問(wèn)題。