0 前言

計算機網(wǎng)絡(luò)協(xié)議一致性測試是檢驗計算機網(wǎng)絡(luò)各部分正確互連,、互通和互操作的關(guān)鍵技術(shù),,用來驗證產(chǎn)品協(xié)議實現(xiàn)與相應(yīng)協(xié)議標(biāo)準(zhǔn)之間的一致性。即在同一網(wǎng)絡(luò)協(xié)議標(biāo)準(zhǔn)下檢驗不同的待測設(shè)備是否在相同的外部輸入下,,輸出相同的結(jié)果,。

目前,,我國網(wǎng)絡(luò)產(chǎn)品檢測的技術(shù)水平和能力與國際上存在較大差距,協(xié)議一致性測試產(chǎn)品的設(shè)計大多停留在測試方法的理論研究上,,在協(xié)議測試的通用平臺方面還缺乏較好的解決方案,。

1 網(wǎng)絡(luò)協(xié)議一致性測試概述

網(wǎng)絡(luò)協(xié)議的一致性測試是一種功能性的黑盒測試,通常包括靜態(tài)測試和動態(tài)測試兩類,。靜態(tài)測試是指協(xié)議實現(xiàn)者向測試方提交“協(xié)議實現(xiàn)一致性聲明”與協(xié)議中的靜態(tài)一致性要求相比較,,動態(tài)測試是運行測試集對DUT(Device under Test)進行測試。

協(xié)議一致陛測試包括三個階段:第一階段是測試生成,,為特定協(xié)議產(chǎn)生獨立于所有協(xié)議實現(xiàn)的抽象測試集,;第二階段是測試實現(xiàn),把抽象測試集中的測試?yán)D(zhuǎn)換成可執(zhí)行的測試?yán)?;第三階段為測試執(zhí)行,,在特定的DUT上執(zhí)行測試用例。

通用網(wǎng)絡(luò)協(xié)議一致性測試平臺用于動態(tài)測試,,也分為三個階段:第一階段是對一個指定的協(xié)議生成一個測試套集,,根據(jù)協(xié)議的要求,這個測試套集可以在實現(xiàn)前對收發(fā)雙方進行的交互進行完全設(shè)定,,或者在某些需要雙方互動(字段值需要對方的數(shù)據(jù)來進行填寫)的字段給出一個變量,。第二階段是按照這個測試套集對被測設(shè)備的協(xié)議實現(xiàn)(DUT)進行黑盒測試;第三個階段是通過比較DUT的實際輸出與預(yù)期輸出的異同,,從而實現(xiàn)網(wǎng)絡(luò)協(xié)議的一致性測試,。

通用平臺對各個不同的協(xié)議可支持生成不同的測試套集,分別進行測試和一致性對比,。

2 通用平臺組成

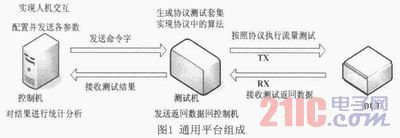

通用平臺由控制臺,、測試機兩部分組成。其中控制臺負責(zé)配置測試套集的策略,、測試結(jié)果的統(tǒng)計分析及人機交互,;測試機負責(zé)生成或接收測試套集,然后生成測試流發(fā)送到被測設(shè)備,;并從被測設(shè)備接收測試數(shù)據(jù),;然后將數(shù)據(jù)返回控制臺。如圖1所示,。

2.1 控制臺

控制臺硬件可以是一臺PC機,,其網(wǎng)卡與測試機控制口相連。在高層通過人機對話界面,,對協(xié)議,、算法及網(wǎng)絡(luò)參數(shù)進行配置,對測試套集生成模式及使用方式等進行策略設(shè)置;通過驅(qū)動程序與測試機進行通信,,向測試機輸入測試套集的參數(shù)配置,,并接收測試機輸出的結(jié)果;并對測試結(jié)果進行統(tǒng)計分析,。

軟件模塊包括界面模塊,、協(xié)議接口模塊、算法接口模塊,、網(wǎng)絡(luò)接口模塊,、通信模塊、統(tǒng)計分析模塊,。

2.2 測試機

2.2.1 硬件組成

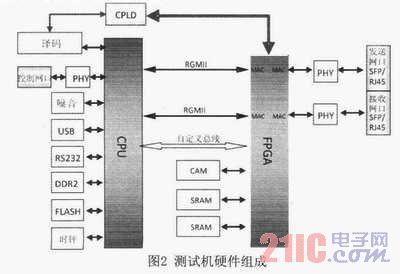

測試機硬件采用高性能,、高可靠性、高穩(wěn)定性的嵌入式多核處理器平臺,。配置高速100M,、1000M自適應(yīng)以太網(wǎng)口,可擴展的大容量DDR2內(nèi)存和大容量的Flash空間,。硬件框圖如圖2所示,,多核處理器平臺的核心部件為CPU、CPLD和FPGA,。

CPU主要用于接收來自控制機的網(wǎng)絡(luò),、協(xié)議、算法參數(shù)并生成實現(xiàn)網(wǎng)絡(luò)協(xié)議的測試套集,,它可以直接對被測設(shè)備發(fā)送或者接收測試流,,或者通過自定義總線將測試套集存儲在SRAM中,以實現(xiàn)快速的測試,;它還實現(xiàn)對外圍配套器件的控制,包括DDR,、Flash,、噪聲、日歷時鐘以及譯碼等,。CPU的PCI總線轉(zhuǎn)換出一個網(wǎng)絡(luò),,作為測試機的控制口,與控制機進行通信,。CPU的串口總線接出一個RS232串口,。

CPLD主要用于CPU啟動、數(shù)據(jù)總線的譯碼,、FPGA邏輯配置等處理,。

FPGA主要用于網(wǎng)絡(luò)接口處理和測試流發(fā)送、接收。首先,,它提供兩個軟MAC核與PHY芯片相連實現(xiàn)DUT的發(fā)送和接收網(wǎng)口,;其次,它提供另外兩個軟 MAC核可以允許CPU直接與DUT進行發(fā)送接收測試流,;也可以調(diào)用外部SRAM實現(xiàn)測試流發(fā)送接收等操作,。FPGA和CPU之間有兩種不同的通訊接口,一種是數(shù)據(jù)總線接口,,用于傳輸基本配置信息,、狀態(tài)信息和SRAM數(shù)據(jù);一種是RGMII網(wǎng)口接口,,用于傳輸測試流數(shù)據(jù),。

2.2.2 軟件組成

CPU軟件使用裁剪的定制LINUX操作系統(tǒng),內(nèi)核版本2.6以上,,配IPv4協(xié)議棧等,。CPU要實現(xiàn)的軟件功能比較多,軟件模塊有以下幾個:

(1)與控制機的通信模塊:負責(zé)接收來自控制機的網(wǎng)絡(luò),、協(xié)議,、算法參數(shù)以及其他命令,并回送測試結(jié)果,。

(2)算法實現(xiàn)模塊:實現(xiàn)協(xié)議中需要的算法,。

(3)套集生成模塊:這是實現(xiàn)一個協(xié)議所需要的IP包的集合,包括發(fā)送的IP包和接收的IP包,。每個不同的協(xié)議將產(chǎn)生定制的套集,。每個套集的主要流程就是生成指定的某個協(xié)議所需IP包的過程。但是在協(xié)議的實現(xiàn)上,,會按照協(xié)議的要求對相應(yīng)的字段進行邊界測試,、正確性和錯誤測試。并體現(xiàn)在不同的測試流里,。

(4)測試流發(fā)送模塊:將存儲在SRAM里的測試流發(fā)送至DUT,。

(5)測試流接收模塊:接收DUT發(fā)出的響應(yīng)流,存儲在SRAM里,。

(6)結(jié)果的協(xié)議分析模塊:CPU接收到測試流后,,將其按照協(xié)議要求拆分成各個字段,并與協(xié)議進行比對分析,。并將結(jié)果發(fā)送到與控制機的通信模塊,。

在發(fā)送IP包和接收IP包有關(guān)聯(lián)的情況下,比如IV向量由接收包傳遞過來后才能確定下一包發(fā)送的內(nèi)容,,必須由CPU直接進行測試,。

在協(xié)議比較簡單,,發(fā)送IP包和接收IP包沒有關(guān)聯(lián)的情況下,可以將測試套集裝載在SRAM里,,由FPGA進行測試,。這種情況下,也可以測試DUT的性能,。

3 工作流程與測試內(nèi)容

協(xié)議一致性測試的主要過程包括:標(biāo)準(zhǔn)測試套集生成,、測試執(zhí)行、結(jié)果分析三個部分,。標(biāo)準(zhǔn)測試套集是通過分析協(xié)議來確定要測試的各個方面,,從而產(chǎn)生測試用例的集合;測試執(zhí)行為測試用例的運行過程,;接收數(shù)據(jù)分析是對測試結(jié)果進行分析,,從而得到協(xié)議實現(xiàn)與協(xié)議說明是否一致的判決。如圖3所示,。

協(xié)議一致性測試的內(nèi)容包括三個方面:一是協(xié)議格式,、完整性的一致性測試,能夠正確識別收到的協(xié)議,,并且按照協(xié)議做出正確的響應(yīng),,響應(yīng)的格式要與協(xié)議一致。二是測試協(xié)議中包含的算法的正確性,。要能夠正確地加密和解密相應(yīng)的信息,。三是要對協(xié)議的實現(xiàn)過程包括握手、協(xié)商等進行一致性測試,。

4 測試套集的生成方法

測試套集的生成方法理論上有可達性分析與測試序列兩種,。可達性分析是從一個初始狀態(tài)出發(fā),,生成并檢查系統(tǒng)能夠到達的所有狀態(tài),。測試序列方法是針對FSM中的單個轉(zhuǎn)移生成的測試子序列,再將這些測試子序列連接起來作為完整的測試序列,。

通用平臺對測試套集的生成方法不作限定,。因為網(wǎng)絡(luò)協(xié)議千差萬別,套用某一個方法是不現(xiàn)實的,。因此不論什么方法,即使是手工方法,,只要能夠正確地詮釋協(xié)議,,生成的測試套集符合套集接口要求都可以直接輸入到平臺上實施測試。套集可以是完整的協(xié)議測試,,也可以是某個協(xié)議測試套集的一部分,。這樣大大方便了協(xié)議測試套集的調(diào)試與測試,。

通用平臺也提供了一種測試套集的生成方法。就是將協(xié)議的分析過程體現(xiàn)在控制機的界面上,,在界面上對協(xié)議進行分割,,確定轉(zhuǎn)移點和子序列,并給出子序列的數(shù)據(jù)范圍,。然后CPU的套集生成軟件將這些轉(zhuǎn)移點和子序列通過組合連接起來,,形成測試套集。

5 結(jié)束語

在協(xié)議一致性測試的需求越來越迫切的同時,,協(xié)議的功能越來越強,,復(fù)雜性也越來越高,使得測試難度越來越大,。通用平臺的硬件設(shè)計為以后協(xié)議的發(fā)展做好了可持續(xù)發(fā)展的基礎(chǔ),,而軟件設(shè)計也將提供開源和穩(wěn)定的接口以供協(xié)議的發(fā)展,增加對協(xié)議的支持,。