斯坦福大學與賽靈思研究實驗室(Xilinx Research Labs)聯(lián)手開發(fā)專門面向研究社群的第二代高速網絡" title="高速網絡">高速網絡設計平臺 NetFPGA" title="FPGA">FPGA-10G,。該新型平臺采用最先進的技術,,能夠幫助研究人員迅速構建高速復雜的原型,以解決網絡領域新出現(xiàn)的技術問題,。正如第一代平臺已在世界各地的大學中得到廣泛應用一樣,,我們希望新平臺能夠催生一個開源社區(qū),貢獻并共享IP,,從而加快創(chuàng)新步伐,。

開源軟件庫有助于軟件、IP核以及設計經驗的共享,,進而催生新一代網絡問題的解決方案,。

基礎平臺為最終用戶提供了迅速上手所需的所有要素,而開源社區(qū)則可以讓研究人員利用彼此的成果,,這樣一來最大限度地減少了理念實際實施所需的時間,,從而讓設計人員集中精力進行創(chuàng)新。

2007年,,我們開發(fā)出了第一代開發(fā)板NetFPGA-1G,,采用賽靈思Virtex-II Pro 50,主要用于電氣工程和計算機科學系學生的網絡硬件教學,。許多電氣工程和計算機科學的畢業(yè)生走上了開發(fā)網絡產品的崗位,,我們希望他們能夠有機會進行實際操作,,親自動手使用業(yè)界標準設計流程開發(fā)以線速運行且可植入正在運行的網絡中的硬件。為此,,最初的開發(fā)板必須具有低成本性,。在多家半導體供應商的慷慨捐贈下,我們得以把設計的最終價格壓到500美元以下,。結果許多大學很快采用了該開發(fā)板,,目前約有2,000個NetFPGA-1G開發(fā)板被世界各地的150個學院使用。

不過很快NetFPGA就超越了教學工具的范疇,。研究社群逐漸將其用于實驗和原型設計,。為此,NetFPGA小組提供了免費的開源參考設計,,并維護著有約50項研究人員所貢獻設計的設計庫,。我們?yōu)樾掠脩籼峁┲С郑\行在線論壇,,提供輔導資料,,舉辦夏令營和開發(fā)人員技術座談。

可編程技術勢在必行

10多年以來,,網絡技術在交換機,、路由器及其它產品中的發(fā)展越來越體現(xiàn)出轉發(fā)路徑的可編程性。這在很大程度上是因為隨著更多隧道格式,、服務質量方案,、防火墻過濾器和加密技術等的問世,網絡硬件日益復雜化,。加上日新月異的標準,,可編程技術勢在必行,比如說使用NPU或FPGA,。

研究人員往往想改變部分或所有轉發(fā)流水線,。近來,有許多人關注全新的轉發(fā)模型,,比如OpenFlow,。研究人員可以在全國范圍內在國家級測試平臺上,比如美國的GENI(http://geni.net)和歐盟的FIRE(http://cordis.europa.eu/fp7/ict/fire/calls_en.html)上試驗新型網絡架構,。

研究人員還越來越多地將NetFPGA開發(fā)板用于新理念的硬件原型設計,,諸如新的轉發(fā)模式、調度與查找算法,,以及新的深層數據監(jiān)測器,。NetFPGA開發(fā)板上最常見的參考設計是功能齊全的開源OpenFlow交換機,可以讓研究人員體驗到標準設計的各個變體,。另一項常用的參考設計則可以通過鏡像硬件中內核路由表并以線速轉發(fā)所有數據包來加速計算機主機內置的路由功能,。

第二代NetFPGA

在第二代平臺NetFPGA-10G上,,我們添加了易用性,旨在為最終客戶提供基本的基礎架構,,以簡化他們的設計工作,,這不僅擴大了我們的原始設計目標,而且這個目標與賽靈思主流目標設計平臺的目標很接近,,即除FPGA芯片外,,還為客戶提供工具、IP核和參考設計,,以加快設計流程,。

為實現(xiàn)這一目標,我們將以基礎IP構建塊和特定領域IP構建塊形式提供與FPGA基礎架構設計配套的開發(fā)板,,以增強易用性,,縮短開發(fā)時間。我們將進一步開發(fā)諸如網絡接口卡和IPv4參考路由器等參考設計,,以及協(xié)助設計構建,、仿真和調試的基本基礎架構。我們的想法是讓用戶把開發(fā)時間真正聚焦于他們特定的專業(yè)領域或者專題上,,無需深入了解底層硬件的詳細情況,。

與主流目標設計平臺不一樣,我們的網絡平臺針對的是一個與眾不同的最終用戶群體,,即囊括了學術研究和商業(yè)研究的這樣一個龐大的研究群體。為了讓該開發(fā)板得到廣泛采用,,多家半導體合作伙伴慷慨解囊,,期望能將其成本降至最低。賽靈思及Micron,、賽普拉斯半導體公司和NetLogic Microsystems等其他主力組件制造商也紛紛在向學術界最終用戶捐贈部件(商業(yè)研究人員則需給付更高的價格),。

這個項目的部分優(yōu)勢在于這個平臺得到了社區(qū)和開源硬件庫的支持,可以以最初的基礎方案為基礎,,促進軟件,、IP核和經驗的共享。這樣,,我們期望在眾多知名大學,、研究群體和企業(yè)的支持下,IP庫能夠日益擴大完善,,最終能夠覆蓋各種參考組件,、網絡IP核、軟件和尖端的基礎構架,。我們還期望通過提供精心設計的框架,,用系統(tǒng)的方法對專業(yè)知識和IP的共享稍加協(xié)調,,并采用具有標準接口的設計精良的即插即用型架構,就可以讓開源硬件庫不斷擴大,,從而催生新一代網絡問題的解決方案,。

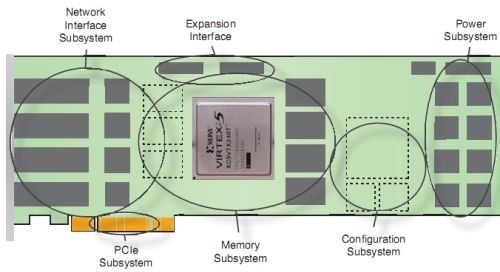

圖1:圍繞Virtex-5 FPGA構建的NetFPGA-10G板卡。

NetFPGA-10G是一種40Gb/s的PCI Express適配卡,,擁有龐大的FPGA架構,,能夠盡可能多地支持各種應用。如圖1所示,,該板卡設計以一個大型的賽靈思FPGA器件Virtex-5 XC5VTX240T-2為中心,。

圖2:FPGA開發(fā)板與網絡接口、PCIe,、擴展,、存儲器、配置和電源五個子系統(tǒng)相連,。

FPGA與5個子系統(tǒng)相連(見圖2),。第一個子系統(tǒng)是網絡接口子系統(tǒng),有4個帶有物理層器件的10Gbps以太網" title="以太網">以太網接口,,用于讓網絡流量進入FPGA,。第二個子系統(tǒng)是存儲子系統(tǒng),其由多個QDRII和RLDRAMII組件構成,。I/O主要用于該接口,,用來為諸如路由表或包緩存這樣的功能提供盡可能高的可用片外帶寬。第三個子系統(tǒng)是PCIe子系統(tǒng),。

第四個子系統(tǒng)是擴展接口,,用于加載子卡或與其它板卡通信。為此我們把所有剩余的高速串行I/O連接端都接到了兩個高速接插件上,。第五個子系統(tǒng)是配置子系統(tǒng),,用于FPGA的配置。

總體而言,,該板卡就是作為一個雙插槽,、全尺寸PCIe適配器來實現(xiàn)的。使用兩個插槽是出于散熱,、功耗和高度方面的考慮,。與高端圖形卡一樣,該板卡需要外接ATX電源,,因為FPGA在絕對最大負載條件下,,功耗可能會超過單槽PCIe允許的50W。不過該板卡也可在服務器環(huán)境外獨立運行。

存儲器子系統(tǒng)

我們設計流程的核心焦點是到SRAM和DRAM組件的接口,。因為FPGA器件上的I/O總數限制了可用的片外總帶寬,,我們必須小心地達成一定的妥協(xié),爭取盡量多支持一些應用,。要支持從網絡監(jiān)控到安全性,、路由、流量管理等各類應用,,會帶來很大不同的約束,。

例如,對外部存儲器存取來說,,網絡監(jiān)控器會采用一個大型的基于流量的統(tǒng)計表,,而且多數情況下可能還需要一個流量分類查找表。對兩者的存取都會帶來較短的時延,,因為流量分類需要對內部依賴性進行多次查找,,而流量統(tǒng)計表的更新則一般會覆蓋整個讀取—修改—寫入周期。因此,,SRAM是合適的器件選擇,。不過流量管理器主要需要大量存儲空間用于包緩存,通常出于密度要求,,還會采用DRAM組件,。對外部存儲器而言,最后可以考慮使用需要路由表查找和包緩存的IPv4路由器,。

總結各種應用的要求,,我們認識到某些功能會占用外部存儲器帶寬,不管是SRAM還是DRAM,。包緩存(要求大量存儲空間)適合采用DRAM,,SRAM則更適用于流量分類搜索存取、路由表查詢,、基于流量的數據統(tǒng)計表或基于規(guī)則的防火墻、用于包緩沖區(qū)實現(xiàn)的存儲器管理表以及報頭隊列等,。

所有這些功能都需要逐包執(zhí)行,。因此,假定在最惡劣的情況下最小尺寸的包是帶20字節(jié)開銷的64字節(jié),,系統(tǒng)需要處理的包率就是大約每秒6000萬個包,。其次,我們需要將存取做進一步的區(qū)分,。首先,,許多存儲器組件,比如QDR SRAM和RLDRAM SIO器件有獨立的讀/寫數據總線。由于存取模式不能假定為系統(tǒng)分布,,我們就無法匯聚總的存取帶寬,,不得不對單獨考慮每項業(yè)務。

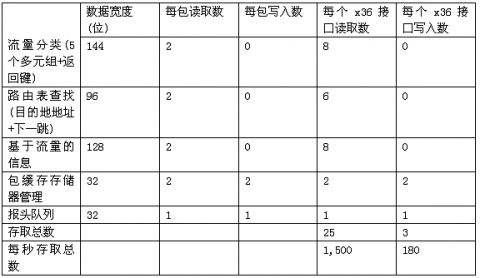

另外,,還存在第三類存取,,就是“搜索”。搜索可以通過基于TCAM的器件很好地完成,,搜索時延固定,,且確保能獲得搜索結果。不過,,出于價格和功耗方面的考慮,,以及TCAM會進一步限制I/O使用,我們不準備在我們的開發(fā)板上使用TCAM器件,。搜索還可以通過諸如決策樹,、哈希算法和分解法等其他方式來完成,可采用高速緩存也可不用,,僅以這些為例,。為了便于探討,我們假定完成一次搜索平均需要近兩次讀取,。鑒于此,,以及對數據寬度進行了一些慣常的假設后,我們將要求精簡為表1所示,。

表1:SRAM帶寬需求,。

假定接口上的時鐘速度為300MHz,那么QDRII接口可以實現(xiàn)每秒2X300=6億次讀/寫存取操作,。因此,,三個QDRII x36位的接口就可以滿足我們的所有要求。

對于DRAM存取,,我們主要考慮的是包存儲的方便程度,,僅從存儲器中對包進行一次讀/寫。把包開銷從原本進入的2x40Gbps中扣除后,,這相對于約62Gbps的存取帶寬,。用物理資源來衡量,RLDRAMII存取可以實現(xiàn)約97%的效率,,而DDR2或DDR3存儲設備則可能在40%左右,,因此會要求多得多的I/O。因此我們選擇了RLDRAMII CIO組件,。兩個運行在300MHz的64位RLDRAMII接口提供的總帶寬可以大致滿足這個要求,。

網絡接口

NetFPGA-10G的網絡接口由4個能夠以10Gbps或1Gbps以太網鏈路方式運行的子系統(tǒng)構成。為了最大化平臺的利用率和最小化功耗,我們使用了4個增強型小型封裝可熱插拔(SFP+)模塊(cage)作為物理接口,。與XENPAK和XFP等其他10G收發(fā)器標準相比,,SFP+在功耗和尺寸方面有著明顯的優(yōu)勢。使用SFP+模塊,,可以支持一系列接口標準,,包括10GBase-LR、10GBase-SR,、10GBase-LRM和低成本直聯(lián)SFP+銅纜(雙同軸),。此外,還可以利用針對1Gpbs運行的SFP模塊,,從而支持1000Base-T或1000Base-X物理標準,。

4個SFP+模塊每個都通過SFI接口連接到一個NetLogic AEL2005器件。AEL2005是一個帶有符合IEEE 802.3aq規(guī)范的嵌入式電分散補償引擎的10Gb以太網物理層收發(fā)器,。除了常規(guī)的10G模式,,該物理層器件還能夠支持千兆位以太網(1G)模式。在系統(tǒng)側,,這些物理層器件通過一個10Gb連接單元接口(XAUI)連接到FPGA,。在1G模式下工作時,其中一個XAUI信道用作串行千兆位介質無關接口(SGMII),。

Virtex-5 FPGA內部提供適當的IP核,。對于10Gbps的業(yè)務,賽靈思推出了XAUI LogiCORE IP核和10Gb以太網媒體訪問控制器(10GEMAC)LogiCORE IP核,。對于1G的業(yè)務,,接口可以直接連接至賽靈思嵌入式三態(tài)以太網MAC內核。

PCIe子系統(tǒng)

NetFPGA-10G平臺使用開放式組件可移植性基礎架構(OpenCPI)作為開發(fā)板和計算機主機通過PCIe互聯(lián)的主要互聯(lián)實現(xiàn)方式[7],。我們目前支持x8的第一代,,將來可能會升級到支持第二代。OpenCPI是一種通用開源框架,,用于連接使用不同類型的通信接口,、且?guī)捄蜁r延要求不同的IP模塊(串流、字節(jié)可尋址等),。就其本質來說,,OpenCPI是一種高度可配置的框架,能夠為用于快速實現(xiàn)新設計的IP核提供關鍵性的通信“橋梁”,。

OpenCPI為NetFPGA-10G平臺帶來了一些關鍵特性。在軟件側,,我們能夠提供無干擾(clean)DMA接口,,用于傳輸數據(主要是數據包,雖然也有其他類型的信息)以及通過編程的輸入/輸出控制器件。對于網絡應用,,我們提供Linux網絡驅動程序,,將網絡接口導出到NetFPGA器件上的每個物理以太網端口上。這樣可以讓用戶空間軟件把網絡數據包傳輸到器件上,,并且讀取設計中任何主機可視寄存器,。

在硬件側,OpenCPI為我們提供了無干擾,、甚至多種數據流接口,,而且每個接口都可以通過OpenCPI框架進行配置。此外,,OpenCPI能夠處理主機側和硬件側所有的緩存和PCIe事務處理,,這樣用戶就能夠集中精力進行特定應用開發(fā),而不必處理器件通信的細節(jié),。

擴展接口與配置子系統(tǒng)

擴展接口子系統(tǒng)的目的是讓用戶通過連接第二塊NetFPGA-10G板卡來增加端口密度,,比如通過光學子卡來豐富網絡接口特性,或者通過高速串行接口連接更多搜索組件,,比如基于知識的處理器等,。我們將FPGA上的20個GTX收發(fā)器取出,然后通過AC耦合傳輸線連接到兩個高速接插件上,。這些接插件是為諸如XAUI,、PCIe、SATA和Infiniband這樣的傳輸接口設計的,,既可以通過匹配接插件直接連接到另一塊板卡上,,也可以通過電纜組件連接到另一塊板卡上。每條傳輸線經測試雙向傳輸速率均可達到6.5Gbps,,從而為進出FPGA提供了一條額外的130Gbps數據路徑,。

使用不斷變大的比特流位寬來配置FPGA,如果器件的配置時間超過PCIe的限制,,可能就會出現(xiàn)問題,。V5TX240T就會遇到這樣的問題:平臺閃存器件的存取速度遠遠低于V5TX240T理論上能夠處理的速度,從而帶來了瓶頸,。作為應對措施,,設計人員可以考慮配置部分比特流,并通過并行方式存取平臺閃存器件,,從而以最大速度配置FPGA,。為了提高實現(xiàn)的可能性,我們?yōu)榘蹇ㄅ鋫淞藘蓚€平臺閃存器件,,可以通過CPLD連接到FPGA的配置接口,。此外,,該板卡還支持標準的JTAG編程接口。

FPGA設計

構建成功的開源庫的一個關鍵因素是嚴格的架構規(guī)范以及標準的,、抽象且定義準確的接口,。實際上,我們認為這些接口對提供一個能夠輕松地將大型全球性社區(qū)貢獻的組件組合在一起的構建塊系統(tǒng)具有重要的意義,。標準化保證了物理兼容性,,物理連接功能之外的清晰定義避免了對接口協(xié)議的誤解。在理想的情況下,,用戶可以不對實施內在的知識做詳細了解,,就可以部署抽象組件。

作為完整平臺發(fā)布的一部分,,我們將提供完備的架構規(guī)范和帶有關鍵組件的參考設計,。這些關鍵組件包括:

OpenCPI的PCIe端點;

4個XAUI LogiCORE IP模塊和4個10G模式下的10GEMAC LogiCORE內核(后者許可協(xié)議下使用),;

2個基于XAPP852的RLDRAMII存儲器控制器,;

3個基于MIG3.1的QDRII存儲器控制器;

用以檢查時鐘頻率和加電完畢信號,,并生成所有所需系統(tǒng)時鐘的時鐘及復位模塊,;

針對1G運行模式的三態(tài)以太網MAC(TEMAC);

用于配置物理層器件的MDIO接口,;

帶有能夠處理所有管理任務的支持系統(tǒng)的MicroBlaze控制處理器,;

UART接口;

配置控制和比特流工具箱,,為平臺閃存器件提供編程路徑,;

可將所有輸入流量整合成一個數據流的輸入仲裁器;

可將流量分配給指定的輸出端口的輸出仲裁器,。

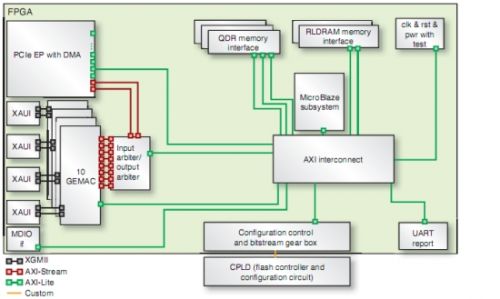

圖3顯示了這些組件如何互聯(lián),,以支持10G業(yè)務。對數據傳輸,,我們選擇了AMBA 4 AXI串流協(xié)議,。對控制流量,則選擇了基于AMBA4 AXI-Lite的接口,。

圖3:面向10G業(yè)務的FPGA設計架構基于AXI協(xié)議,。

發(fā)展現(xiàn)狀與未來展望

NetFPGA-10G板卡的設計驗證已經完成。一旦完成產品測試平臺開發(fā),,該板卡可立即投入生產,。目前正在進行FPGA的初步設計和首次發(fā)布相關代碼。