1 引言

在石英晶體的中間測(cè)試中,需要測(cè)量串聯(lián)諧振頻率、串聯(lián)諧振電阻、負(fù)載諧振頻率、負(fù)載諧振電阻、靜電容、動(dòng)電容、頻率牽引靈敏度和DLD等參數(shù)。其中,靜電容C0主要由石英晶體兩端所鍍銀膜決定,表征了石英晶體的靜態(tài)特性,與石英晶體的串聯(lián)諧振頻率和負(fù)載諧振頻率等應(yīng)用指標(biāo)密切相關(guān)。

目前,IEC(國(guó)際電工委員會(huì))所推薦的石英晶體測(cè)量的標(biāo)準(zhǔn)方法是π網(wǎng)絡(luò)零相位法。在該方法中,未規(guī)定測(cè)量靜電容的標(biāo)準(zhǔn)方法。若采用諧振法、交流電橋法等常用方法來(lái)測(cè)量靜電容,會(huì)增加整個(gè)測(cè)量系統(tǒng)的復(fù)雜性,并且對(duì)諧振頻率的測(cè)量產(chǎn)生不利影響。本課題提出了一種基于π網(wǎng)絡(luò)零相位法的測(cè)量石英晶體靜電容的新方法,并據(jù)此設(shè)計(jì)制作了實(shí)驗(yàn)測(cè)量系統(tǒng)。

2 測(cè)量原理與電路

2.1石英晶體的等效電參數(shù)模型

石英晶體的等效電參數(shù)模型如圖1所示:

諧振器靜電容測(cè)量方法" height="118" src="http://files.chinaaet.com/images/20110728/cf34e83c-b282-4358-a132-fb89dd433ff2.jpg" width="214" />

其中,C0是石英晶體兩電極間的電容,稱為石英晶體的靜電容,C1稱為石英晶體的動(dòng)電容,L1稱為石英晶體的動(dòng)電感,R1表示石英晶體在振動(dòng)時(shí)的損耗,稱為串聯(lián)諧振電阻。當(dāng)激勵(lì)信號(hào)的頻率等于石英晶體的諧振頻率時(shí),其等效電參數(shù)模型為純電阻。由于C1、L1的值非常小,當(dāng)激勵(lì)信號(hào)的頻率遠(yuǎn)離石英晶體的諧振頻率時(shí),R1、C1、L1的影響可以忽略不計(jì),此時(shí),石英晶體等效成一個(gè)值為C0的電容。

2.2 π網(wǎng)絡(luò)法原理

IEC所推薦的π網(wǎng)絡(luò)如圖2所示:

網(wǎng)絡(luò)的阻抗與測(cè)試儀表的阻抗相匹配,并衰減來(lái)自測(cè)試儀器的反射信號(hào)。M為待測(cè)石英晶體。Va是輸入激勵(lì)信號(hào),Vb是π網(wǎng)絡(luò)輸出信號(hào),它們都是矢量電壓信號(hào)。當(dāng)石英晶體處于諧振狀態(tài)時(shí),其表現(xiàn)為純電阻特性,此時(shí)Va與Vb之間相位差為零,Va的頻率即為石英晶體的串聯(lián)諧振頻率。所以,通過(guò)改變Va的頻率并檢測(cè)Va與Vb之間相位差可以找到石英晶體的諧振頻率。對(duì)于π網(wǎng)絡(luò)中石英晶體的靜電容如何測(cè)量,IEC并未推薦標(biāo)準(zhǔn)方法。pπ網(wǎng)絡(luò)由對(duì)稱的雙π型電阻回路組成,R1、R2和R3構(gòu)成輸入衰減器,R4、R5和R6構(gòu)成輸出衰減器,它們的作用是使

2.3 常用測(cè)電容的方法

常用的測(cè)量電容方法主要有諧振法、交流電橋法和充放電法。諧振法是將電容引入振蕩電路中,使得振蕩頻率成為電容的函數(shù),通過(guò)測(cè)量該頻率值來(lái)計(jì)算電容值。交流電橋法將電容接入交流電橋中,調(diào)整電橋中的可調(diào)電阻和可調(diào)電容使得電橋平衡,根據(jù)平衡時(shí)電橋各臂的電阻和電容值計(jì)算被測(cè)電容值。充放電法使用交流信號(hào)源對(duì)電容充電,然后將電容接入放電電路中,通過(guò)測(cè)量電容的放電時(shí)間來(lái)計(jì)算電容值。由于π網(wǎng)絡(luò)法是通過(guò)測(cè)量π網(wǎng)絡(luò)兩端的矢量電壓來(lái)得到石英晶體電參數(shù)值,與上述三種方法并不一致,所以如果采用這三種方法測(cè)量石英晶體的靜電容都需要增加額外的測(cè)量電路,并且會(huì)因此增加π網(wǎng)絡(luò)電路的雜散項(xiàng),對(duì)測(cè)量石英晶體的諧振頻率產(chǎn)生不利影響。

2.4 基于π網(wǎng)絡(luò)的靜電容測(cè)量方法

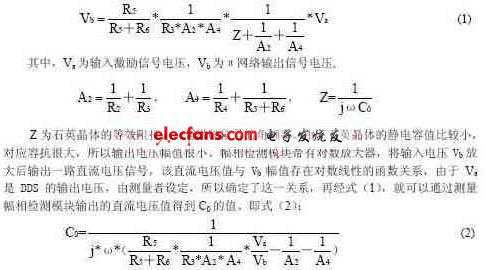

利用DDS(直接數(shù)字頻率合成)信號(hào)源作為激勵(lì)源,其輸出交流信號(hào)頻率遠(yuǎn)離石英晶體諧振頻率,該信號(hào)激勵(lì)接有被測(cè)石英晶體的π網(wǎng)絡(luò)。此時(shí),石英晶體等效于一個(gè)值為C0的電容。π網(wǎng)絡(luò)的輸出電壓與該電容存在一定的函數(shù)關(guān)系,由于輸入電壓和π網(wǎng)絡(luò)的參數(shù)已知,測(cè)量輸出電壓并根據(jù)這一函數(shù)關(guān)系,可以計(jì)算出C0值。這種方法與測(cè)石英晶體諧振頻率的方法很相似,都需要利用DDS輸出信號(hào)作為激勵(lì)信號(hào)并檢測(cè)π網(wǎng)絡(luò)輸出的矢量電壓。兩者區(qū)別在于測(cè)量諧振頻率要求檢測(cè)輸入電壓和輸出電壓之間相位差,而測(cè)量靜電容則要求測(cè)量輸入電壓和輸出電壓的幅值。因此,對(duì)這兩個(gè)矢量電壓信號(hào)采用幅相檢測(cè)的辦法可以使測(cè)量石英晶體的諧振頻率和靜電容統(tǒng)一起來(lái)。

原理框圖如圖3所示:

其中,DDS輸出兩路幅值、頻率和相位均相同的信號(hào)。一路激勵(lì)π網(wǎng)絡(luò),另一路輸入幅相檢測(cè)模塊。本課題要求石英晶體諧振頻率的測(cè)量范圍為0~200MHz。在這一范圍內(nèi)選取30MHz和68MHz兩個(gè)頻率點(diǎn)作為激勵(lì)信號(hào)的設(shè)定頻率。具體方法是,當(dāng)石英晶體的諧振頻率在30MHz附近時(shí),設(shè)定DDS輸出信號(hào)頻率為68MHz,反之,則設(shè)為30MHz。激勵(lì)信號(hào)經(jīng)過(guò)π網(wǎng)絡(luò)后輸出電壓如式

3 測(cè)試系統(tǒng)設(shè)計(jì)

3.1 測(cè)試系統(tǒng)硬件設(shè)計(jì)

測(cè)試系統(tǒng)硬件框圖如圖4所示:

測(cè)試系統(tǒng)硬件由計(jì)算機(jī)、CPLD芯片、DDS信號(hào)源、π網(wǎng)絡(luò)、幅相檢測(cè)模塊和A/D轉(zhuǎn)換器組成。其中, CPLD、DDS、幅相檢測(cè)模塊和A/D轉(zhuǎn)換器集成在一塊PCI擴(kuò)展板上。作為控制核心的計(jì)算機(jī)通過(guò)PCI接口發(fā)出的地址和數(shù)據(jù)信號(hào)由CPLD芯片轉(zhuǎn)換為相應(yīng)的控制邏輯控制DDS、幅相檢測(cè)模塊和A/D轉(zhuǎn)換器工作。DDS信號(hào)源發(fā)出設(shè)定頻率、相位和幅值的信號(hào)激勵(lì)π網(wǎng)絡(luò)。π網(wǎng)絡(luò)上帶有插座,可插入晶體或電阻、電容等元器件。π網(wǎng)絡(luò)輸出的矢量電壓信號(hào)Vb接入幅相檢測(cè)模塊。幅相檢測(cè)模塊的輸出直流電壓輸入A/D轉(zhuǎn)換器,轉(zhuǎn)換為數(shù)字信號(hào)后經(jīng)CPLD輸入計(jì)算機(jī)。

3.2 測(cè)試系統(tǒng)軟件設(shè)計(jì)

測(cè)試軟件采用Visual C++語(yǔ)言編寫(xiě),實(shí)現(xiàn)人機(jī)交互界面、測(cè)量控制和數(shù)據(jù)處理的功能。測(cè)量控制包括對(duì)DDS各通道頻率、相位和幅度控制字的設(shè)置,以及對(duì)A/D轉(zhuǎn)換器內(nèi)部指令寄存器的寫(xiě)入和轉(zhuǎn)換結(jié)果的讀取。數(shù)據(jù)處理部分主要是對(duì)已轉(zhuǎn)換為數(shù)字量的幅相檢測(cè)模塊的輸出直流電壓進(jìn)行計(jì)算,由前述關(guān)系得出靜電容的值。由于在實(shí)際測(cè)量條件下, 該直流電壓與Vb之間并不是嚴(yán)格的對(duì)數(shù)線性關(guān)系,所以需要對(duì)這一函數(shù)關(guān)系進(jìn)行擬合,根據(jù)擬合后的關(guān)系,可由直流電壓值計(jì)算出Vb,然后按照前面所列方程,得到靜電容C0的值。

4 實(shí)驗(yàn)數(shù)據(jù)與處理

以S&A公司的250B作為標(biāo)準(zhǔn)儀器,將采用本方案所測(cè)得的C0值與250B的測(cè)量結(jié)果進(jìn)行比對(duì),檢驗(yàn)測(cè)量精度是否滿足工業(yè)生產(chǎn)要求。在工業(yè)生產(chǎn)中,要求石英晶體靜電容的測(cè)量范圍為1~10pF,測(cè)量誤差小于0.1pF。實(shí)驗(yàn)數(shù)據(jù)如表1所示:

5 結(jié)論

在π網(wǎng)絡(luò)零相位法的基礎(chǔ)上,采用了“DDS激勵(lì)、π網(wǎng)絡(luò)響應(yīng)、幅相檢測(cè)計(jì)算容抗”的方法測(cè)量石英晶體的靜電容,并由此設(shè)計(jì)制作了實(shí)驗(yàn)測(cè)量系統(tǒng)來(lái)實(shí)現(xiàn)該方案。該方法把測(cè)量石英晶體的靜電容和諧振頻率統(tǒng)一起來(lái),簡(jiǎn)化了測(cè)量電路。通過(guò)實(shí)際測(cè)量一批晶體和小電容,證明在1~10pF范圍內(nèi)測(cè)量誤差小于0.1pF,能滿足實(shí)際要求,可以在此基礎(chǔ)上開(kāi)發(fā)實(shí)際的石英晶體中間測(cè)試系統(tǒng)。