隨著便攜式電子設備的廣泛使用,系統(tǒng)集成度越來越高。對于數(shù)/模混合的片上系統(tǒng)中,數(shù)字電路對模擬電路的干擾加大,因此模擬電路與數(shù)字電路需要施加獨立電源,以減小數(shù)/模混合帶來的相互干擾以及動態(tài)調整功耗。全集成型LDO線性穩(wěn)壓器可以用來為系統(tǒng)中各子模塊單獨供電,具有抑制電源噪聲,減小干擾,同時消除鍵合線電感引入的瞬態(tài)脈沖的優(yōu)點,此外還可以減小片外器件和芯片引腳,所以全集成型LDO線性穩(wěn)壓器成為片上系統(tǒng)(SoC)型集成電路中不可或缺的模塊。由于LDO的負載電流變化大,且調整管尺寸較大,為滿足LDO的穩(wěn)定性要求,必須對LDO進行頻率補償。傳統(tǒng)方法是利用負載電容的ESR進行補償,但是,全集成型LDO不允許使用片外電容,因此設計一個不需片外電容,穩(wěn)定,響應速度快的LDO是面臨的主要挑戰(zhàn)。

1 LDO原理與頻率補償

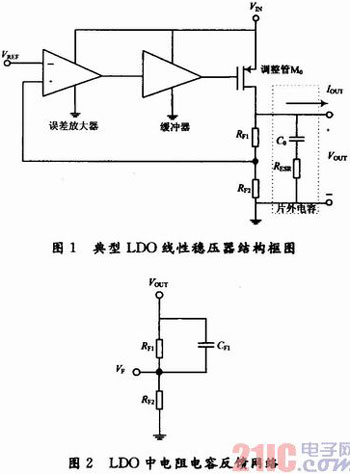

LDO線性穩(wěn)壓器的傳統(tǒng)電路結構如圖1所示,由誤差放大器,緩沖器,調整管M0,分壓電阻RF1,RF2,以及片外濾波電容C0和其寄生的等效串聯(lián)電阻RESR組成。片外電容C0和RESR組成的零點用來抵消LDO中第2個極點,從而達到環(huán)路穩(wěn)定。當沒有片外電容補償時,由于輸出負載電流變化大,LDO的輸出極點變化大,環(huán)路穩(wěn)定性設計變得困難。Leung提出了衰減系數(shù)控制頻率補償法(Damping Factor Control Compen-sation,DFC)和引入零點補償,在穩(wěn)定性,響應時間方面具有較好的特性。Milliken采用在調整管的輸入端和輸出端之間加入一個微分器,將調整管輸入節(jié)點和輸出節(jié)點的2個極點分離,從而在只使用片內電容時依然保持穩(wěn)定。Kwok使用動態(tài)密勒電容補償技術,通過串聯(lián)一個在線性區(qū)工作的PMOS管作為動態(tài)可調電阻,在誤差放大器的輸出端引入一個動態(tài)零點抵消LDO的輸出極點,實現(xiàn)系統(tǒng)穩(wěn)定。本文中則采用在負載端引入零點,補償誤差放大器輸出極點的方法,避免了為補償LDO輸出極點,而需要大電容和動態(tài)調整電阻的要求,且減小了需要的補償電容值,降低了芯片面積。

2 電路設計

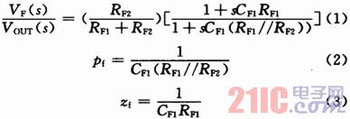

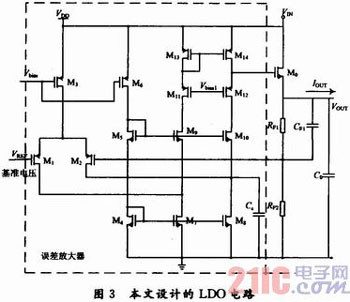

圖2為所設計的LDO線性穩(wěn)壓器電路,誤差放大器為折疊式共源共柵結構,由M1~M14組成,M0為輸出調整管,反饋網絡由RF1,RF2和CF1組成,電容Cc為誤差放大器的補償電容。

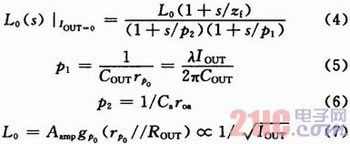

圖2中電阻電容反饋網絡的傳輸函數(shù)為:

這種反饋網絡產生了一個零點zf和一個較高的極點pf,設置極點pf大于單位增益頻率,即RF2//RF1>1/(CF1·pf)。

不施加片外電容時,LDO的傳輸函數(shù)為:

式中:Ca,roa為分別誤差放大器輸出a端的寄生電容和輸出電阻;gp0,rp0分別為調整管M0的跨導和小信號輸出電阻;Aamp為誤差放大器的增益。由式(7)增益L0隨著負載電流增大而降低,而極點p1隨負載電流增大而升高,極點p2基本保持不變,對于不施加片外電容,其等效串聯(lián)電阻RESR所提供的零點不存在,在輸出負載電流IOUT=0時,調整管輸出電阻rp0最大,gmp0最小,故小負載電流時,環(huán)路穩(wěn)定性變差。為滿足LDO穩(wěn)定性要求,IOUT必須有一個最小輸出電流,以保證M0的輸出極點P1不會太低。為保證極點P2和零點zf相近而抵消,須適當減小調整管M0尺寸。在本應用中,LDO輸入電壓為2.5V,用于為1.2V核心電路供電,調整管M0的VDS=1.3V,所以M0可以取較小尺寸。

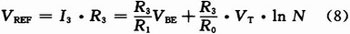

本設計采用了一階溫度補償帶隙基準電壓源,圖4所示為帶隙基準電壓源的核心電路,這里采用了典型的一階溫度補償電流模結構。其中M1,M2和M3寬長比相同,R1=R2,A0為誤差放大器,誤差放大器的同相端接Va端,反相端接Vb端。為了保證電路的穩(wěn)定性,必須保證電路中由M1,Q1和R1組成的正反饋網絡的反饋系數(shù)小于M2,R2,Q0和R0組成的負反饋網絡的反饋系數(shù),即要求:

運算放大器A0使Va,Vb兩點電壓相等,忽略電阻的溫度系數(shù),電流I0為PTAT電流,I1為CTAT電流。通過選擇![]() ,可以得到-40~+85℃范圍內溫度系數(shù)小于4.76ppm/℃。

,可以得到-40~+85℃范圍內溫度系數(shù)小于4.76ppm/℃。

3 仿真驗證

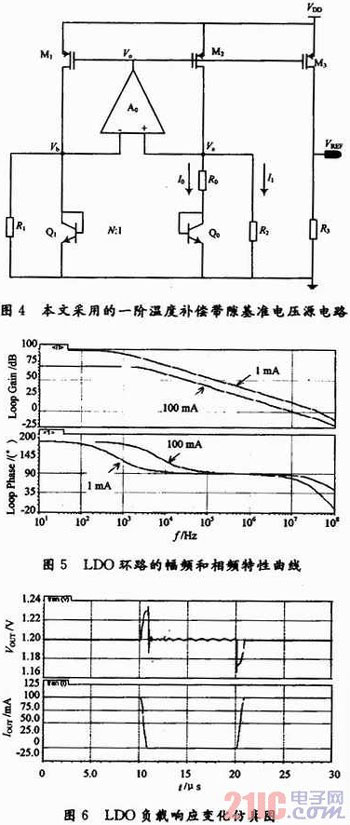

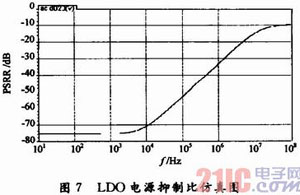

該電路采用SMIC 0.25μm CMOS工藝實現(xiàn),輸入電源電壓為2.5V,輸出電壓為1.2V,作為芯片模擬部分的電源。LDO的環(huán)路穩(wěn)定性采用Spectre stb仿真,結果如圖5所示,負載電流從1mA變化到100mA,整個系統(tǒng)相位裕度均在40°以上,系統(tǒng)穩(wěn)定。圖6為負載電流從1mA到100mA轉換時,輸出電壓和輸出電流瞬態(tài)響應曲線。從圖中可以看出,瞬態(tài)響應過沖小于20mV,無振鈴現(xiàn)象產生。圖6為仿真的電源電壓抑制比(PSRR)。低頻時PSRR好于75dB。整個LDO包括基準電壓源共消耗靜態(tài)電流390μA。

4 結語

本文設計了一種全集成型LDO線性穩(wěn)壓器,采用一種簡單的頻率補償電路,通過輸出反饋電路引入零點,抵消了LDO產生第二個極點,獲得較好的穩(wěn)定性。此方法結構簡單、不損失環(huán)路開環(huán)增益、帶寬高,而且所需要的補償電容小,節(jié)省芯片面積和輸出引腳。