目前,片上系統(tǒng)(SOC)芯片已經(jīng)在無(wú)線通信、工業(yè)控制、視頻監(jiān)控等領(lǐng)域得到了越來(lái)越廣泛的應(yīng)用,SOC系統(tǒng)需要考慮接口驅(qū)動(dòng)電路、動(dòng)態(tài)電源管理和電源電路等問(wèn)題,其中,良好的電源電路是成功實(shí)現(xiàn)系統(tǒng)功能的重要保障。本文就應(yīng)用于視頻監(jiān)控的TMS320DM64xx系列SOC外部電源電路的設(shè)計(jì)進(jìn)行了討論。

1 TMS3320DM64xx系列SOC對(duì)電源的要求

TMS3320DM64xx系列SOC是應(yīng)用于數(shù)字視頻的片上處理平臺(tái),具有DSP與ARM雙核結(jié)構(gòu),需要內(nèi)核與I/0兩種電源,而內(nèi)核電源又分為CVDD(1.2V)和CVDDDSP(1.2V),I/0電源分為DVDDl8(1.8V),DVDDR2(1.8V),DVDD33(3.3V)。由于通常TMS3320DM64xx用于嵌入式系統(tǒng)中,因而,電源電路設(shè)計(jì)不僅要考慮電壓的精度、穩(wěn)定度和外圍電路的復(fù)雜度等問(wèn)題,還要考慮低功耗問(wèn)題,另外根據(jù)設(shè)計(jì)工藝,為了保證芯片正常工作,在系統(tǒng)上電、關(guān)機(jī)及穩(wěn)壓操作時(shí),對(duì)這幾種電源還有一定的排序要求,如果違反該要求,可能降低器件的性能或永久損壞器件。

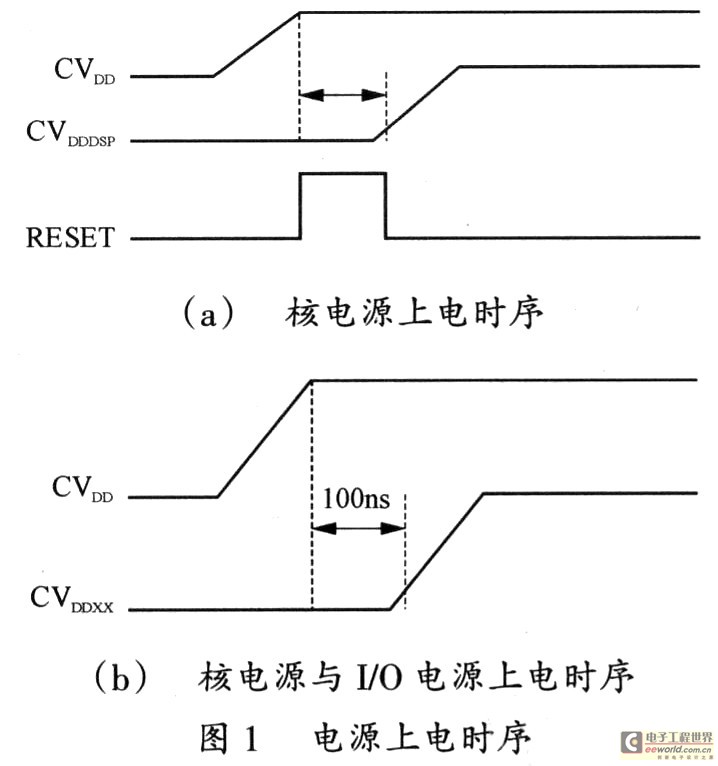

圖1(a)、圖1(b)分別顯示的是內(nèi)核電源之間以及內(nèi)核電源與I/0電源之間的上電時(shí)序。內(nèi)核電源的上電時(shí)序依賴復(fù)位時(shí)選擇的DSP啟動(dòng)模式:如果DSP初始化模式被配置為自啟動(dòng)模式,要求兩個(gè)內(nèi)核電源同時(shí)上電;如果DSP被配置為主機(jī)啟動(dòng)模式(即ARM啟動(dòng)DSP),要求兩個(gè)內(nèi)核電源分別上電,CVIDD優(yōu)先于CVDDDSP,而CVDDDSP必須在復(fù)位信號(hào)開啟(關(guān)閉)之前上電。如圖1(b)所示,I/O電源必須在CVDD電源上電后的100ns內(nèi)上電,各個(gè)I/O電源的上電順序沒有要求。

根據(jù)TMS3320DM64xx SOC的數(shù)據(jù)手冊(cè),內(nèi)核電源的最大電流為767mA,而I/O電源的最大工作電流是102 mA,參考TI提供的相關(guān)方案分析得出,性能優(yōu)越的TPS543lx(x=0,l,2,3,4,5,6)系列DC/DC調(diào)節(jié)器符合系統(tǒng)設(shè)計(jì)要求,其中,TPS54310的輸出可調(diào),而沒有內(nèi)部補(bǔ)償功能;其它芯片的輸出不可調(diào),而具有內(nèi)部補(bǔ)償。盡管具有內(nèi)部補(bǔ)償?shù)男酒軌蚬?jié)約電路板空間并減少芯片總量,但由于多種型號(hào)芯片共存會(huì)引起調(diào)試難度的增大,故采用具有可調(diào)輸出特性的TPS54310以降低系統(tǒng)調(diào)試難度。

2 TPS54310特性分析

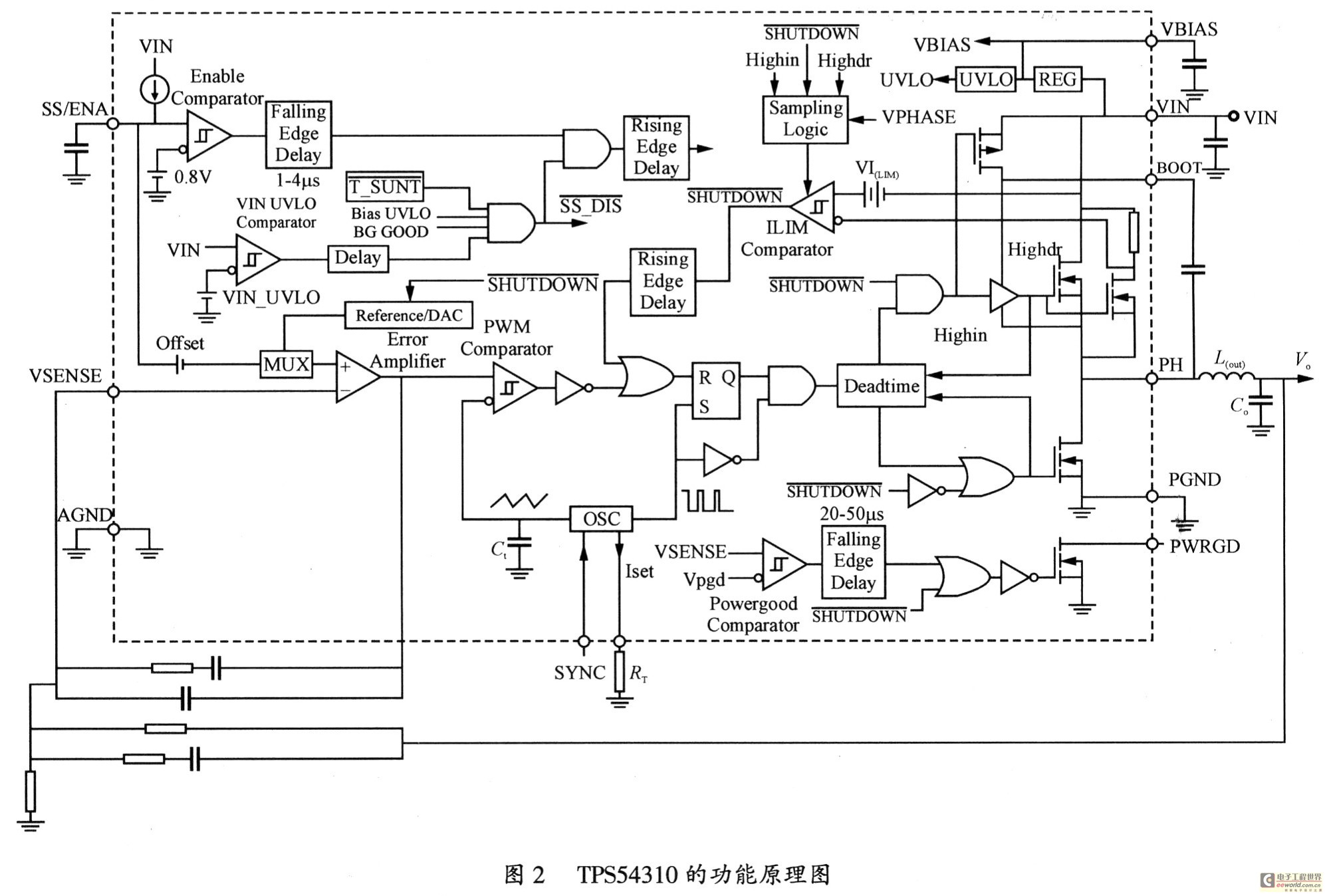

TPS54310是一款開關(guān)電源調(diào)節(jié)器,其功能原理圖如圖2所示,能夠?qū)崿F(xiàn)低電壓輸入和高電流輸出(輸入電壓范圍為3~6V,輸出電壓在0.9~3.3V之間可調(diào),輸出電流為3A);內(nèi)部具有電壓誤差放大器,能夠提高瞬態(tài)響應(yīng)條件下的工作性能;可以分別從內(nèi)部或外部設(shè)置慢啟動(dòng)方式;其良好的電源輸出特性可用于處理器/邏輯復(fù)位、故障信號(hào)檢測(cè)和連續(xù)電源。

通過(guò)配置相應(yīng)管腳或?qū)?nèi)部編程可以實(shí)現(xiàn)以下功能。

2.1 靈活控制器件的啟動(dòng)/關(guān)斷特性

上電過(guò)程中,當(dāng)輸入電壓不夠時(shí),將內(nèi)部電路置于靜止?fàn)顟B(tài),器件不工作;輸入電壓開始等于并超出正常的起始門限(2.95V)時(shí),激活內(nèi)部電路,控制器件開始工作。電壓穩(wěn)定后,當(dāng)輸入電壓幅度再次降低到關(guān)閉門限(2.8V)時(shí),器件停止工作。另外,由于內(nèi)部比較器的滯后作用和2.5μs上升與下降沿抗尖峰電路的存在,降低了由于混入輸入電壓內(nèi)的噪聲而引起器件瞬間關(guān)斷的可能性。

2.2 自定義啟動(dòng)時(shí)間

通過(guò)在SS/ENA(慢啟動(dòng)/芯片使能)管腳和AGND(模擬地)管腳之間加一個(gè)小電容(Css)能夠達(dá)到延長(zhǎng)啟動(dòng)時(shí)間的目的,延遲時(shí)間的計(jì)算公式為

2.3 設(shè)定轉(zhuǎn)換頻率

轉(zhuǎn)換頻率可以被設(shè)定為固定的350kHz或550kHz內(nèi)部振蕩器頻率,也可以被設(shè)定為可調(diào)的280kHz~700kHz。振蕩頻率的設(shè)定由SYNC和RT管腳共同決定,當(dāng)SYNC懸空或接地,而RT懸空時(shí),轉(zhuǎn)換頻率為350kHz;當(dāng)SYNC接入大于2.5V的電壓,而RT懸空時(shí),轉(zhuǎn)換頻率為550kHz;當(dāng)SYNC懸空,而RT與地之間接入68k到180k之間的電阻時(shí),轉(zhuǎn)換頻率為可調(diào)的280kHz~700kHz。

2.4 過(guò)電流保護(hù)

判斷電流流向,當(dāng)電流從VIN流向PH時(shí),啟動(dòng)高端場(chǎng)效應(yīng)管和差分放大器,器件能夠感知流經(jīng)高端場(chǎng)效應(yīng)管和差分放大器的電流,并將之與過(guò)電流門限進(jìn)行比較,限流操作在每開關(guān)周期內(nèi)進(jìn)行。當(dāng)達(dá)到限流門限時(shí),高端場(chǎng)效應(yīng)管會(huì)在200ns時(shí)間內(nèi)關(guān)斷,在吸收電流過(guò)量時(shí),由熱關(guān)斷電路進(jìn)行負(fù)載保護(hù)。

2.5 熱關(guān)斷

當(dāng)溫度超出150℃時(shí),使用熱關(guān)斷電路關(guān)閉內(nèi)部場(chǎng)效應(yīng)管的電源,當(dāng)溫度低于熱關(guān)斷觸發(fā)點(diǎn)10℃時(shí),器件停止關(guān)斷狀態(tài),并在慢啟動(dòng)電路的控制下重新開始工作。

3 基于TPS54310的SOC電源電路設(shè)計(jì)

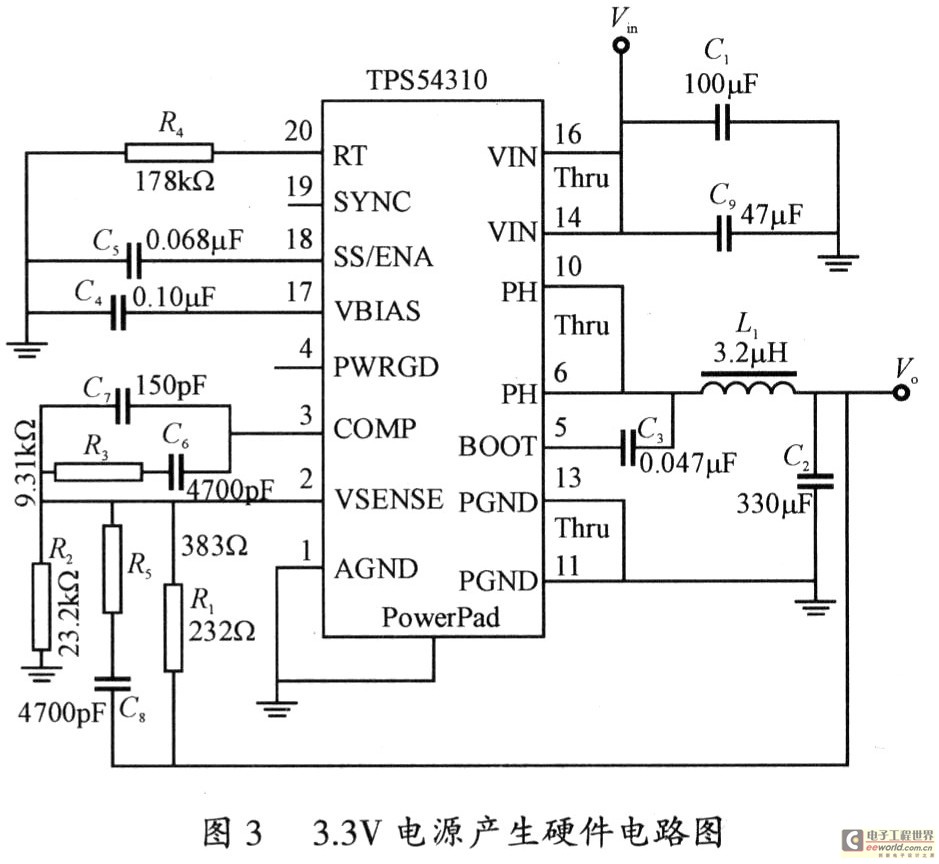

參考SWIFT De signer軟件,設(shè)計(jì)了基于TPS54310的TMS3320DM64xX SOC的三種電源電路,以3.3V I/O電源電路為例(參見圖3),其主要步驟如下。

3.1 選擇轉(zhuǎn)換頻率

由前節(jié)的特性分析可知,轉(zhuǎn)換頻率分為固定和可調(diào)兩種。由于SYNC設(shè)置的固定頻率誤差為±20%,不符合SOC系統(tǒng)的高精度要求,因而選用頻率可調(diào)的方式。

3.2 選擇輸入電容

TPS54310的輸入端需要一個(gè)去耦電容(圖3中的C9)和一個(gè)大電容(圖3中的C1)。去耦電容用于降低器件輸入端的高頻噪聲,選擇陶瓷電容并盡量使之與芯片靠近放置以保證完全起作用;大電容用于降低輸入總線的電壓波動(dòng),如果選擇的去耦電容足夠大(10μF以上),能夠進(jìn)行足夠的濾波,則大電容可以省略。決定是否需要大電容的因素有:

(1)系統(tǒng)輸入電源允許的最大波動(dòng)值(Vrip),為保證正常工作,Vrip卻應(yīng)該低于300mVpp,根據(jù)式(3)有

式中:Vin為沒有大電容時(shí)的實(shí)際最大的峰峰波動(dòng)電壓值;

IOUT(MAX)為最大的直流負(fù)載電流;

fsw為選擇的轉(zhuǎn)換頻率,如果Vin值大于Vrip的值,則需要大電容。

(2)如果加了一個(gè)大電容,該電容能夠降低在高端場(chǎng)效應(yīng)管啟動(dòng)時(shí)間內(nèi)產(chǎn)生的電流脈沖所帶來(lái)的輸入電壓的變化,而流經(jīng)大電容的匹配電阻(ESR)的電壓也會(huì)帶來(lái)波動(dòng),因而要求使用大電容和小匹配電阻。

3.3 選擇輸出濾波器組件

輸出濾波器組件包括輸出電感(圖3中的L1)和輸出電容(圖3中的C2)。選擇輸出電容需要考慮三個(gè)因素:直流額定電壓、額定的波動(dòng)電流和最大的輸出波動(dòng)電壓,其直流額定電壓至少大于輸出電壓的10%。

3.4 選擇補(bǔ)償組件

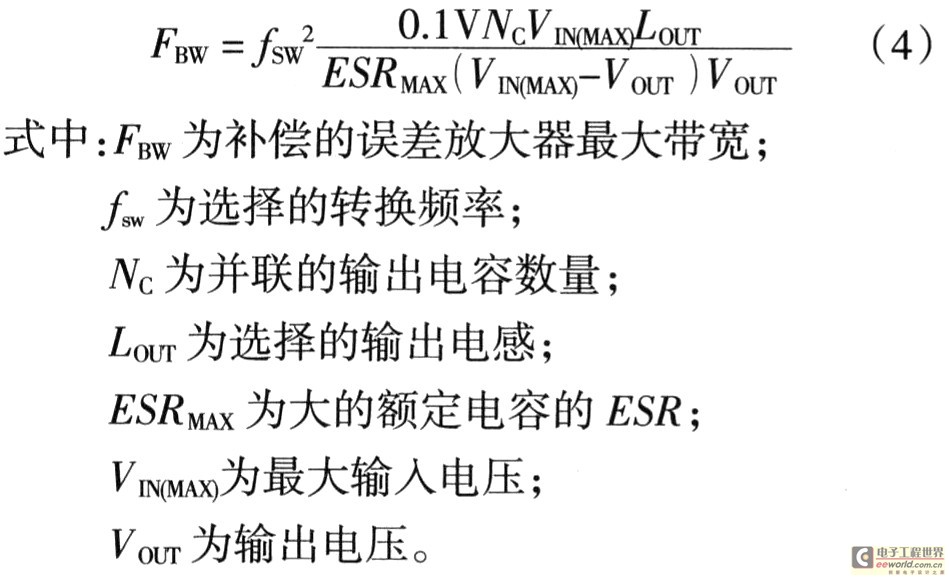

如圖3所示,C7、R3、C6和R5、R1、C8共同構(gòu)成電路補(bǔ)償回路網(wǎng)絡(luò)。當(dāng)設(shè)計(jì)補(bǔ)償時(shí),需要考慮很多因素,首先,根據(jù)式(4)檢測(cè)補(bǔ)償?shù)恼`差放大器允許的最大帶寬,設(shè)計(jì)時(shí)應(yīng)該使實(shí)際的帶寬小于FRW。

然后,根據(jù)式(5)計(jì)算所需的的回路交叉頻率FCO,F(xiàn)BW的值由式(4)得出。

式中:FCO為所需的回路交叉頻率;

LOUT為選擇的輸出電感。

最后計(jì)算R2,C7、R3、C6和R5、R1、C8的值。首先選擇R1和R2的值,這兩個(gè)電阻值決定了輸出電壓的值,因而必須是0.1%精度電阻。R1的范圍在10kΩ到50kΩ之間,然后根據(jù)式(6)計(jì)算出指定輸出的電壓值,再確定R2的值。然后利用式(

關(guān)鍵字:TPS54310 SOC 電源電路設(shè)計(jì)

3.5 選擇慢啟動(dòng)時(shí)間

由式(1)可知,在SS/ENA管腳上連接的電容使啟動(dòng)延遲了16ms。

如圖3所示,Vin為輸入端,Vo為輸出端;R2用于決定輸出電壓的值;100μF的C1和47μF的C9共同構(gòu)成了輸入信號(hào)的去耦合器;C7、R3、C6和R5、R1、C8共同構(gòu)成電路補(bǔ)償回路網(wǎng)絡(luò);L1和C2作為輸出信號(hào)的濾波器;RT引腳接了一個(gè)178kΩ的電阻而SYNC懸空,即內(nèi)部的轉(zhuǎn)換頻率在280kHz到700kHz之間可調(diào),由式(2)可得,

另外,在實(shí)際設(shè)計(jì)中,為了保證輸入信號(hào)的噪聲盡可能小,還應(yīng)該在電源與輸入引腳之間連接一個(gè)LC濾波器。

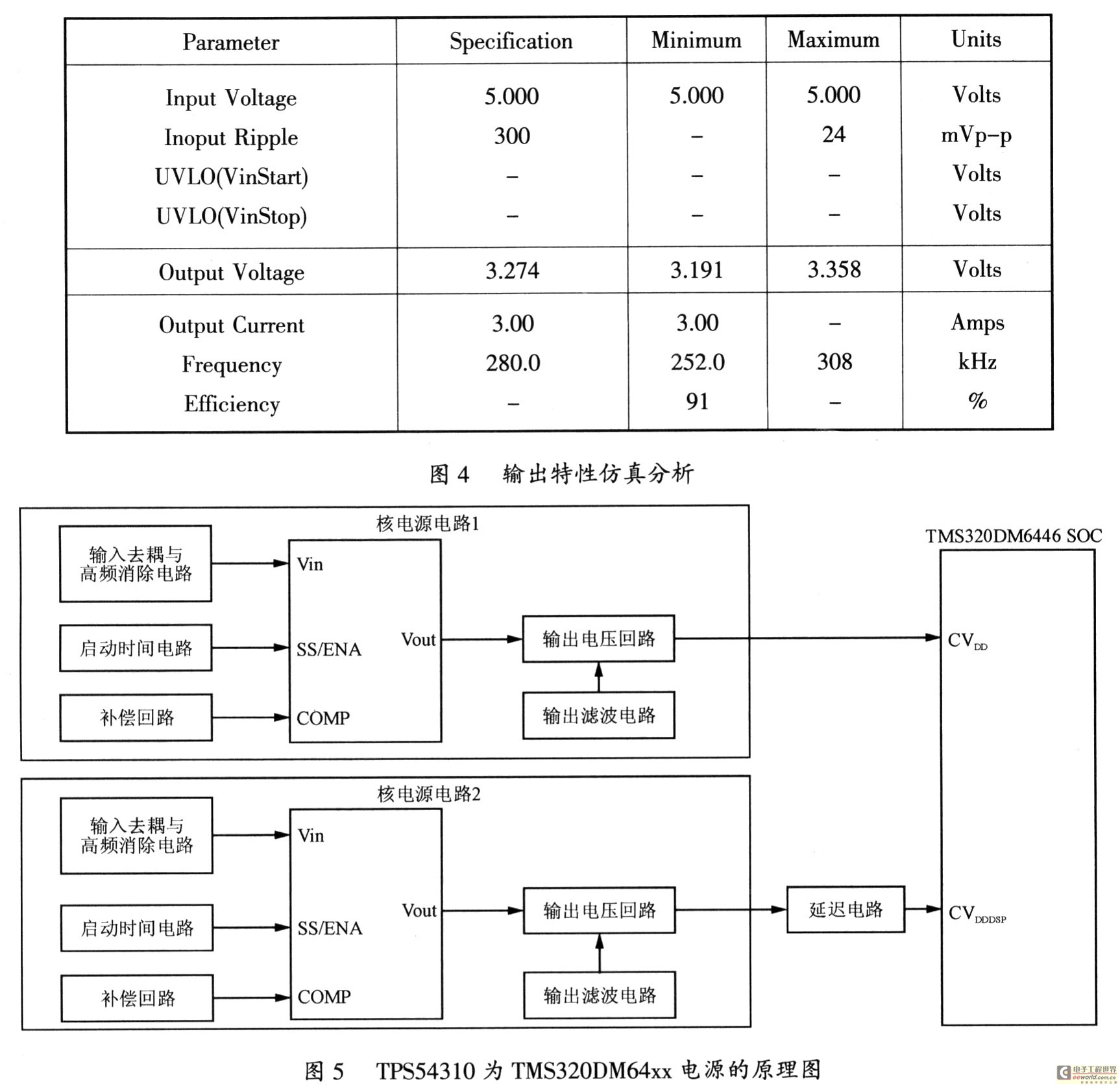

對(duì)芯片的輸出特性進(jìn)行了軟件仿真分析,如圖4所示,當(dāng)設(shè)定輸入電壓為5V,輸出電壓為3.3V,轉(zhuǎn)換頻率為280kHz時(shí),其實(shí)際輸出電壓在3.191V到3.358V之間,最大誤差為3.3%,具有較高的精度和穩(wěn)定度;輸出電流為3A,具有較強(qiáng)的驅(qū)動(dòng)能力;實(shí)際的轉(zhuǎn)換頻率在252kHz到300kHz之間,滿足系統(tǒng)對(duì)電源響應(yīng)速度的要求;功耗與效率相關(guān),效率越高,在負(fù)載功耗一定的情況下,系統(tǒng)總功耗就越低,芯片的最低效率達(dá)到91%,完全滿足系統(tǒng)的低功耗要求。由上述分析可知,該電路工作性能良好。

1.2V電源電路和1.8VI/O電路的產(chǎn)生方法與上述方法相同。通過(guò)核電源與I/O電源產(chǎn)生電路之間加入延遲電路來(lái)保證上電時(shí)序的正確性。圖5顯示的就是以TPS54310為基本核心的多組電路TMS320DM64xx電源的原理圖。

4 結(jié)語(yǔ)

以高性能DC/DC調(diào)節(jié)器TPS54310為核心設(shè)計(jì)的TMS320DM64xx SOC電源電路,能夠提供穩(wěn)定精準(zhǔn)的核電壓和I/O電壓,外部附加簡(jiǎn)單的延時(shí)電路可以保證正確的上電時(shí)序,能夠?yàn)镾OC系統(tǒng)建立可靠的電源電路,正確實(shí)現(xiàn)SOC系統(tǒng)的功能。