在電子測量中,不僅需要對多路信號(hào)進(jìn)行高精度的采集和預(yù)處理,而且要將其快速地傳送到計(jì)算機(jī),以便于對測量的監(jiān)測。文中選用ADS8364來進(jìn)行多通道信號(hào)采集,通過CY7C68013芯片采用USB2.O協(xié)議進(jìn)行數(shù)據(jù)的快速傳輸。

1 多通道,高精度的A/D轉(zhuǎn)換

ADS8364是美國TI公司生產(chǎn)的高速、低功耗,6通道同步采樣16位模數(shù)轉(zhuǎn)換器。ADS8364采用+5 V工作電壓,并帶有80 dB共模抑制的全差分輸入通道以及6個(gè)4μs連續(xù)近似的模數(shù)轉(zhuǎn)換器、6個(gè)差分采樣放大器。

當(dāng)ADS8364采用5 MHz的外部時(shí)鐘來控制轉(zhuǎn)換時(shí),它的取樣率是250 kHz,同時(shí)對應(yīng)于4μs的最大吞吐率,這樣,采樣和轉(zhuǎn)換共需花費(fèi)20個(gè)時(shí)鐘周期。另外,當(dāng)外部時(shí)鐘采用5 MHz時(shí),ADS8364的轉(zhuǎn)換時(shí)間是3.2μs,對應(yīng)的采集時(shí)間是0.8μs。因此,為了得到最大的輸出數(shù)據(jù)率,讀取數(shù)據(jù)可以在下一個(gè)轉(zhuǎn)換期間進(jìn)行。

ADS8364中的采樣/保持模塊以最大吞吐率250 kB工作,它的輸入帶寬大于ADC的奈奎斯特頻率。而典型的小信號(hào)帶寬是300 MHz。孔徑延遲時(shí)間為5 ns,每次的平均增量為5 ops。這些特性反映了ADS8364接收輸人信號(hào)的能力。

1.1 A/D前端信號(hào)調(diào)理電路

鑒于多通道信號(hào)采集的時(shí)序的重要性,這里選用差分放大電路對信號(hào)進(jìn)行調(diào)理。

采用TI公司的運(yùn)算放大器OPA2227組成一個(gè)電壓放大器,將輸入電壓轉(zhuǎn)換到ADS8364的差分輸入電壓范圍。根據(jù)需要,可以通過調(diào)整放大電路中電阻的大小,改變輸入電壓的范圍,其對應(yīng)的參數(shù)表如表1所示。

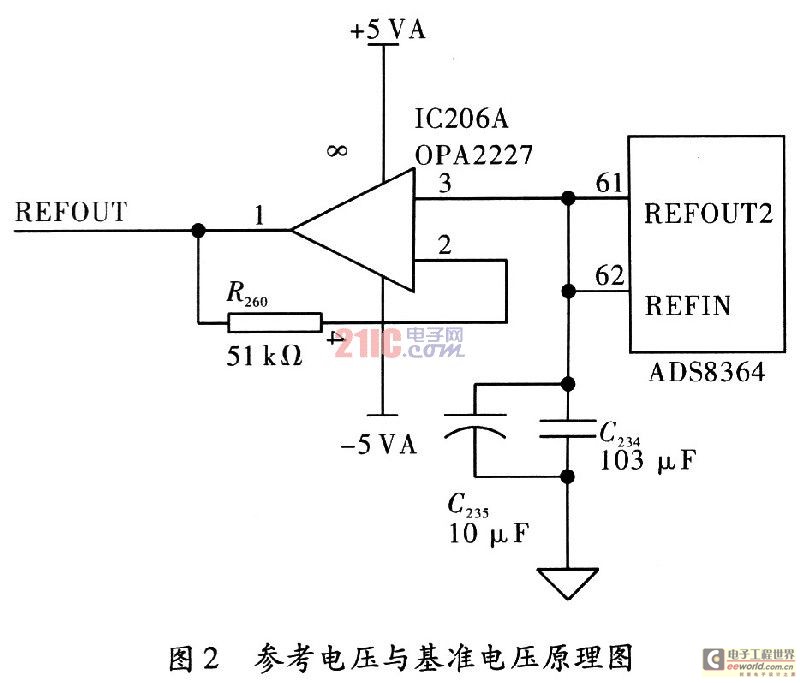

ADS8364在參考電壓為2.5 V的情況下,其測量范圍為±1.25 V。而實(shí)際中的測試信號(hào)一般為±2.5 V,±5 V或±lO V,所以,在ADS8364的前端,要經(jīng)過線性衰減、限幅和濾波。其調(diào)理電路原理圖,如圖1所示。

1.2 A/D電源電路

數(shù)據(jù)采集電路需要完成高精度的數(shù)據(jù)采集,因此電源部分的設(shè)計(jì)是相對比較重要的。

在作進(jìn)一步的分析之前,需要說明采樣精度和有效位都是對采樣質(zhì)量高低的描述。設(shè)采樣精度為vp,有效位為N,基準(zhǔn)電壓為vREF,基準(zhǔn)電壓噪聲電平為VN,則有

2 USB接口模塊設(shè)計(jì)

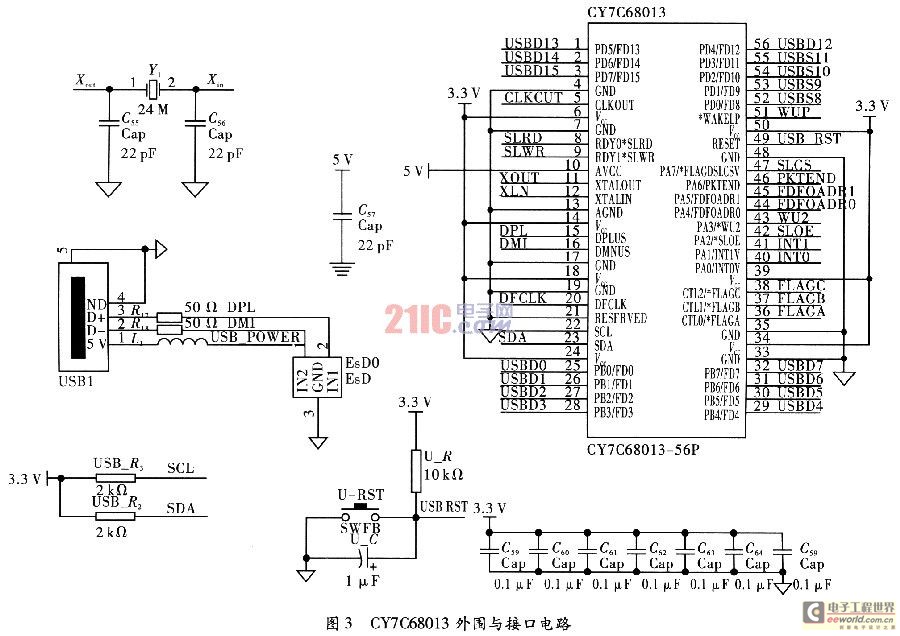

Cypress Semiconductor公司的EZ-USB FX2是世界上的第一款集成USB2.0的微處理器,它集成了USB2.0收發(fā)器、SIE(串行接口引擎)、增強(qiáng)型8051微控制器和可編程的外圍接口。FX2這種獨(dú)創(chuàng)性結(jié)構(gòu)可使數(shù)據(jù)傳輸率達(dá)到56 MB·s-1,即USB2.0允許的最大帶寬。EZ-USB FX2 CY7C68013的微處理器是一個(gè)增強(qiáng)型的805l內(nèi)核,性能可達(dá)標(biāo)準(zhǔn)8051的5~10倍,并與標(biāo)準(zhǔn)805l的指令完全兼容。增強(qiáng)型的8051內(nèi)核使用RAM芯片作程序指令和數(shù)據(jù)存儲(chǔ)器,從而使得EZ-USB FX2 CY7C68013具有“軟”特性,也就是說,可以通過自行編寫程序指令來實(shí)現(xiàn)所需的功能。

由于USB通信是本系統(tǒng)設(shè)計(jì)主要的任務(wù)目標(biāo),所以在設(shè)計(jì)時(shí)也充分考慮到系統(tǒng)的可擴(kuò)展性,所有的信號(hào)引腳都有排線引出,方便了測試和擴(kuò)展。

3 FPGA邏輯電路

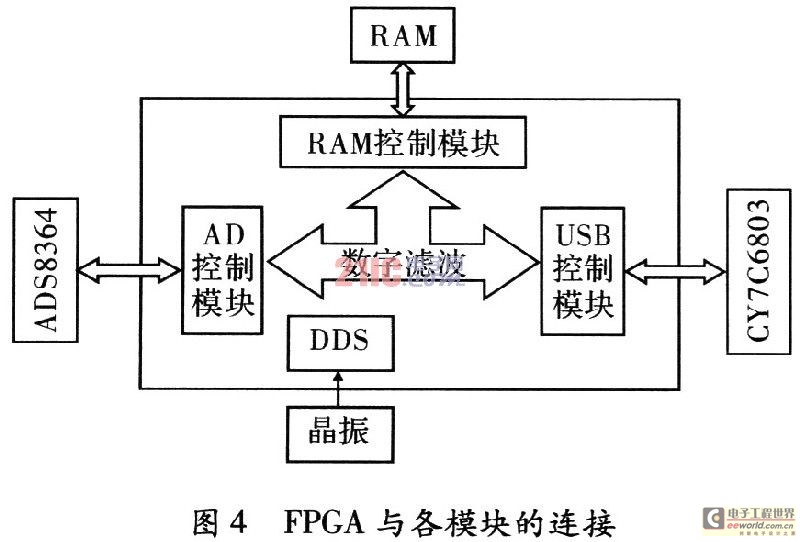

圖4為采集傳輸系統(tǒng)中FPGA與各模塊的連接。

整個(gè)電路選用Altera公司推出的新一代低成本的Cyclone系列FPGA器件EPlC6Q240作為控制和信號(hào)處理芯片。EPlC6Q240型FPGA芯片具有強(qiáng)大的硬件邏輯功能,總邏輯單元達(dá)5 980個(gè),有I/O引腳181個(gè),92 160位的內(nèi)部存儲(chǔ)單元,20個(gè)RAM單元,2個(gè)鎖相環(huán)。利用這些強(qiáng)大的功能,可以很容易進(jìn)行模塊控制和數(shù)據(jù)動(dòng)態(tài)濾波。如圖4所示,通過FPGA對A/D進(jìn)行采樣控制,將A/D采樣的數(shù)據(jù)進(jìn)行數(shù)字濾波后傳送到RAM中進(jìn)行,或是直接通過USB模塊將數(shù)據(jù)床送到電腦中進(jìn)行處理。

采用VerilogHDL硬件語言編程來對A/D采集,RAM傳輸,USB傳輸?shù)冗M(jìn)行控制信號(hào)輸出,并對采樣的數(shù)據(jù)進(jìn)行數(shù)字濾波。

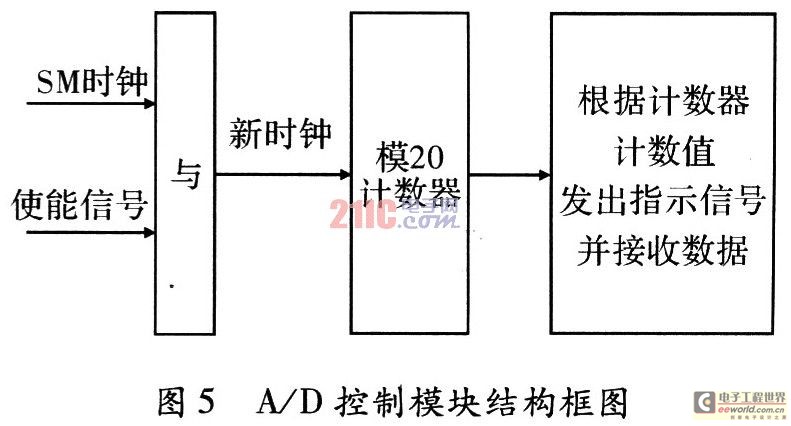

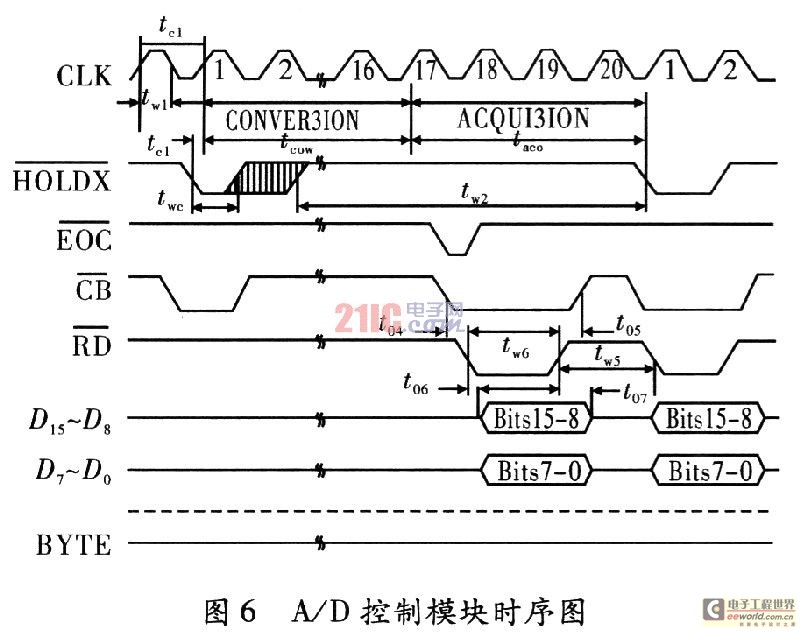

A/D數(shù)據(jù)接口模塊實(shí)現(xiàn)對ADS8364數(shù)據(jù)的采樣,采樣后的數(shù)據(jù)進(jìn)行濾波處理。本模塊對ADS8364的控制引腳有:

(1)模擬采樣通道控制信號(hào)為/HOLDA,/HOLDB,/HOLDC;

(2)數(shù)據(jù)輸出模式以及通道選擇信號(hào)為A0,A1和A2;

(3)讀控制信號(hào)為/RD。

首先將5 MHz時(shí)鐘和使能信號(hào)相與產(chǎn)生新時(shí)鐘,使用該時(shí)鐘驅(qū)動(dòng)一個(gè)20個(gè)狀態(tài)的狀態(tài)機(jī)。在計(jì)數(shù)器值為15時(shí)將HOLDa,HOLDb,HOLDc置0,啟動(dòng)一次數(shù)據(jù)采樣。在計(jì)數(shù)值為2~3,4~5,6~7,8~9,10~ll,12~13且相應(yīng)的通道得到使能時(shí),分別發(fā)出通道l至通道6的通道地址。在計(jì)數(shù)值為3,5,7,9,ll,13時(shí)發(fā)出讀信號(hào)讀取相應(yīng)通道的數(shù)據(jù)。在計(jì)數(shù)值為15時(shí)發(fā)出采樣完畢信號(hào),指示6通道數(shù)據(jù)已經(jīng)采集完畢。

USB控制電路分兩個(gè)模塊完成。模塊1實(shí)現(xiàn)主機(jī)向FPGA寄存器單元的配置,模塊2實(shí)現(xiàn)FPGA向主機(jī)的數(shù)據(jù)包輸出。

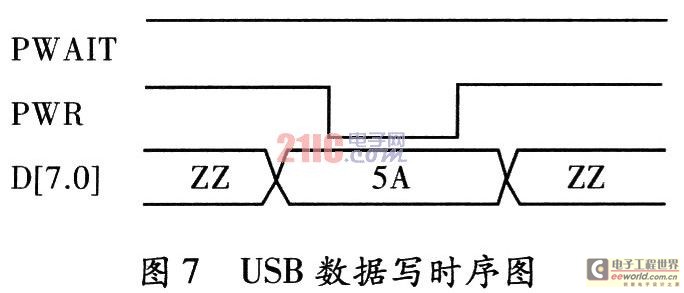

模塊1實(shí)現(xiàn)在地址IO模式下向寄存器寫數(shù)據(jù)。寫時(shí)序如圖7所示。可以根據(jù)地址線和PWR信號(hào)實(shí)現(xiàn)對某寄存器的寫控制。

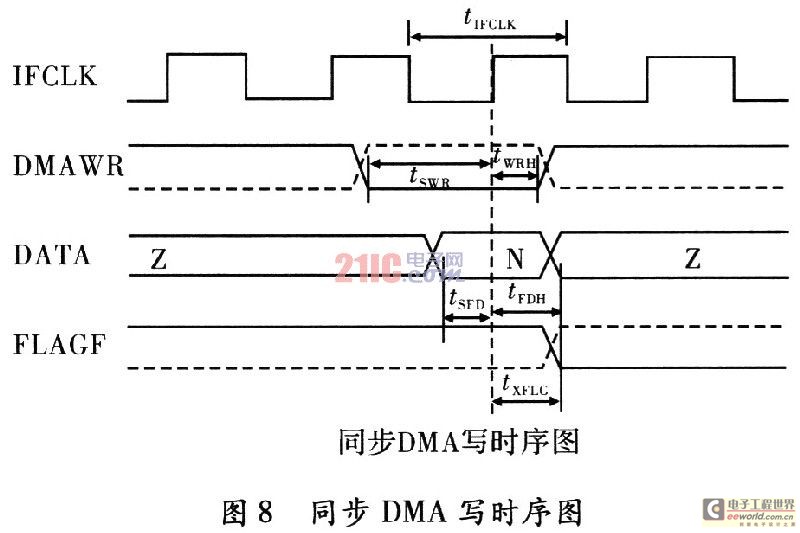

模塊2實(shí)現(xiàn)在DMA模式下FPGA向主機(jī)的批量數(shù)據(jù)傳輸。同步DMA的時(shí)序圖如圖8所示(時(shí)鐘由FPGA提供)。

本系統(tǒng)使用一個(gè)狀態(tài)機(jī)實(shí)現(xiàn)該功能,狀態(tài)機(jī)在“查找”和“傳輸”兩個(gè)狀態(tài)之間切換。系統(tǒng)啟動(dòng)以后首先進(jìn)入查詢FIFO的狀態(tài),在查詢到FIFO中的數(shù)據(jù)量大于一個(gè)USB數(shù)據(jù)包(2 040 bit)時(shí),狀態(tài)機(jī)進(jìn)入到“傳輸”狀態(tài)。在“傳輸”狀態(tài)下,按照上述同步。DMA寫時(shí)序,首先傳輸6 bit包頭,然后傳輸2 040 bit數(shù)據(jù),最后傳輸2 bit數(shù)據(jù)校驗(yàn)。在數(shù)據(jù)傳輸?shù)倪^程中,電路要一直查詢DMAING的狀態(tài),檢測到:DMAING為低時(shí)要暫停數(shù)據(jù)傳輸。在傳輸完2 kB數(shù)據(jù)后,狀態(tài)機(jī)再轉(zhuǎn)入到“查詢”狀態(tài),進(jìn)行下一輪數(shù)據(jù)傳輸狀態(tài)。

系統(tǒng)當(dāng)前的工作時(shí)鐘為20 MHz,在USB接口處可以達(dá)到的最大帶寬約為10 MB,系統(tǒng)分頻給A/D的時(shí)鐘為5 MHz,這樣可以保證A/D接口的最大帶寬達(dá)到3 MB。在Flash接口處的帶寬約為5 MB。將時(shí)鐘速度提升l倍,則USB口的傳輸能力可以達(dá)到約20 MB。

數(shù)據(jù)處理與儲(chǔ)存模塊主要是FPGA將高速A/D采集到的數(shù)據(jù)進(jìn)行打包、暫存。本套電路中使用了一片由,TI公司生產(chǎn)的高速靜態(tài)RAM IS61-LV51216作為數(shù)據(jù)暫存器件;由FPGA對這片RAM存儲(chǔ)器進(jìn)行監(jiān)控。

4 結(jié)束語

采用USB協(xié)議的數(shù)據(jù)采集卡可以滿足對數(shù)據(jù)進(jìn)行多通道的高精度采集、處理和傳輸,在數(shù)據(jù)有效采集的情況下,擺脫了對端口的依賴。