1 引言

隨著集成電路規(guī)模的發(fā)展, 電子設(shè)備的體積、重量和功耗" title="功耗">功耗越來越小, 這對電源電路的集成化、小型化及電源管理性能提出了越來越高的要求。而隨著片上系統(tǒng)( SOC) 的不斷發(fā)展, 單片集成的LDO" title="LDO">LDO 線性穩(wěn)壓" title="線性穩(wěn)壓">線性穩(wěn)壓器的應(yīng)用也越來越廣泛[1]。對于片內(nèi)的LDO,最擔(dān)心的是寄生電容過大引起不穩(wěn)定,論文針對片內(nèi)應(yīng)用而設(shè)計(jì)的這款LDO,能保證在uF 級別的寄生電容范圍內(nèi)都可以正常工作,畢竟寄生電容再大也不至于是μF 級別的。功耗是LDO 線性穩(wěn)壓器的重要指標(biāo)之一,一般的LDO 功耗都在幾十μA 以上,例如文獻(xiàn)[2]中電路的靜態(tài)電流為38μA,文獻(xiàn)[3]中靜態(tài)功耗高達(dá)65μA, 而本文的靜態(tài)功耗做到10μA 左右,不僅功耗低,本文中第二級靠電阻的電流關(guān)系提供了一個小增益級,并且提高了整個LDO的帶寬。

2 LDO電路組成原理與關(guān)鍵模塊設(shè)計(jì)

2.1 電路基本工作原理

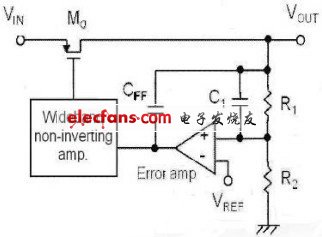

圖1 是LDO 線性穩(wěn)壓器的結(jié)構(gòu)框圖, 由下面幾個部分組成:基準(zhǔn)電壓源(Vref)、誤差放大器、同相放大器、反饋電阻網(wǎng)絡(luò)、調(diào)整管等。其中基準(zhǔn)電壓源輸出參考電壓Vref, 要求它精度高, 溫漂小。誤差放大器將輸出反饋回來的電壓與基準(zhǔn)電壓Vref 進(jìn)行比較, 并放大其差值,其經(jīng)過同相放大器來控制調(diào)整功率管的狀態(tài), 因而使輸出穩(wěn)定。在這里C1 是前饋電容,可以提高負(fù)載調(diào)整率,并增加了一個左零點(diǎn)補(bǔ)償,Cff提供一個零點(diǎn)補(bǔ)償。第一級放大器就是一個差分對,和大多數(shù)誤差放大器結(jié)構(gòu)一樣,第二級為同相放大級,靠電阻的電流關(guān)系提供一個小增益級,并控制帶寬。相對于普通結(jié)構(gòu)而言的,如果靠運(yùn)放直接驅(qū)動功率管,那帶寬就被功率管的寄生電容和運(yùn)放輸出阻抗和增益決定了,而這個結(jié)構(gòu)的增益和輸出阻抗,相比運(yùn)放小很多,帶寬自然就提高很多。表1 為該LDO 的主要設(shè)計(jì)參數(shù)和性能指標(biāo)。

圖1 LDO 線性穩(wěn)壓器結(jié)構(gòu)示意圖

表1 LDO 的設(shè)計(jì)參數(shù)和性能指標(biāo)

2.2 電路組成與設(shè)計(jì)

(1)調(diào)整管結(jié)構(gòu)設(shè)計(jì):MOS 型線性穩(wěn)壓器的調(diào)整管是電壓驅(qū)動的, 能大大降低器件消耗的靜態(tài)電流, 而且其較小的導(dǎo)通阻抗使得漏失電壓也比較低,從而提高了電源的轉(zhuǎn)換效率[4]。根據(jù)調(diào)整管的平方率關(guān)系式以及設(shè)計(jì)指標(biāo)Vdropout ≈ 200mV,可以計(jì)算出調(diào)整管的寬長比, 結(jié)合調(diào)整管的柵極寄生電容以及工藝的要求,在重載情況下考慮調(diào)整管需工作在線性區(qū), 將調(diào)整管的寬長設(shè)計(jì)為:W=6000μm,L=0.5μm。

(2)電阻R1 與R2 選擇:輸出電壓由反饋網(wǎng)絡(luò)決定,根據(jù)VOUT =VREF[(R1+R2)/R1],當(dāng)選定的VREF=1.25V,R1 = 625KΩ,那么R2 = 625KΩ。

2.3 誤差放大器(EA)設(shè)計(jì)

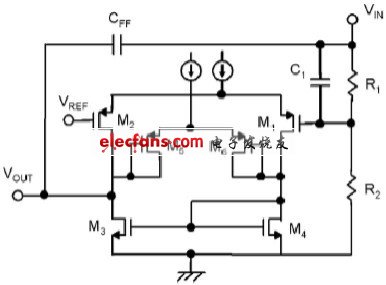

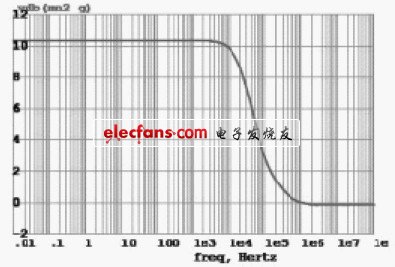

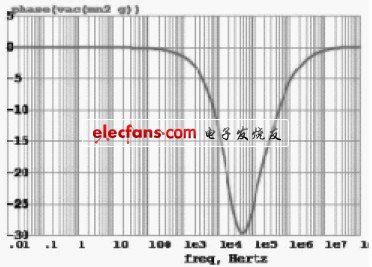

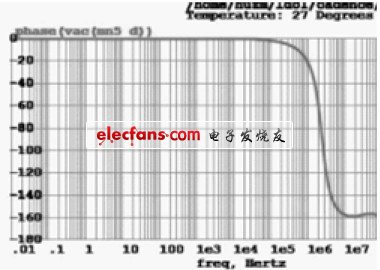

誤差放大器電路原理圖如圖2 所示。對該EA部分功耗(3μA)以及低的失調(diào)電壓的要求,根據(jù)σ2(VT)= A2VT / WL+S2VTD2以及MOS 管的平方率關(guān)系[5],設(shè)計(jì)出各MOS 管的尺寸,M1 和M2 的寬長比為41/2, M3 和M4 的寬長比為4/1,M5 和M6 的寬長比為2/1, 我們這里取W1=W2=82μm,L1=L2=4μm;W3=W4=12μm,L3=L4=3μm;W5=W6=8μm,L5=L6=4μm。實(shí)際上,在EA 這部分為了讓這一級增益Ger 不小于10dB 且保證有足夠的相位裕度,將反饋電容CFF設(shè)計(jì)為20.8pF,把C1 設(shè)計(jì)為1.5pF。該部分的仿真結(jié)果如圖3 所示。結(jié)果表明,該設(shè)計(jì)在保證穩(wěn)定的前提下Ger 為11dB[6]。

圖2 EA 與反饋網(wǎng)絡(luò)

圖3 EA 的環(huán)路增益

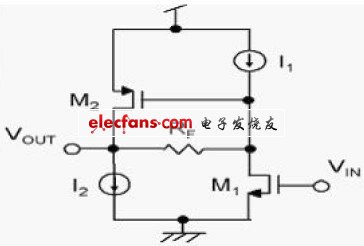

2.4 同相放大器設(shè)計(jì)

同相放大器電路結(jié)構(gòu)如圖4 所示。這一級主要是獲得整個環(huán)路最大的增益Gnon- inv=25dB~30dB。

圖4 同相放大器結(jié)構(gòu)為保證低功耗的前提下I1設(shè)為5μA,I2設(shè)為3μA,在小的偏置電流以及較大的負(fù)載的情況下為了保證能得到不小于25dB 的增益,把RF設(shè)計(jì)為500K。由于同相放大器的增益隨負(fù)載的增加而減小,在設(shè)計(jì)中需要適當(dāng)增加偏置電流I1 和增加RF的值[7]。而帶寬受M2 的跨導(dǎo)和調(diào)整管的W/L 的影響,需要增加M2 的W/L 以及偏置電流I2。圖中M1 的寬長比為4/1, 這里取W1=30μm,L1=3μm,M2 的寬長比為110/1,取W2=110μm,L2=1μm。仿真結(jié)果如圖5 所示。

圖5 同相放大器的增益3 LDO 整體仿真結(jié)果與討論

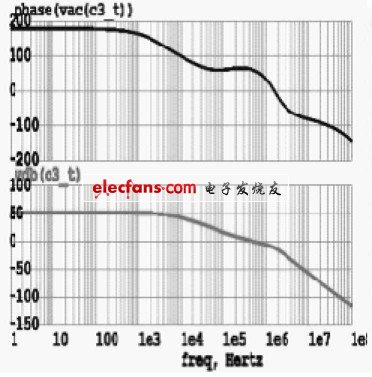

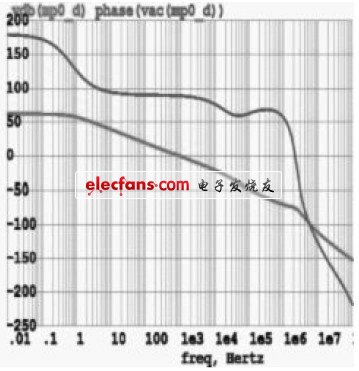

我們基于HHNEC 0.35um BCD 工藝下,采用cadence 和Hspice 仿真軟件對整體電路做仿真,如圖6 所示為LDO 環(huán)路穩(wěn)定性仿真曲線。

(a)負(fù)載電流為50mA 仿真曲線

(b)負(fù)載電流為0 時仿真曲線

圖6 LDO 環(huán)路穩(wěn)定性仿真曲線

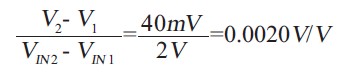

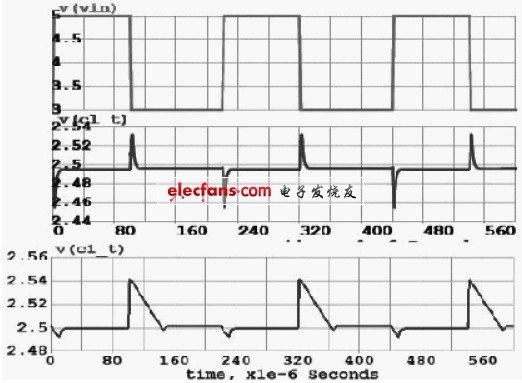

(a) 圖為負(fù)載電流為50mA 時,LDO 環(huán)路增益為50dB、單位增益帶寬為470KHZ、相位裕度為74degree。(b)圖為負(fù)載電流為0 時,LDO 環(huán)路增益為63dB、單位增益帶寬為1KHZ、相位裕度為87degree。圖7 給出了該LDO 的線性調(diào)整率曲線,仿真條件為C L=1μF, 由仿真曲線可以看出該LDO 的線性調(diào)整率為:

圖7 CL=1μF 線性調(diào)整率曲線

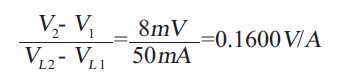

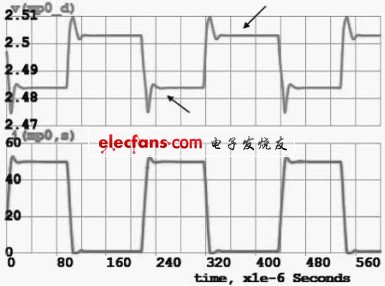

圖8 給出了該LDO 的負(fù)載調(diào)整率曲線,仿真條件為CL=1μF, 由仿真曲線可以看出該LDO 的負(fù)載調(diào)整率為:

圖8 CL=1μF 負(fù)載調(diào)整率曲線

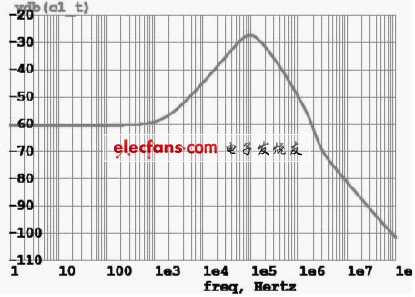

圖9 給出了該LDO 的電源抑制比仿真曲線,仿真條件為IL=1mA。從該曲線可以看出,該LDO 的PSRR 在1KHZ時為- 60dB。

圖9 電源抑制比仿真曲線

4 結(jié)論

本文提出的這款LDO 線性穩(wěn)壓器,能保證在μF 級別的寄生電容范圍內(nèi)都可以正常工作。

該LDO 的靜態(tài)電流低至10μA,文中同相放大器的引入,提高了整個LDO 的帶寬。從仿真結(jié)果可以看出,在負(fù)載電流Iload=50mA 時,帶寬為470KHz。

該LDO 其它各方面指標(biāo)都滿足設(shè)計(jì)要求。