低壓降穩(wěn)壓器(LDO)主要用于產(chǎn)生供音頻和射頻電路使用的低紋波、低噪聲電源,也可以作為頻率合成器和VCO的局部純凈電源。一般情況下,LDO的輸入是在直流電壓上疊加了寬帶交流紋波的電源電壓。流經(jīng)電池和連接器阻抗的電流變化所引起的電氣噪聲就是其中一種寬帶交流紋波。LDO可用來全面抑制這些寄生信號。LDO的輸入端還可連接交換式穩(wěn)壓器的輸出,以提供純凈、低噪聲的輸出電壓,在這種應(yīng)用中,LDO必須能夠應(yīng)付從100kHz到3MHz以上的開關(guān)頻率。

首先,可將LDO穩(wěn)壓器視為一個具有開關(guān)功能的低損耗、緊湊型多節(jié)低通濾波器。然而,這種模型存在不少局限性,特別是抑制輸入端寬帶紋波的能力。假設(shè)工作電流小于250μA(對于合理的效率而言),IC設(shè)計師可以在低靜態(tài)電流引起的增益帶寬極限內(nèi)優(yōu)化一些主要性能,如噪聲、調(diào)節(jié)和電源抑制比等。進一步的性能改進需要采取其它一些措施。

當(dāng)需要高性能電源時,設(shè)計師應(yīng)從向穩(wěn)壓器中增添盡可能多的功能開始。以下將以輸出噪聲為9μVrms、電源抑制比在10kHz時為80dB的AS1358-9組件為例,說明LDO設(shè)計實例。

電源抑制

在實際應(yīng)用中,非理想的組件和寄生電容會改變線性穩(wěn)壓器的理想抑制特性。圖1顯示了改變或降低電路抑制能力的一些顯著缺陷。

圖1:P信道LDO顯示了簡化的寄生高頻通道

線性調(diào)節(jié)率

LDO數(shù)據(jù)手冊中有兩個指標(biāo)用于描述LDO抑制輸入電壓噪聲等的能力,分別是線性調(diào)節(jié)率和電源抑制比(PSRR)。雖然它們看起來非常相似,但其中一個指標(biāo)反映的是直流變化,另一個指針反映的是交流性能。

線性調(diào)節(jié)率代表了LDO抑制輸入電壓變化的能力。以下式表示:

在實際應(yīng)用中,線性調(diào)節(jié)率可被視為穩(wěn)壓器輸出電壓VOUT隨每伏特輸入電壓Vin變化的百分比,當(dāng)同樣的穩(wěn)壓器具有各種輸出電壓微調(diào)功能時這一點特別有用。

線性調(diào)節(jié)率是一個穩(wěn)態(tài)直流參數(shù),主要由零頻率點上穩(wěn)壓器的開環(huán)增益所決定。

電源抑制比

這個指標(biāo)衡量的是穩(wěn)壓器抑制疊加在正常輸入直流電壓上的交流信號的能力。

電源抑制比在低頻時最大,依照實際穩(wěn)壓器設(shè)計,從1kHz到10kHz范圍內(nèi)開始下降。圖2為AS1358-9 150mA/300mA低噪聲、高電源抑制比LDO的典型PSRR特性。該組件在100kHz時仍具有60dB的良好PSRR值。

圖2:AS1358-9組件的電源抑制比。

圖2所示的曲線,是由取決于感興趣頻率的眾多主導(dǎo)影響共同形成的。在直流與接近100Hz到1kHz區(qū)間內(nèi),抑制效果取決于帶隙基準(zhǔn)和穩(wěn)壓器誤差信號放大器的開環(huán)增益。而在該區(qū)間之上直到約100kHz,抑制效果主要取決于誤差信號放大器的開環(huán)增益。但在100kHz以上時,電源抑制比主要受輸出電容、寄生組件以及調(diào)整管上的任何漏電流及封裝影響。圖1標(biāo)示了這些組件。

如果對100kHz以上頻率有額外的電源抑制要求(通常也是需要的),那么在輸入端必須連接一個外部的預(yù)濾波網(wǎng)絡(luò)來增強LDO的抑制性能。

外部網(wǎng)絡(luò)

在實際應(yīng)用中,只有兩種預(yù)濾波方法值得考慮,這是因為必須防止在額外的組件上產(chǎn)生過多功耗,同時要保持穩(wěn)壓器的穩(wěn)定性。

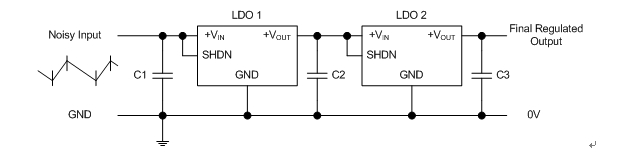

圖3:串聯(lián)LDO可產(chǎn)生很高的PSRR

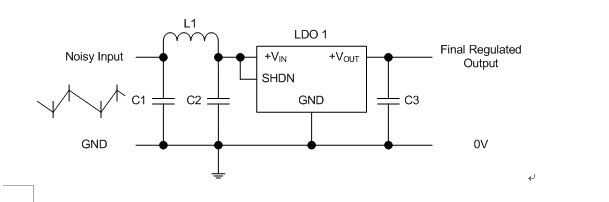

圖4:外部輸入網(wǎng)絡(luò)可提供額外的抑制性能

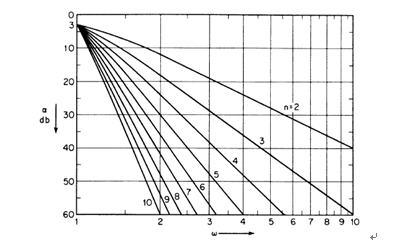

三極點巴特沃斯特性需要串聯(lián)低值線圈和兩個電容,其中一個電容通常位于LDO輸入端。三極點巴特沃斯響應(yīng)在4.5Fo處可提供額外40dB的抑制,其中Fo是-3dB點(見圖5)。

圖5:不同階數(shù)N下的巴特沃斯阻帶衰減。

相較方法1,額外的濾波器網(wǎng)絡(luò)不會增加顯著的直流阻抗損耗。不過設(shè)計時要特別小心,確保所選電感能夠支持要求的直流電流而不至于飽和。巴特沃斯是很有用的特性,其中的通帶特別平坦,這點與切比雪夫特性不同,后者為了獲得更好的衰減率會犧牲通帶和阻帶紋波。圖7顯示級數(shù)在2和10之間的巴特沃斯濾波器衰減特性。

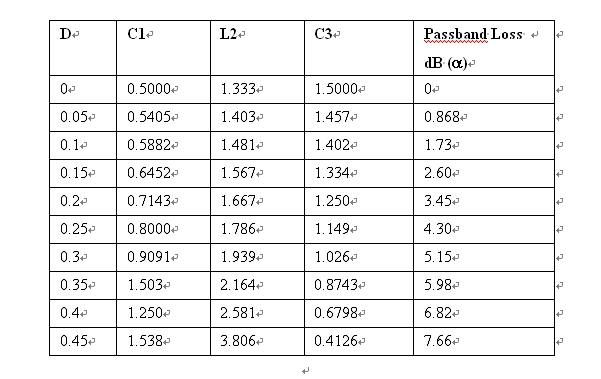

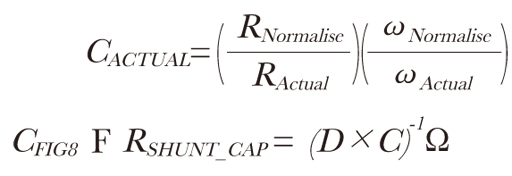

圖6提出了歸一化到1Ω源阻抗和1rad/s頻率下的元件值。注意,濾波器輸出端并未端接終端電阻,這將允許將其連接到線性穩(wěn)壓器的高輸入阻抗上。D欄包含了由非理想元件引起的損耗,并標(biāo)示了通帶損耗。對電源濾波來說,不必嚴(yán)格地符合巴特沃斯特性;畢竟濾波器在直流點只有很小的損耗。

圖6a:歸一化到1Ω和1rad/s的三極點巴特沃斯統(tǒng)一耗散值。

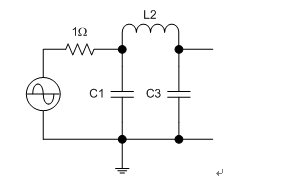

圖6b:三極點巴特沃斯統(tǒng)一耗散濾波器。

下列表達式用于去歸一化圖8a中的值:

針對電源應(yīng)用,選擇的實際源阻抗為RACTUAL=0.1Ω。如果C2固定為1μF(AS1358-9),那么必須反復(fù)選擇w和a直到接近商用元件值為止。通帶損耗不是主要問題,而額外的交流衰減在這個應(yīng)用中非常重要。

假設(shè)C3=1μF,F(xiàn)-3dB=1MHz(Calc 1.082),RACTUAL=0.1Ω,那么C1=1.5μF(Calc 1.47),L2=38nH(D=0.4,a=6.82dB)。合適的線圈可從Coilcraft公司的Mini Spring系列(B09TJLC)或Midi Spring系列(1812SMS-39NJLC)這類中挑選。只要陶瓷電容(C1&C3)的寄生電感小于1nH,濾波器就有足夠的衰減值。

本文小結(jié)

AS1358-9 LDO具有良好的噪聲和電源抑制性能。只要在輸入端增加一個簡單的LC網(wǎng)絡(luò),即可實現(xiàn)額外的高頻電源抑制比性能。