0 引言

近年來(lái),DSP技術(shù)發(fā)展迅速,越來(lái)越多的工程技術(shù)人員開(kāi)始采用DSP進(jìn)行系統(tǒng)設(shè)計(jì)。TI公司的TMS320F28335具有運(yùn)算速度快、功耗小和性價(jià)比高的特點(diǎn),在個(gè)人通信、信號(hào)與信息處理及自動(dòng)控制等領(lǐng)域得到了廣泛應(yīng)用。該芯片配備了兩個(gè)多通道緩沖串口(Multi-channel Buff-ered Serial Port,McBSP),為設(shè)計(jì)串行模數(shù)接口提供了極大的便利。它與串行A/D轉(zhuǎn)換器構(gòu)成的信號(hào)采集與處理系統(tǒng)具有硬件設(shè)計(jì)簡(jiǎn)單、可靠性好的特點(diǎn)。本文將闡述TMS320F28335與ADS7863的接口設(shè)計(jì)。

1 TMS320F28335 McBSP

1.1 TMS320F28335 McBSP的特點(diǎn)

TMS320F28335是一款高性能、多功能、高性價(jià)比32位浮點(diǎn)DSP。該器件最高可在150 MHz主頻下工作,片上集成豐富的外設(shè),其中包括兩個(gè)多通道緩沖串口(McBSP)。McBSP是一種同步串行接口,除具有一般DSP串口功能之外,還可以支持T1/E1,ST-BUS,SPI等不同標(biāo)準(zhǔn)。它的主要特點(diǎn)如下:全雙工串行通信;允許獨(dú)立數(shù)據(jù)流的雙倍發(fā)送緩沖和三倍接收緩沖數(shù)據(jù)存儲(chǔ)器;獨(dú)立的接收、發(fā)送幀和時(shí)鐘信號(hào);發(fā)送和接收通道數(shù)最多可達(dá)128路;多通道選擇模式,允許或阻止每個(gè)通道的傳輸;兩個(gè)16級(jí),32位的FIFO代替DMA;可直接與工業(yè)標(biāo)準(zhǔn)的編碼器、模擬界面芯片(AICs)、其他串行A/D,D/A器件連接;支持時(shí)鐘信號(hào)和幀同步信號(hào)的外部生成;用來(lái)內(nèi)部生成和控制幀同步信號(hào)的可編程采樣率發(fā)生器;可編程的內(nèi)部時(shí)鐘和幀同步信號(hào)生成;可編程的幀同步和數(shù)據(jù)時(shí)鐘極性;可選的數(shù)據(jù)寬度:8 b,12 b,16 b,20 b,24 b或32 b;比特?cái)?shù)據(jù)傳輸時(shí)可選擇高位或低位在先;用于數(shù)據(jù)壓縮的μ律和A律壓縮擴(kuò)展。

1.2 TMS320F28335 McBSP的工作過(guò)程

TMS320F28335的McBSP包括7個(gè)引腳,分別是串行數(shù)據(jù)發(fā)送信號(hào)DX,串行數(shù)據(jù)接收信號(hào)DR,發(fā)送時(shí)鐘信號(hào)CLKX,接收時(shí)鐘信號(hào)CLKR,發(fā)送幀同步信號(hào)FSX、接收幀同步信號(hào)FSR和外部輸入時(shí)鐘信號(hào)CLKS。McBSP通過(guò)這7個(gè)管腳為外部設(shè)備提供了數(shù)據(jù)通道和控制通道。

McBSP通過(guò)DX和DR實(shí)現(xiàn)DSP與外部設(shè)備的通信和數(shù)據(jù)交換。其中,DX完成數(shù)據(jù)發(fā)送,DR完成數(shù)據(jù)接收。控制信息通過(guò)CLKX,CLKR,F(xiàn)SX和FSR以時(shí)鐘和幀同步的形式進(jìn)行通信。由于McBSP內(nèi)有一個(gè)可編程的采樣和幀同步時(shí)鐘發(fā)生器,所以這些時(shí)鐘和幀同步信號(hào)既可以由內(nèi)部產(chǎn)生,也可以由外部輸入。

McBSP發(fā)送數(shù)據(jù)的過(guò)程如下:首先將要發(fā)送的數(shù)據(jù)寫(xiě)入數(shù)據(jù)發(fā)送寄存器DXR[1,2],如果發(fā)送移位寄存器XSR[1,2]中沒(méi)有數(shù)據(jù),則DXR[1,2]中的值先復(fù)制到XSR[1,2],再由XSR[1,2]將數(shù)據(jù)移到DX上發(fā)送;如果XSR[1,2]不為空,則等待將XSR[1,2]中的數(shù)據(jù)全部移出到DX腳發(fā)送后才將DXR[1,2]中的值復(fù)制到XSR[1,2],再由DX腳將數(shù)據(jù)發(fā)送出去。

McBSP接收數(shù)據(jù)的過(guò)程如下:DR腳上接收的數(shù)據(jù)首先移入接收移位寄存器RSR[1,2],一旦收到一個(gè)字(可以是8 b,12 b,16 b,24 b或32 b),檢查接收緩沖寄存器RBR[1,2]是否為空,如果為空,則將RSR[1,2]中的數(shù)據(jù)復(fù)制到RBR[1,2],接著,數(shù)據(jù)被復(fù)制到數(shù)據(jù)接收寄存器DRR[1,2],CPU通過(guò)讀取DRR[1,2]中的數(shù)據(jù)完成數(shù)據(jù)接收。需要注意的是,DRR2,RBR2,RSR2,DXR2和XSR2寄存器只有當(dāng)接收或發(fā)送的字

長(zhǎng)超過(guò)16 b(20 b,24 b和32 b)時(shí),才會(huì)用上。

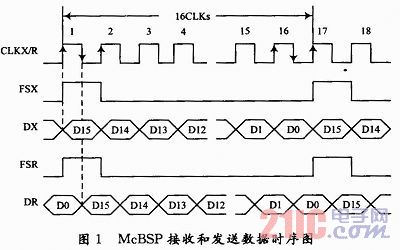

0位數(shù)據(jù)延遲時(shí),McBSP串口接收和發(fā)送數(shù)據(jù)的時(shí)序圖如圖1所示。

2 ADS7863

2.1 ADS7863芯片的特點(diǎn)

ADS7863是一個(gè)雙路、2 MSPS、12位、3+3或2+2通道、同步采樣模/數(shù)SAR轉(zhuǎn)換器。ADS7863具有如下特點(diǎn):四路全差分或六路偽差分輸入;SNR:71 dB,THD:-81 dB;可編程的和緩沖的內(nèi)部2.5 V參考電壓;靈活的省電功能;可變的電源范圍:2.7~5.5 V;低功率操作:5 V時(shí)45 mW;工作溫度范圍:-40~+125℃;引腳與ADS7861,ADS8361兼容。

2.2 ADS7863芯片的工作原理

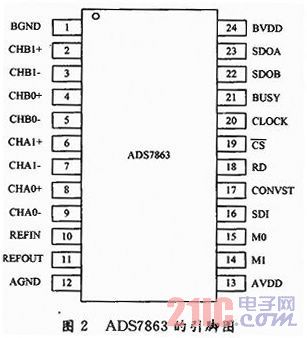

ADS7863的引腳圖如圖2所示。

2.2.1 ADS7863的主要引腳定義

ADS7863的主要引腳定義如下:CHxy+:同相模擬輸入通道xy+(x代表A或B,y代表0或1,eg:A1+);CHxy-:反相模擬輸入通道xy~(x代表A或B,y代表0或1,eg:A1-);M1:模式引腳1,選擇SDOx數(shù)字輸出,x代表A或B;M0:模擬引腳0,選擇模擬輸入通道;SDI:串行數(shù)據(jù)輸入,這個(gè)管腳允許使用ADS7863的增加功能,并且這些功能可以用在ADS7861的兼容模式上;CONVST:轉(zhuǎn)換開(kāi)始,不管CLOCK的狀態(tài),在CONVST的上升沿ADC從采樣模式進(jìn)入保持模式,轉(zhuǎn)換本身在CLOCK的下一個(gè)上升沿開(kāi)始;RD:讀數(shù)據(jù),SDOx輸出與SDI輸入的同步脈沖,RD只在![]() 為低時(shí)觸發(fā);

為低時(shí)觸發(fā);![]() :芯片選擇,當(dāng)置低時(shí),SDOx輸出有效,當(dāng)置高時(shí),SDOx輸出3態(tài)。CLOCK:外部時(shí)鐘輸入;BUSY:ADC忙碌指示符,當(dāng)進(jìn)入保持模式時(shí),BUSY變成高電平,轉(zhuǎn)換結(jié)束后,BUSY變成低電平;SDOB:轉(zhuǎn)換器B的串行數(shù)據(jù)輸出,在CLOCK的下降沿?cái)?shù)據(jù)是有效的;SDOA:轉(zhuǎn)換器A的串行數(shù)據(jù)輸出,當(dāng)M1為高時(shí),SDOA與SDOB都是有效的,數(shù)據(jù)在CLOCK的下降沿是有效的。

:芯片選擇,當(dāng)置低時(shí),SDOx輸出有效,當(dāng)置高時(shí),SDOx輸出3態(tài)。CLOCK:外部時(shí)鐘輸入;BUSY:ADC忙碌指示符,當(dāng)進(jìn)入保持模式時(shí),BUSY變成高電平,轉(zhuǎn)換結(jié)束后,BUSY變成低電平;SDOB:轉(zhuǎn)換器B的串行數(shù)據(jù)輸出,在CLOCK的下降沿?cái)?shù)據(jù)是有效的;SDOA:轉(zhuǎn)換器A的串行數(shù)據(jù)輸出,當(dāng)M1為高時(shí),SDOA與SDOB都是有效的,數(shù)據(jù)在CLOCK的下降沿是有效的。

2.2.2 ADS7863的工作原理

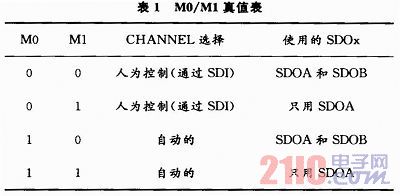

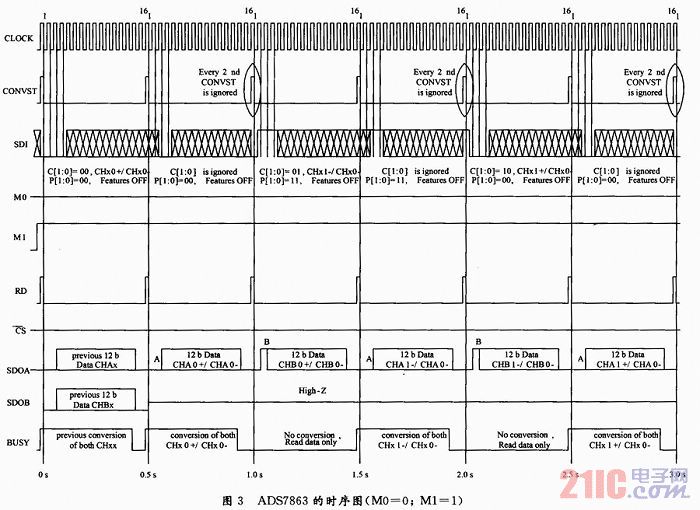

ADS7863的工作模式根據(jù)M0,M1的不同配置分為四種,如表1所示。本文主要介紹ADS7863的M0=0,M1=1模式時(shí)的工作原理。當(dāng)M0=0、M1= 1時(shí),ADS7863工作在人為通道控制模式,數(shù)據(jù)只在SDOA腳輸出,SDOB腳置為3態(tài)。SDI選擇不同的模擬輸入通道。當(dāng)CONVST置高時(shí),一個(gè)轉(zhuǎn)換被觸發(fā)。ADS7863需要32個(gè)CLOCK周期從兩個(gè)模/數(shù)轉(zhuǎn)換器ADCs輸出轉(zhuǎn)換結(jié)果,需要1.0μs完成一個(gè)完整的CONVERSION/READ周期。如果CONV-ST信號(hào)每0.5μs被觸發(fā)一次(RD信號(hào)的需要),那么每第二個(gè)脈沖被忽略。在CONVST的上升沿,不管CLOCK的狀態(tài),ADC從采樣模式進(jìn)入保持模式。經(jīng)過(guò)一些延遲,BUSY信號(hào)變成高電平,并且在轉(zhuǎn)換周期內(nèi)保持高電平。在第二個(gè)時(shí)鐘的下降沿,根據(jù)SDI寄存器的C[1:0]兩位的狀態(tài),ADS7863選擇使用下一個(gè)轉(zhuǎn)換周期的模擬輸入通道。CS必須置為低電平以使能SDOA輸出。在每個(gè)轉(zhuǎn)換的每32個(gè)CLOCK周期的下降沿,數(shù)據(jù)是有效的。輸出數(shù)據(jù)由一個(gè)‘0’,緊接一個(gè)ADC指示符(CHAx為‘0’,CHBx為‘1’),12位轉(zhuǎn)換結(jié)果,和一個(gè)‘00’組成。

相應(yīng)的時(shí)序圖如圖3所示。

3 TMS320F28335 McBSP與ADS7863接口設(shè)計(jì)

3.1 硬件接口設(shè)計(jì)

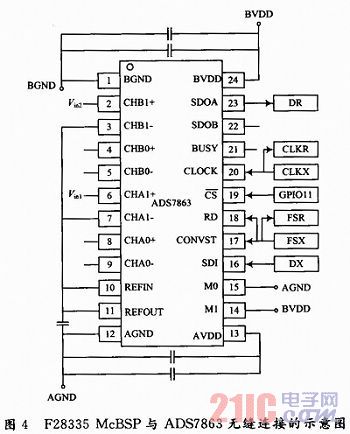

圖4是TMS320F28335 McBSP與ADS7863無(wú)縫連接的示意圖。從圖中可以看出,McBSP與ADS7863之間的連接非常簡(jiǎn)單,實(shí)現(xiàn)了數(shù)據(jù)的高效轉(zhuǎn)移,充分體現(xiàn)了同步串口連接的優(yōu)點(diǎn)。由F28335 DSP的GPIO11向ADS7863提供片選信號(hào)。McBSP的數(shù)據(jù)發(fā)送DX腳接ADS7863的SDI腳,向ADS7863發(fā)出控制信號(hào)。ADS7863的SDOA腳接McBSP的數(shù)據(jù)接收DR腳,向F28335傳送數(shù)據(jù)信號(hào)。由MeBSP內(nèi)含的可編程采樣率發(fā)生器生成時(shí)鐘信號(hào)CLKG和幀同步信號(hào)FSG。由CLKG驅(qū)動(dòng)發(fā)送時(shí)鐘信號(hào)CLKX,CLKX驅(qū)動(dòng)接收時(shí)鐘信號(hào)CLKR和ADS7863的時(shí)鐘信號(hào)CLOCK。由FSG驅(qū)動(dòng)發(fā)送幀同步信號(hào)FSX,F(xiàn)SX驅(qū)動(dòng)接收幀同步信號(hào)FSR和ADS7863的開(kāi)始轉(zhuǎn)換信號(hào)CONVST。CONVST初始化一個(gè)轉(zhuǎn)換進(jìn)程,并啟動(dòng)發(fā)送前一周期轉(zhuǎn)換的數(shù)據(jù)。為了簡(jiǎn)化,只連接了ADS7863的CHA1+和CHB1+通道,可用輸出數(shù)據(jù)的第二位(ADC指示符)分辨所采樣的信號(hào)來(lái)自哪個(gè)通道。

3.2 軟件接口設(shè)計(jì)

3.2.1 McBSP口初始化

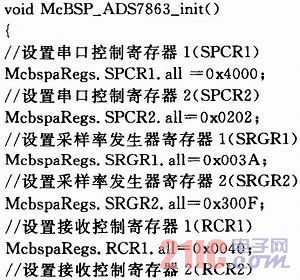

整個(gè)初始化過(guò)程包括三部分:接收部分初始化、發(fā)送部分初始化和采樣率發(fā)生器初始化。

(1)DSP初始化后,采樣率發(fā)生器的初始化位GRST=0;在其他情況下,也可通過(guò)向SPCR2寄存器中的GRST位置0,使采樣率發(fā)生器處于初始化狀態(tài)。在此狀態(tài)下,時(shí)鐘CLKG時(shí)鐘為CPU時(shí)鐘的1/2,幀同步信號(hào)FSG為邏輯0;設(shè)置接收初始化位RRST、發(fā)送初始化位XRST和幀同步發(fā)生器初始化位FRST為0;

(2)對(duì)采樣率發(fā)生器SRGR[1,2]進(jìn)行設(shè)置,并對(duì)其他控制寄存器進(jìn)行設(shè)置;

(3)等待兩個(gè)CPU時(shí)鐘以確保內(nèi)部正確同步;

(4)將采樣率發(fā)生器初始化位置1,使采樣率發(fā)生器進(jìn)行工作;

(5)等待兩個(gè)SRG時(shí)鐘;

(6)將接收和發(fā)送初始化位置1;

(7)在下一個(gè)CPU時(shí)鐘的上升沿,CLKG時(shí)鐘發(fā)送一個(gè)1,并以CPU時(shí)鐘/(1+CLKGDV)的頻率運(yùn)行;

(8)在數(shù)據(jù)發(fā)送寄存器DXR[1,2]被載入數(shù)據(jù)后,將幀同步初始化位置1以發(fā)出正確的幀同步脈沖信號(hào)。

下面是McBSP初始化程序片段:

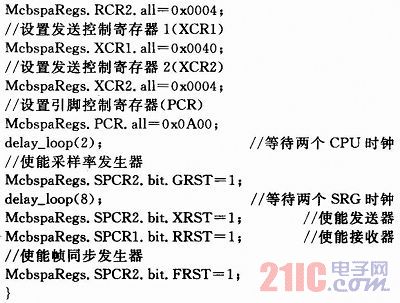

3.2.2 McBSP串口通信主要程序

McBSP串口通信主要程序如下:

4 試驗(yàn)結(jié)果

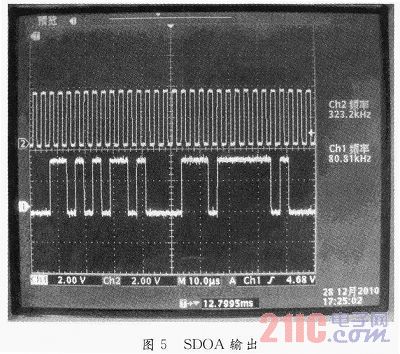

ADS7863的輸入模擬量Vin1=1.670 V,Vin2=1.866 V時(shí),A/D轉(zhuǎn)換器SDOA引腳輸出如圖5所示。圖中通道Ch2為ADS7863的外部輸入時(shí)鐘CLOCK,通道Ch1為ADS7863的模擬輸入通道CHA1+和CHB1+的32位輸出結(jié)果。可以很清楚地看出該32位二進(jìn)制碼為:00110101011010000111011 111101000,前16位為CHA1+通道的轉(zhuǎn)換結(jié)果,后16位為CHB1+通道的轉(zhuǎn)換結(jié)果。在本試驗(yàn)中,通過(guò)設(shè)置McBSP的采樣率發(fā)生器時(shí)鐘分頻系數(shù)CLKGDV,使得McBSP的采樣率發(fā)生器時(shí)鐘CLKG頻率為323.2 kHz,從而使得ADS7863的外部輸入時(shí)鐘CLOCK頻率為323.2kHz。

5 結(jié)論

本文設(shè)計(jì)了高速度、高精度12位A/D轉(zhuǎn)換器ADS7863與32位浮點(diǎn)DSP TMS320F28335的McBSP之間的硬件接口與軟件實(shí)現(xiàn)。該系統(tǒng)設(shè)計(jì)簡(jiǎn)潔,在DSP集成開(kāi)發(fā)環(huán)境CCS下采用C語(yǔ)言編寫(xiě)、調(diào)試完成,對(duì)其他A/D系統(tǒng)設(shè)計(jì)具有很大的借鑒意義。