基準(zhǔn)電壓源廣泛應(yīng)用于各種模擬集成電路、數(shù)/模混合信號集成電路和系統(tǒng)集成芯片(SoC)中,是集成電路的一個(gè)基本元件,其穩(wěn)定性直接影響到整個(gè)系統(tǒng)的精度。然而,傳統(tǒng)的高性能基準(zhǔn)電路普遍采用帶隙基準(zhǔn)電路,與標(biāo)準(zhǔn)CMOS工藝不兼容。為了解決帶隙基準(zhǔn)電路與標(biāo)準(zhǔn)CMOS工藝不兼容問題,一些學(xué)者提出了一定的解決方法,例如:利用N阱的寄生二極管設(shè)計(jì)帶隙基準(zhǔn),利用CMOS管的亞閾值區(qū)工作原理設(shè)計(jì)基準(zhǔn),利用載流子和閾值電壓在不同溫度下的特性設(shè)計(jì)基準(zhǔn)等。但是他們的電源抑制比普遍偏低,且溫度系數(shù)較大。

本文利用高電源抑制比電路設(shè)計(jì)的和式偏置電流源進(jìn)一步提高了電源抑制比,并利用NMOS和PMOS管的兩個(gè)閾值電壓VTHN和VTHP具有相同方向但不同數(shù)量的溫度系數(shù),設(shè)計(jì)了一種基于不同VTH值的新型CMOS基準(zhǔn)。該設(shè)計(jì)充分利用CMOS器件高輸入阻抗、低功耗的特點(diǎn),利用相同電流減少了載流子遷移率對溫度性能的影響,利用VRHN和VTHP溫度系數(shù)抵消原理和高電源抑制比和式電流源,大大降低了基準(zhǔn)的溫度系數(shù),提高了電源抑制特性,使電路的性能得到優(yōu)化。

1 傳統(tǒng)帶隙電路原理

如圖1所示,傳統(tǒng)的帶隙電路主要是利用雙極型晶體管的基極-發(fā)射極電壓VBE具有負(fù)溫度系數(shù),而兩個(gè)不同電流密度的雙極型晶體管之間的基極一發(fā)射極電壓差△VBE具有正溫度系數(shù),將其乘以合適的系數(shù)K后,再與前者進(jìn)行加權(quán),即:VREF=VBEK△VBE,從而在一定范圍內(nèi)就可以抵消VBE的溫度漂移效應(yīng),得到低溫漂的輸出電壓VREF。K值將通過把VBE的表達(dá)式帶入VREF中,在參考溫度T0處令![]() 求得。

求得。

但是使用BJT管會占用很大的芯片面積且與在標(biāo)準(zhǔn)CMOS工藝中不能很好的兼容。

2 新型CMOS基準(zhǔn)電路原理

對于CMOS器件,其閾值電壓VTH和載流子遷移率μ是主要的受溫度因數(shù)影響的參量。雖然閾值電壓VTH和載流子遷移率μ的值都隨著溫度的升高而減小,但是MOS器件閾值電壓VTH和載流子遷移率μ的下降對于MOS管的漏電流ID有著完全相反的效果:閾值電壓VTH越低,漏電流ID越大;而載流子遷移率μ越小,漏電流ID越小。

由文獻(xiàn)可知,閾值電壓VTH與環(huán)境溫度有著近似的線性關(guān)系:

![]()

式中:aVT是閾值電壓VTH的溫度系數(shù),其值介于1~4 mV/℃之間,對NMOS和PMOS是相互獨(dú)立且不同的。

載流子遷移率μ和環(huán)境溫度的關(guān)系為:

![]()

式中:μ(T0)是某基準(zhǔn)溫度時(shí)的載流子遷移率,且m介于1~2.5之間。

由式(1)可知,VTHN和VTHP具有不同的負(fù)溫度系數(shù),只要取合適的系數(shù)K時(shí):

![]()

就可以得到不隨溫度變化的基準(zhǔn)電壓VREF。

3 新型CMOS基準(zhǔn)電路設(shè)計(jì)

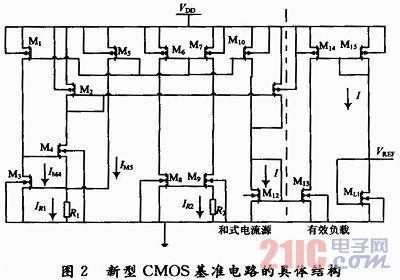

圖2為本文利用標(biāo)準(zhǔn)CMOS工藝設(shè)計(jì)的基準(zhǔn)電路。該電路主要由啟動電路、和式電流產(chǎn)生電路、有效負(fù)載電路構(gòu)成。電路的基本原理是利用高性能和式電流源產(chǎn)生高電源抑制比的PTAT電流,再利用NMOS和PMOS管的兩個(gè)閾值電壓VTHN和VTHP具有相同方向,但不同數(shù)量的溫度系數(shù)設(shè)計(jì)了一種基于不同VTH值的新型CMOS基準(zhǔn)。

3.1 和式電流源電路

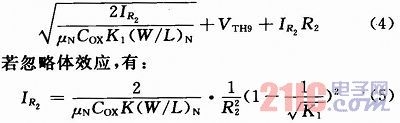

由圖2可見,和式電流產(chǎn)生電路由自舉式偏置電路(由MOS管M6~M9和電阻R2構(gòu)成)產(chǎn)生偏置電流。設(shè)M9與M8的寬長比為K1,則有:

但是由于體效應(yīng)的存在,使得R2中的電流隨電源電壓VDD的變化有一定改變。所以文中引入和式電流產(chǎn)生電路。

如圖2可知,電阻R1中的電流值為:

式中:K2為M5與M6的寬長比。

由于MOS管的柵源電壓VGS幾乎不隨電源電壓的變化而變化,由式(6)、式(7)可知MOS管M4中的電流IM4的變化方向與R2中的電流IR2隨電源電壓的變化方向相反。

由圖2可知,取K3,K4分別為M10與M7,M11與M2的寬長比,M13與M12,M15與M14的寬長比為1,則MOS管ML1中的電流I為:

![]()

合理選擇式(8)中的K3,K4就能減小電源電壓VDD對電流I的影響。

由上面的分析和式電流源電路可以進(jìn)一步減小電源電壓對輸出電流的影響。

3.2 有效負(fù)載電路

由圖2可知,電流I流過MOS管M15,ML1時(shí):

![]()

由式(2)可知,載流子遷移率μ是溫度的高階函數(shù),若近似認(rèn)為μN,μP的溫度變化量相等,可將K看作常數(shù),可得:

![]()

由式(3)和式(13)可知,取恰當(dāng)?shù)腒值,即合理選擇MOS管M15和ML1的寬長比,就可以使閾值電壓VTHN和VTHP的溫度系數(shù)相抵消,使VREF幾乎不隨環(huán)境溫度的變化而變化。

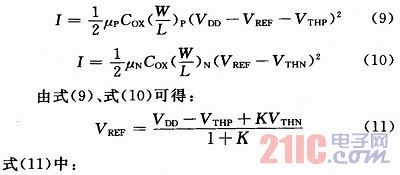

3.3 電路的優(yōu)化

在圖2中MOS管M12,M13,M14,M15起電流鏡像作用,可以將這4個(gè)管子省去,直接將負(fù)載管ML1接到M10和M11的漏極。這樣將圖2優(yōu)化成圖3就可以少4個(gè)MOS管,節(jié)省版圖面積。

4 仿真與分析

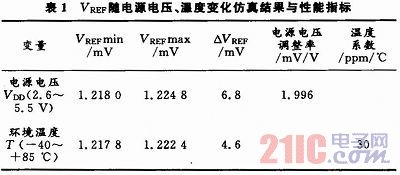

通過上面的分析,初步確定該電路各器件尺寸,在0.6μm CMOS工藝下采用HSpice軟件進(jìn)行仿真可以得出,在3.3 V電源電壓下對溫度在-40~85℃范圍內(nèi)進(jìn)行直流掃描,基準(zhǔn)電壓曲線如圖4所示。在25℃下,對電源電壓在2.6~5.5 V的范圍內(nèi)進(jìn)行直流掃描,基準(zhǔn)電壓曲線如圖5所示。據(jù)此計(jì)算出的基準(zhǔn)電壓電源電壓調(diào)整率、溫度系數(shù)見表1。

與國際上已有的和CMOS兼容的電壓基準(zhǔn)電路的主要指標(biāo)進(jìn)行比較,結(jié)果如表2所示。可以看出,本文設(shè)計(jì)的CMOS基準(zhǔn)的溫度漂移率TFC遠(yuǎn)遠(yuǎn)小于國際上已有的和CMOS兼容的電壓基準(zhǔn)電路。

5 結(jié)語

本文所設(shè)計(jì)的基于CMOS工藝的基準(zhǔn)電路結(jié)構(gòu)較簡單,既沒有放大器,也沒有BJT,適合于標(biāo)準(zhǔn)CMOS工藝生產(chǎn)。通過HSpice驗(yàn)證,其輸出基準(zhǔn)電壓為1.22 V,在-40~85℃內(nèi)溫度系數(shù)僅為30 ppm/℃。當(dāng)電源電壓為2.6~5.5 V時(shí),電源電壓調(diào)整率為1.996 mV/V,且溫度漂移率TFC遠(yuǎn)遠(yuǎn)小于國際上已有的和CMOS兼容的電壓基準(zhǔn)電路,比較適合于標(biāo)準(zhǔn)CMOS工藝。