摘要:采用Verilog HDL語言作為硬件功能的描述,運(yùn)用模塊化設(shè)計(jì)方法分別設(shè)計(jì)了通用異步收發(fā)器(UART)的發(fā)送模塊、接收模塊和波特率發(fā)生器,并結(jié)合現(xiàn)場可編程門陣列(FPGA)的特點(diǎn),實(shí)現(xiàn)了一個(gè)可移植的UART模塊。該設(shè)計(jì)不僅實(shí)現(xiàn)了串行異步通信的主要功能,而且電路簡單,工作穩(wěn)定、可靠,可以將其靈活地嵌入到各個(gè)通信系統(tǒng)中。

關(guān)鍵詞:通用異步收發(fā)器;現(xiàn)場可編程門陣列;Verilog HDL;串行通信

串行通信要求的傳輸線少,可靠性高,傳輸距離遠(yuǎn),被廣泛應(yīng)用于計(jì)算機(jī)和外設(shè)的數(shù)據(jù)交換。通常都由通用異步收發(fā)器(UART)來實(shí)現(xiàn)串口通信的功能。在實(shí)際應(yīng)用中,往往只需要UART的幾個(gè)主要功能,專用的接口芯片會造成資源浪費(fèi)和成本提高。隨著FPGA/CPLD的飛速發(fā)展與其在現(xiàn)代電子設(shè)計(jì)中的廣泛應(yīng)用,F(xiàn)PGA/CPLD功能強(qiáng)大、開發(fā)過程投資小、周期短、可反復(fù)編程、保密性好等特點(diǎn)也越來越明顯。因此可以充分利用其資源,在芯片上集成UART功能模塊,從而簡化了電路、縮小了體積、提高了可靠性,而且設(shè)計(jì)時(shí)的靈活性更大,周期更短。鑒于此本文提出了一種采用FPGA實(shí)現(xiàn)UART功能的方法,可以有效地解決上述問題。

1 UART的工作原理

UART(Universal Asynchronous Receiver Transmitter,通用異步收發(fā)器)是廣泛使用的異步串行數(shù)據(jù)傳輸協(xié)議。在串行通信中,數(shù)據(jù)以字節(jié)為單位的字節(jié)幀進(jìn)行傳送。發(fā)送端和接收端必須按照相同的字節(jié)幀格式和波特率進(jìn)行通信。UART控制器所傳輸?shù)囊粠袛?shù)據(jù)包括1位起始位(低電平)、5~8位數(shù)據(jù)位、1位校驗(yàn)位(可選)和停止位(可為1,1.5,2位)。起始位是字節(jié)幀的開始,使數(shù)據(jù)線處于邏輯0狀態(tài),用于向接收端表明開始發(fā)送數(shù)據(jù)幀,起到使發(fā)送和接收設(shè)備實(shí)現(xiàn)同步的功能。停止位是字節(jié)幀的終止,使數(shù)據(jù)線處于邏輯1狀態(tài)。用于向接收端表明數(shù)據(jù)幀發(fā)送完畢。波特率采用標(biāo)準(zhǔn)速率9 600 b/s。數(shù)據(jù)在傳輸時(shí),低位在前,高位在后。接收端檢測并確認(rèn)起始位后,接收數(shù)據(jù)位。停止

位接收完畢后,向CPU發(fā)出中斷信號,同時(shí)將數(shù)據(jù)發(fā)送到計(jì)算機(jī)的8位數(shù)據(jù)總線上;發(fā)送數(shù)據(jù)時(shí),先由CPU設(shè)置波特率,然后將8位并行數(shù)據(jù)加上起始位和停止位發(fā)送給外設(shè)。停止位發(fā)送完畢后,向CPU發(fā)出中斷信號。在數(shù)據(jù)發(fā)送和接收過程中,CPU可以通過控制信號來讀取UART的工作狀態(tài),以便進(jìn)行實(shí)時(shí)處理。

2 UART的模塊化設(shè)計(jì)

2.1 系統(tǒng)總體結(jié)構(gòu)

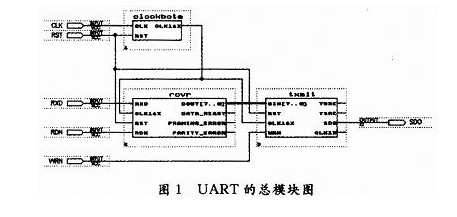

在大規(guī)模電路的設(shè)計(jì)中,廣泛采用層次化、結(jié)構(gòu)化的設(shè)計(jì)方法。它將一個(gè)完整的硬件設(shè)計(jì)任務(wù)從系統(tǒng)級開始,劃分為若干個(gè)可操作的模塊,編制出相應(yīng)的模型并進(jìn)行仿真驗(yàn)證,最后在系統(tǒng)級上進(jìn)行組合。這樣在提高設(shè)計(jì)效率的同時(shí)又提高了設(shè)計(jì)質(zhì)量,是目前復(fù)雜數(shù)字系統(tǒng)實(shí)現(xiàn)的主要手段,也是本文設(shè)計(jì)思想的基礎(chǔ)。按照系統(tǒng)功能進(jìn)行劃分,UART主要由波特率發(fā)生器、接收模塊和發(fā)送模塊三大部分組成。在Maxp-lusⅡ仿真環(huán)境下,由各個(gè)子模塊進(jìn)行綜合的系統(tǒng)總模塊如圖1所示。下面分別討論發(fā)送模塊、接收模塊和波特率發(fā)生器模塊的具體實(shí)現(xiàn)過程。

2.2 發(fā)送模塊

2.2.1 發(fā)送模塊及其功能

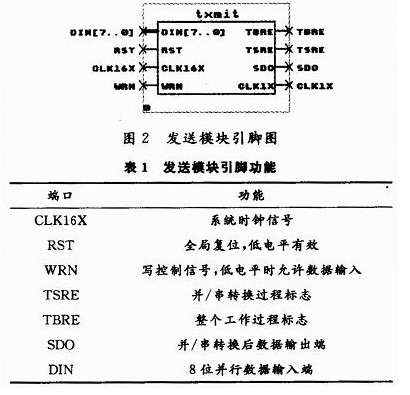

發(fā)送模塊主要實(shí)現(xiàn)對并行數(shù)據(jù)的緩存、并串轉(zhuǎn)換,并把串行數(shù)據(jù)按照既定數(shù)據(jù)幀格式進(jìn)行輸出。發(fā)送模塊的引腳如圖2所示,各引腳功能見表1。

由CPU送來的待發(fā)送的并行數(shù)據(jù),首先寫入發(fā)送緩沖器TBR[7..0]。發(fā)送緩沖區(qū)中有數(shù)據(jù)待發(fā)送時(shí),數(shù)據(jù)自動裝入移位寄存器TSR[7..0]并自動完成串行數(shù)據(jù)的發(fā)送。首先傳送一位起始位0,然后根據(jù)幀結(jié)構(gòu)中定義的數(shù)據(jù)長度,分別串行移出TSR[7..0]中的數(shù)據(jù),數(shù)據(jù)的低位在前,高位在后。當(dāng)沒有數(shù)據(jù)發(fā)送的時(shí)候,SDO管腳保持高電平。

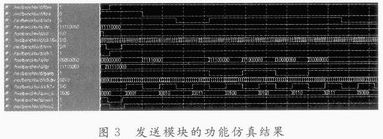

2.2.2 發(fā)送模塊功能仿真

發(fā)送器功能仿真結(jié)果如圖3所示。二進(jìn)制數(shù)11110000從引腳DIN[7..0]并行輸入,當(dāng)WRN為0時(shí),啟動發(fā)送程序,計(jì)數(shù)器開始計(jì)數(shù),使發(fā)送器將并行數(shù)據(jù)鎖存到發(fā)送緩沖器TBR[7..0],并通過發(fā)送移位寄存器TSR[7..0]逐位移位發(fā)送串行數(shù)據(jù)至串行數(shù)據(jù)輸出端SDO。在數(shù)據(jù)發(fā)送過程中用輸出信號TBRE,TSRE作為標(biāo)志信號。當(dāng)一幀數(shù)據(jù)由發(fā)送緩沖器TBR[7..0]送到發(fā)送移位寄存器TSR[7..0]時(shí),TBRE信號為1。由發(fā)送數(shù)據(jù)緩沖器傳給發(fā)送移位寄存器主要由信號TSRE控制。當(dāng)TSRE為1時(shí),表示發(fā)送移位寄存器TSR[7..0]串行發(fā)送完畢;為0時(shí)表示還沒

有發(fā)送完一幀數(shù)據(jù)。由仿真結(jié)果驗(yàn)證了發(fā)送模塊的正確性。

2.3 接收模塊

2.3.1 接收模塊及其功能

接收模塊的作用是把收到的串行數(shù)據(jù)轉(zhuǎn)換成并行數(shù)據(jù)進(jìn)行輸出,并判斷收到的數(shù)據(jù)是否有錯。接收模塊的引腳如圖4所示,各引腳功能見表2。

接收器進(jìn)入準(zhǔn)備接收數(shù)據(jù)狀態(tài),不斷監(jiān)視串行輸入線RXD端,如果出現(xiàn)低電平,立刻啟動起始位檢測電路進(jìn)行確認(rèn),一旦確認(rèn)為接收到正確的起始位,則以波特率作為采樣時(shí)鐘,對每個(gè)數(shù)據(jù)位的中間位置采樣一次,并把采樣到的信息以移位方式送人接收移位寄存器RSR。接收到一幀數(shù)據(jù)位后,把串行數(shù)據(jù)轉(zhuǎn)化成并行數(shù)據(jù),并進(jìn)行奇偶校驗(yàn)、停止位、中止態(tài)的檢查。接收完畢后,DAT_READ置1。

2.3.2 接收模塊功能仿真

接收模塊功能仿真結(jié)果如圖5所示。二進(jìn)制數(shù)11101010從引腳RXD串行輸入,接收器先要捕捉起始位,在RDN信號為0條件下,啟動接收程序,計(jì)數(shù)器開始計(jì)數(shù),數(shù)據(jù)從RXD[7..0]串行輸入,由接收移位寄存器RSR[7..0]逐位移位接收,并在接收完成時(shí)傳送給接收緩沖寄存器RBR[7..0],最后接收緩沖寄存器RBR[7..0]將接收的數(shù)據(jù)傳送至DOUT[7..0],由它并行輸出,同時(shí)輸出一個(gè)接收數(shù)據(jù)準(zhǔn)備好信號DATA _RE標(biāo)志數(shù)據(jù)接收完畢。

2.4 波特率發(fā)生器模塊

2.4.1 波特率發(fā)生器模塊及其功能

波特率發(fā)生器模塊主要用于產(chǎn)生接收模塊和發(fā)送模塊的時(shí)鐘頻率,其實(shí)質(zhì)就是一個(gè)分頻器,可以根據(jù)給定的系統(tǒng)時(shí)鐘頻率和要求的波特率算出波特率分頻因子,作為分頻器的分頻數(shù)。波特率發(fā)生器產(chǎn)生的時(shí)鐘頻率CLK16X不是波特率時(shí)鐘頻率CLK,而是波特率時(shí)鐘頻率CLK的16倍。波特率發(fā)生器模塊的引腳如圖6所示,其功能如表3所示。

2.4.2 波特率發(fā)生器功能仿真

UART在發(fā)送或接收數(shù)據(jù)時(shí),使用的時(shí)鐘信號頻率f是波特率(b=9 600 b/s)的16倍,由外部系統(tǒng)時(shí)鐘進(jìn)行16分頻得到。UART每16個(gè)波特時(shí)鐘發(fā)送或接收一個(gè)二進(jìn)制位,設(shè)計(jì)中采用的晶振頻率c=25 MHz,那么波特率發(fā)生器輸出的時(shí)鐘信號周期為:

![]()

波特率發(fā)生器的功能仿真如圖7所示。

本設(shè)計(jì)用晶振為25 MHz,由公式可得出輸出波形的半個(gè)周期應(yīng)為k/2,即81倍的輸入時(shí)鐘周期,仿真結(jié)果驗(yàn)證了波特率發(fā)生器模塊的正確性。

3 結(jié)語

UlART是廣泛使用的串行數(shù)據(jù)通信電路,因其要求的傳輸線少,可靠性高,傳輸距離遠(yuǎn),所以系統(tǒng)間互聯(lián)常采用異步串行通信接口方式。本文用Verilog HDL語言,結(jié)合有限狀態(tài)機(jī)的設(shè)計(jì)方法實(shí)現(xiàn)了UART的功能,將其核心功能集成到FPGA上,使整體設(shè)計(jì)緊湊、小巧,實(shí)現(xiàn)的UART功能穩(wěn)定、可靠;同時(shí),利用有限狀態(tài)機(jī)的方法具有結(jié)構(gòu)模式直觀簡單,設(shè)計(jì)流程短,程序?qū)哟畏置鳎拙C合,可靠性高等優(yōu)點(diǎn),必將在EDA技術(shù)中發(fā)揮重要作用。