摘要:介紹了一種采用DM642和CPLD相配合的擴(kuò)展鍵盤方法。CPLD管理鍵盤電路中的芯片邏輯,DM642的外部中斷監(jiān)控按鍵的狀態(tài)。簡單闡述了鍵盤的分類,給出系統(tǒng)的硬件電路原理圖,在CCS軟件中調(diào)試程序方法。仿真結(jié)果表明,設(shè)計可行,達(dá)到了預(yù)期效果。

關(guān)鍵詞:鍵盤;DM642;CPLD;人機(jī)交互

引言

鍵盤是人機(jī)交互模塊中必備的輸入部分,在目前的嵌入式系統(tǒng)人機(jī)接口中通常采用專用的鍵盤處理芯片ZLG7290設(shè)計鍵盤。由于ZLG7290是一種64位LED顯示和64個按鍵的鍵盤管理器件,會造成部分LED顯示和按鍵空閑浪費并占用硬件資源比較多,使成本增加。隨著DM642性價比的提高,它在圖像處理系統(tǒng)和數(shù)字媒體系統(tǒng)中的應(yīng)用越來越廣泛,而作為人機(jī)交互重要手段的鍵盤在上述系統(tǒng)中是必不可少的輸入設(shè)備。通常以DM642為核心的電路系統(tǒng)中主要采用獨立式鍵盤和行列掃描式鍵盤。本文在DM642電路系統(tǒng)中使用CPLD提供多路輸入/輸出引腳的方法擴(kuò)展鍵盤。DM642的外部中斷監(jiān)控按鍵的狀態(tài),CPLD管理鍵盤電路中的芯片邏輯。此外,CPLD(EPM7128AET芯片)共有100個輸入/輸出引腳,可根據(jù)實際需要自由擴(kuò)展引腳,實現(xiàn)靈活,應(yīng)用前景廣闊。

1 獨立式鍵盤和行列掃描式鍵盤

1.1 獨立式鍵盤

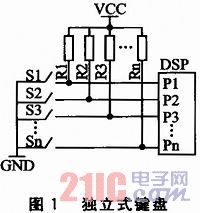

獨立式鍵盤是指將每個按鍵按一對一的方式直接連接到I/O輸入線上所構(gòu)成的鍵盤。獨立式鍵盤可以工作在多種方式下:中斷方式、程序查詢方式、定時查詢發(fā)送和中斷查詢方式。獨立式鍵盤的缺點是需要占用較多的I/O線。當(dāng)應(yīng)用系統(tǒng)中需要的按鍵比較少或I/O線比較富余時,可以把單個按鍵與DSP的輸入/輸出引腳直連,采用查詢或中斷方式檢測鍵值。電路如圖1所示,S1~Sn表示n個按鍵,按鍵的輸入端接地,輸出端與DSP的輸入/輸出引腳P1~Pn相連,并接上拉電阻。DSP可以采用查詢方式檢測鍵值,也可以采用中斷方式監(jiān)控按鍵的狀態(tài)。

1.2 行列掃描式鍵盤

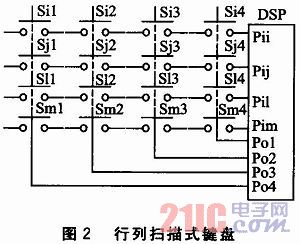

行列掃描式鍵盤是行列式鍵盤中最主要的一種,是用n條I/O線作為行線,m條I/O線作為列線組成的鍵盤。在行線和列線的每一個交叉點上,設(shè)置一個按鍵。這樣,鍵盤中按鍵的個數(shù)是m×n個。它適合于構(gòu)成按鍵數(shù)目比較多的鍵盤。這種形式的鍵盤結(jié)構(gòu),能夠有效地提高系統(tǒng)中I/O口的利用率。行列掃描式是先使列(行)線全輸出低電平,然后判斷行(列)線狀態(tài),若行線全為高電平表示無鍵被按下,若行線不全為高電平表示有鍵被按下。然后依次使列線為低電平,再判斷行線狀態(tài),當(dāng)行線全為高電平時表示被按下的鍵不在本列,當(dāng)行線不全為高電平時表示被按下的鍵在本列,把此時的行線狀態(tài)與列線狀態(tài)和在一起即為被按下的鍵的位置。掃描法對鍵的識別采用逐行(列)掃描的方法獲得鍵的位置,當(dāng)被按下的鍵在最后一行時需要掃描N次(N為行數(shù)),當(dāng)N比較大時鍵盤工作速度較慢。如圖2所示,該鍵盤為16鍵行列掃描式鍵盤,具有4路輸入引腳Pn~Pi4和4路輸出引腳Po1~Po4配合使用。當(dāng)DSP工作于查詢方式時,按鍵不需要加上拉或下拉電阻。

2 外部中斷的寄存器式鍵盤

2.1 系統(tǒng)總體結(jié)構(gòu)

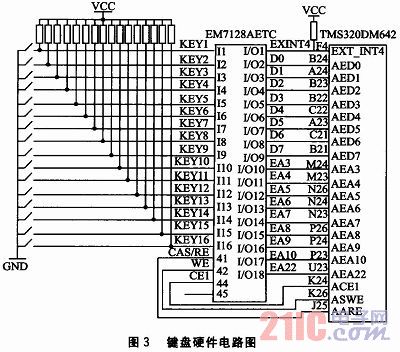

鍵盤系統(tǒng)中CPLD選用EPM7128AET芯片,能提供多路輸入/輸出引腳,輸出邏輯電平為3.3 V,輸入邏輯電平兼容3.3 V和5 V兩種,共100個輸入/輸出引腳。CPLD在邏輯控制和時序控制方面具有很多優(yōu)勢,它的內(nèi)部擁有大量的邏輯門,可以在軟件環(huán)境中巧妙地利用這些門電路,對輸入引腳信號進(jìn)行各種邏輯組合設(shè)計,將邏輯組合信號再提供給輸出引腳。CPLD器件內(nèi)部還提供了大量標(biāo)準(zhǔn)的邏輯電路模塊,如譯碼電路、地址鎖存電路等,這些電路模塊代替了傳統(tǒng)電路中需要的譯碼芯片、地址鎖存芯片等,不僅為電路板設(shè)計節(jié)省空間,而且使電路設(shè)計流程更加靈活和方便。DSP選用TMS320DM642芯片,為了擴(kuò)展DM642的GPIO輸入/輸出引腳而設(shè)計成16按鍵的鍵盤,CPLD需使用DM642的低8位數(shù)據(jù)總線D[7:0]、地址總線EA[10:3]、EA22和讀寫控制信號線,CPLD才能在內(nèi)部產(chǎn)生所需的擴(kuò)展寄存器。CPLD豐富的輸入/輸出引腳和大量的邏輯門管理鍵盤系統(tǒng)中的芯片邏輯。如圖3所示,按鍵的16個輸入端接地,輸出端KEY[1:16]與CPLD芯片的輸人引腳I[1:16]連接,輸出端接上拉電阻,DM642的低8位數(shù)據(jù)總線D[7:0]、地址總線EA[10:3]及EA22與CPLD器件的輸入/輸出引腳I/O[1:18]連接,DM642的RE和WE信號是寄存器擴(kuò)展用的讀/寫使能信號,空間片選信號CE1和地址信號EA22作為寄存器端口片選信號,把按鍵狀態(tài)讀端口映射到DM642的CE1空間。當(dāng)有按鍵按下時,產(chǎn)生一個上升沿脈沖觸發(fā)信號,該信號可以認(rèn)為是一個外部中斷事件,那么可以通過DM642的外部中斷EXINT4響應(yīng)該中斷事件,而在DM642內(nèi)部EXINT4可以映射為中斷INT4,DM642在INT4對應(yīng)的中斷函數(shù)中通過數(shù)據(jù)地址總線讀取按鍵的鍵值并進(jìn)行分析。在程序?qū)用妫摪存I的觸發(fā)信號和程序中INT4的中斷服務(wù)函數(shù)相對應(yīng),同時INT4的中斷服務(wù)函數(shù)與中斷向量表中的中斷編號聯(lián)系起來。

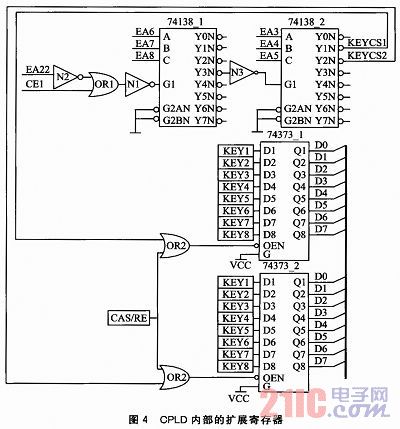

CPLD芯片內(nèi)部擴(kuò)展按鍵狀態(tài)的16位輸入端口控制寄存器邏輯圖如圖4所示,DM642通過操作寄存器讀端口實現(xiàn)讀取按鍵的鍵值并進(jìn)行分析。在圖4中,DM642的空間片選信號CE1和地址信號EA22作為寄存器端口片選信號,當(dāng)CE1信號低電平有效時,與鍵盤狀態(tài)有關(guān)的寄存器地址被映射到CE1空間,地址線EA22在映射關(guān)系中低電平有效。CE1空間地址有效范圍為0x90000000~0x9FFFFFFF,按鍵KEY1~KEY8的寄存器端口地址為0x90080019,KEY9~KEY16的寄存器端口地址為0x9008001A。KEYCS[2:1]為輸入端口的片選信號線,兩路輸入片選信號分別對應(yīng)I[1:8]和I[9:16]輸入引腳。芯片74138是CPLD內(nèi)部提供的一種譯碼器,芯片74373是CPLD內(nèi)部提供的一種地址鎖存器,用于鎖存按鍵按下時的電平狀態(tài)。

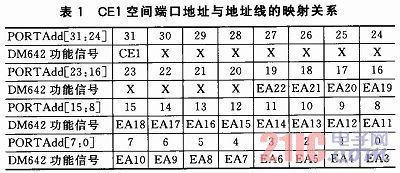

這里將擴(kuò)展的寄存器端口地址設(shè)置為PORTAdd,PORTAdd在CE1空間中擁有一個32位的端口地址,PoRTAdd[31:0]與DM642的CE1信號和EA[22:3]地址信號之間的定義關(guān)系如表1所列。CE1信號決定了PORTAdd31位,EA[22:3]地址信號決定了寄存器端口地址的PORTAdd[19:0]位,PORTAdd端口的其他位保留未用。根據(jù)表1中的映射關(guān)系就可以確定CPLD內(nèi)部寄存器端口的物理地址。在圖4中,CE1信號保持低電平、EA22信號保持高電平時選中74138_1芯片,則PORTAdd的第31位和第19位均應(yīng)為高電平“1”;EA8~EA6為高位譯碼地址線,EA5~EA3為低位譯碼地址線,兩片74138芯片配合使用,能夠產(chǎn)生64路片選信號;片選信號KEYCS1和KEYCS2低電平有效,兩片74373在DM642的CE1空間中的地址分別為0x90080019和0x9008001A。

3 軟件設(shè)計

在CCS編程環(huán)境中,編寫main.C、boot.a(chǎn)sm、ves_dm642.a(chǎn)sm、key.cmd等文件,由于在CSL中包含boot.a(chǎn)sm函數(shù),所以只需要自行編寫main.c和ves_dm642.a(chǎn)sm、key.cmd三個文件,然后添加到所創(chuàng)建的Key.pJt項目中。

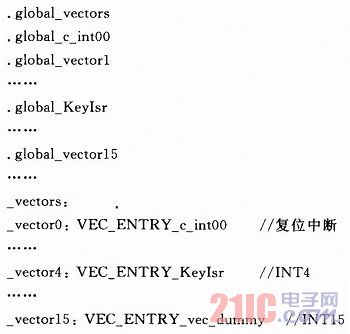

ves dm642.a(chǎn)sm是DM642的中斷向量表文件,聲明中斷函數(shù)名稱及與中斷編號的映射關(guān)系,KeyIsr是INT4對應(yīng)的按鍵中斷響應(yīng)函數(shù),其主要代碼如下:

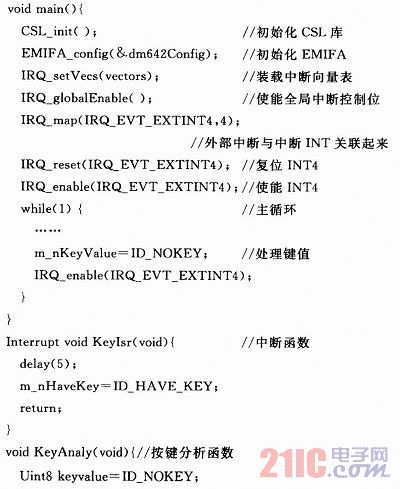

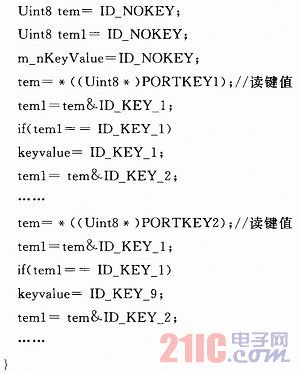

main.c是鍵盤電路的主程序,包括添加CSL庫文件的頭文件、定義按鍵狀態(tài)寄存器的端口地址及按鍵的MASK、初始化設(shè)置EMIFA接口、按鍵分析函數(shù)。主要代碼如下:

4 系統(tǒng)調(diào)試

為了調(diào)試程序,需要把main.c、boot.a(chǎn)sm、ves_dm642.a(chǎn)sm、key.cmd文件添加到項目Key.pjt中。同時,需要設(shè)置Build Options中的Compiler和Linker屬性頁,最后編譯、鏈接、下載。通過設(shè)置斷點和探針來進(jìn)行軟件模擬調(diào)試。CCS仿真表明,程序能根據(jù)硬件設(shè)計的要求讀取按鍵的鍵值并進(jìn)行按鍵狀態(tài)的分析,達(dá)到預(yù)期結(jié)果。

結(jié)語

DM642和CPLD相配合的方法擴(kuò)展鍵盤,DM642的外部中斷監(jiān)控按鍵的狀態(tài),CPLD管理鍵盤電路中的芯片邏輯。充分利用DM642的GPIO口引腳能夠配置為通用輸入/輸出引腳的優(yōu)勢和CPLD豐富的輸入/輸出引腳特性。可以應(yīng)用在以DM642為核心處理器的模式識別和圖像處理系統(tǒng)的人機(jī)交互模塊中,前景廣闊。