引言

1 系統(tǒng)結(jié)構(gòu)

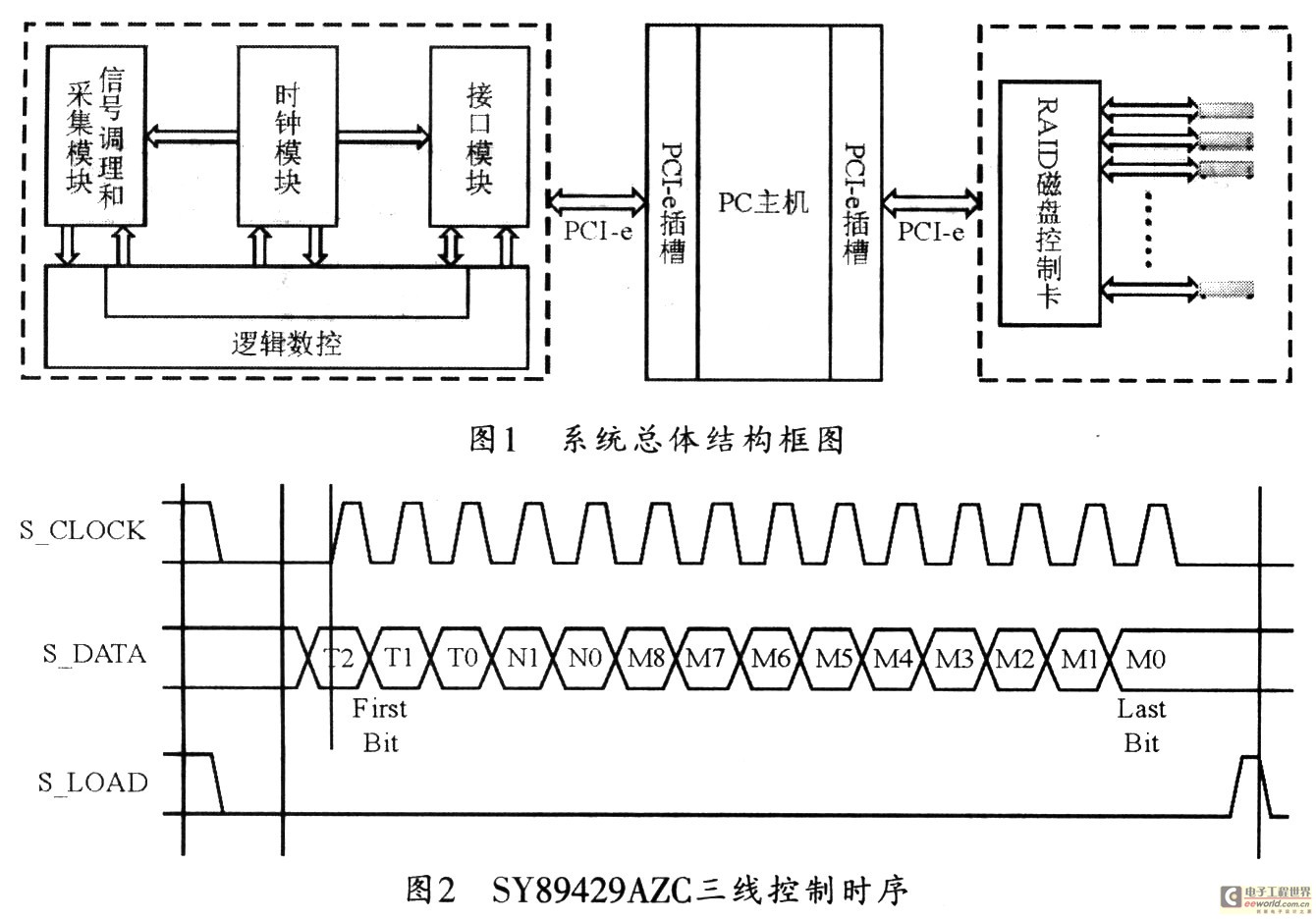

方案總體上分為三個(gè)部分:高速信號(hào)采集卡,、主機(jī)、Raid磁盤陣列,,他們之間可通過PCIExpress總線連接,。其系統(tǒng)結(jié)構(gòu)如圖1所示。

本系統(tǒng)的高速信號(hào)采集卡主要由信號(hào)調(diào)制電路,、數(shù)據(jù)采集模塊,、采集時(shí)鐘控制模塊、數(shù)據(jù)緩存和邏輯控制模塊,、PCI Express總線接口控制等部分組成,。其中邏輯控制模塊負(fù)責(zé)接收來自PCIExpress接口的主機(jī)控制信息以及采樣時(shí)鐘頻率的控制信號(hào),并向系統(tǒng)的其它部分發(fā)送相關(guān)的控制命令,。在進(jìn)行數(shù)據(jù)采集時(shí),,A/D轉(zhuǎn)換芯片的輸出在經(jīng)過信號(hào)處理后,可在數(shù)據(jù)緩存模塊的控制下存入FPGA內(nèi)部FIFO中,;然后再通過PCI Express總線通過主機(jī)內(nèi)存轉(zhuǎn)存到Raid磁盤陣列,。

2 系統(tǒng)實(shí)現(xiàn)

2.1 數(shù)據(jù)采集

本系統(tǒng)中的數(shù)據(jù)轉(zhuǎn)換芯片采用ADI公司生產(chǎn)的AD9430流水型轉(zhuǎn)換器。它是一種單片低功耗12位高速ADC器件,,采用3.3 V單一電源供電,,具有最大的高速轉(zhuǎn)換率(能夠達(dá)到210 MSPS),并在較寬的頻帶范圍內(nèi)仍然具有較好的動(dòng)態(tài)特性,。另外,,片內(nèi)還集成了高性能的采樣保持放大器、參考電壓源和數(shù)據(jù)時(shí)鐘輸出信號(hào),??蔀橄到y(tǒng)提供更加簡(jiǎn)捷的解決方案。

AD9430有兩種數(shù)據(jù)輸出接口模式,,即3.3VCOMS輸出和LVDS輸出,。AD9430正常工作后,每個(gè)時(shí)鐘周期進(jìn)行一次A/D轉(zhuǎn)換,,當(dāng)通過內(nèi)部緩沖采樣保持器和編碼之后,,可將轉(zhuǎn)換結(jié)果鎖存到輸出寄存器。

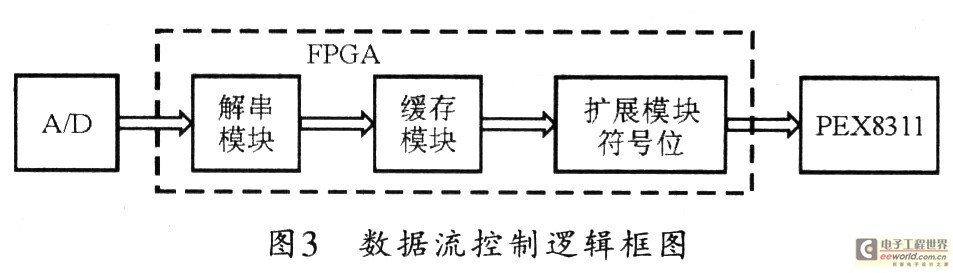

通常高速數(shù)據(jù)采集都是建立在高速高精度采樣的基礎(chǔ)之上,,而高速采樣必須得到高質(zhì)量時(shí)鐘信號(hào)的保障,。采樣時(shí)鐘發(fā)生電路是高速AD采樣的基礎(chǔ)模塊。本系統(tǒng)選用可程控時(shí)鐘源SY89429AZC來產(chǎn)生AD9430的采樣時(shí)鐘,,并通過對(duì)SY89429AZC芯片S_CLOCK,、S_DATA,、S_LOAD三個(gè)引腳信號(hào)線的控制,來程控輸出40MHz~200MHz精確采樣時(shí)鐘,。圖2所示是SY89429AZC的三線控制時(shí)序圖,。

TTL引腳S_DATA為配置串行移位寄存器的輸入端,串行寄存器可在每一個(gè)S_CLOCK信號(hào)的上升沿對(duì)S_DATA信號(hào)進(jìn)行取值,。另有一配置鎖存器可在S_LOAD信號(hào)為高電平時(shí)鎖存串行移位寄存器的內(nèi)容,。這樣,通過設(shè)置S_DATA信號(hào)的值(即T2…T0,,N1,,N0,M8…M0的數(shù)值)以及三信號(hào)線的時(shí)序,,便可控制SY89429AZC時(shí)鐘芯片輸出精確的采樣時(shí)鐘,。

2.2 FPGA邏輯控制

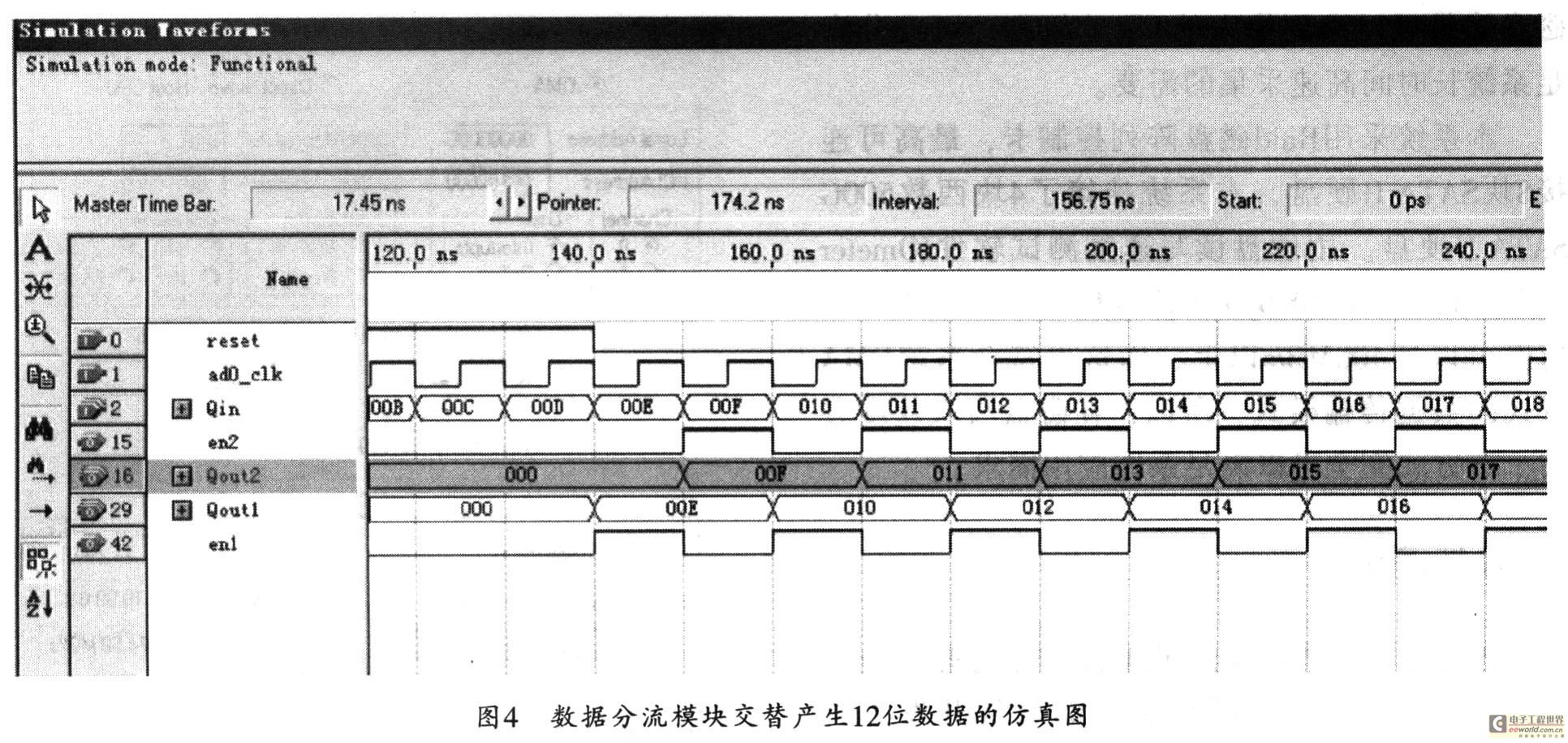

邏輯控制模塊要實(shí)現(xiàn)的主要功能是解析上位機(jī)控制信息并發(fā)送控制命令,同時(shí)要程控采樣時(shí)鐘頻率,,還要對(duì)采集數(shù)據(jù)流進(jìn)行處理和傳輸,。其中數(shù)據(jù)流邏輯控制模塊中的功能組成直接關(guān)系到高速采集信號(hào)能否實(shí)時(shí)可靠的傳輸。圖3所示為數(shù)據(jù)流的邏輯控制結(jié)構(gòu)框圖,。

本設(shè)計(jì)選用Cyclone II系列芯片EP2C5Q208,。此芯片為208腳PQFP封裝,用戶可用I/O資源高達(dá)158個(gè),,差分通道數(shù)為58個(gè),,其內(nèi)部邏輯資源、M4K存儲(chǔ)資源,、內(nèi)部PLL數(shù)量完全能夠滿足本系統(tǒng)設(shè)計(jì)的需要,。

由于AD轉(zhuǎn)換芯片AD94301的采樣精度為12位,而PEX8311接口芯片可支持8位,、16位,、32位數(shù)據(jù)位。因此,,為了更加有效的提高數(shù)據(jù)傳輸?shù)男?,同時(shí)也為了使數(shù)據(jù)采集速率獲得相對(duì)提升,,設(shè)計(jì)中的PEX8311采用32位數(shù)據(jù)位模式進(jìn)行數(shù)據(jù)傳輸,。這樣,在本方案的FPGA數(shù)據(jù)流邏輯控制中,,不僅要進(jìn)行數(shù)據(jù)的緩存以及數(shù)據(jù)傳輸邏輯的控制,,還要進(jìn)行數(shù)據(jù)位的變換擴(kuò)展,即由12位數(shù)據(jù)擴(kuò)展為32位數(shù)據(jù),。為了實(shí)現(xiàn)數(shù)據(jù)位由12位到32位的轉(zhuǎn)換,,應(yīng)先把解串后的12位采樣數(shù)據(jù)進(jìn)行數(shù)據(jù)分流模塊,,以把12位數(shù)據(jù)交替存儲(chǔ)到兩個(gè)FIFO中緩存。圖4所示是經(jīng)數(shù)據(jù)分流模塊交替產(chǎn)生12位數(shù)據(jù)的仿真示意圖,。

高速數(shù)據(jù)采集系統(tǒng)中的數(shù)據(jù)傳輸速率與A/D轉(zhuǎn)換器的采集速度很難保持一致,。為了協(xié)調(diào)數(shù)據(jù)采集與數(shù)據(jù)傳輸之間的速度差異,一般都在兩者之間加入數(shù)據(jù)緩存器進(jìn)行緩沖,,使前端的數(shù)據(jù)采集與數(shù)據(jù)傳輸可以異步工作,。通常的做法是在A/D轉(zhuǎn)換后將數(shù)據(jù)送至外置的FIFO或雙口RAM中進(jìn)行緩存。但這樣無疑會(huì)增加布線密度,,同時(shí)降低數(shù)據(jù)傳輸?shù)目煽啃?。EP2C5Q208 Cyclone II系列FPGA提供了多達(dá)26塊的M4K RAM,而且PCI Ex-press總線的傳輸速率也大于數(shù)據(jù)采集速率,,所以,,可在FPGA內(nèi)部設(shè)置FIFO空間來實(shí)現(xiàn)對(duì)數(shù)據(jù)的緩存。這樣,,從FIFO讀出的兩組12位數(shù)據(jù)經(jīng)過符號(hào)位擴(kuò)展模塊后,,即可擴(kuò)展變換為32位數(shù)據(jù)并由FPGA并行輸出到PCI Express接口模塊。

2.3 PCI Express接口控制

由于數(shù)據(jù)采集速率隨著芯片技術(shù)的進(jìn)步而不斷提高,,而大量的數(shù)據(jù)必須傳輸至主機(jī)進(jìn)行處理,。這些傳輸都由那些將設(shè)備連接到主機(jī)內(nèi)存的數(shù)據(jù)總線完成。因此,,數(shù)據(jù)總線傳輸?shù)乃俾食33蔀檎麄€(gè)數(shù)據(jù)采集系統(tǒng)的瓶頸,,這也是許多儀器帶有昂貴板載內(nèi)存的主要原因之一。而PCI Ex-press的出現(xiàn),,可使測(cè)量設(shè)備至主機(jī)內(nèi)存的數(shù)據(jù)傳輸速率達(dá)到一個(gè)前所未有的高度,。

PCI Express又稱3GIO,即第三代輸入/輸出接口的意思,。串行數(shù)據(jù)傳輸可使數(shù)據(jù)傳輸速率達(dá)到驚人的2.5 Gbps (PCI Express 1.0規(guī)范),,且采用全雙工數(shù)據(jù)傳輸,并可擴(kuò)展為×1,、×4,、×8、×16通道模式,。

以PCI Express×1來計(jì)算,,扣除數(shù)據(jù)校驗(yàn)冗余8 bit\10 bit,有效數(shù)據(jù)傳輸率可以達(dá)到200 Mbyte,,理論上可以提供100 MHz采樣速率和雙字節(jié)以內(nèi)的采樣精度的傳輸帶寬,。

目前,實(shí)現(xiàn)PCI Express總線接口控制的方法有兩種:一種是采用FPGA/CPLD來實(shí)現(xiàn),。目前,,Altera等專業(yè)FPGA公司都提供了多種PCI Express總線接口實(shí)現(xiàn)方案,,并提供了相應(yīng)的MegaCore。但是這種方案設(shè)計(jì)難度大,,調(diào)試?yán)щy,;另一種是采用專用接口芯片,如利用PLX公司的PEX8311來實(shí)現(xiàn)局部總線與PCI Express總線的連接,。目前,,無論從技術(shù)還是成本來看,第二種方案都是比較理想的選擇,。

PEX8311芯片符合PCI Express 1.0基本規(guī)范,,它支持主模式、從模式以及DMA三種數(shù)據(jù)傳輸方式,。PEX8311芯片的主要特性如下:

◇集成有單通道,、全雙工2.5 Gbit/s傳輸?shù)腜CI Express端口;

◇可配置局部總線寬度,,支持8位,、16位和32位的總線方式;

◇支持?jǐn)?shù)據(jù)總線,、地址總線獨(dú)立和復(fù)用總線操作模式,;

◇雙通道高性能的DMA數(shù)據(jù)傳輸可支持?jǐn)?shù)據(jù)塊模式、分散/集中模式,、硬連線數(shù)據(jù)傳輸模式和命令模式,;

◇支持PCI Express規(guī)范中的端點(diǎn)和根復(fù)合體模式;

◇芯片小型封裝,,適合緊湊的電路板設(shè)計(jì),。

本方案中主要使用DMA方式中的命令模式。在命令模式下,,可以通過一對(duì)硬連線“DREQ”和“DACK”來控制傳輸,,每一個(gè)DMA通道都有一對(duì)這樣的信號(hào)。當(dāng)FIFO在被寫滿或讀空時(shí),,命令模式將暫停操作,。而當(dāng)FIFO狀態(tài)改變以后,又可繼續(xù)行進(jìn)數(shù)據(jù)傳輸,。

2.4 Raid磁盤陣列

3 性能測(cè)試

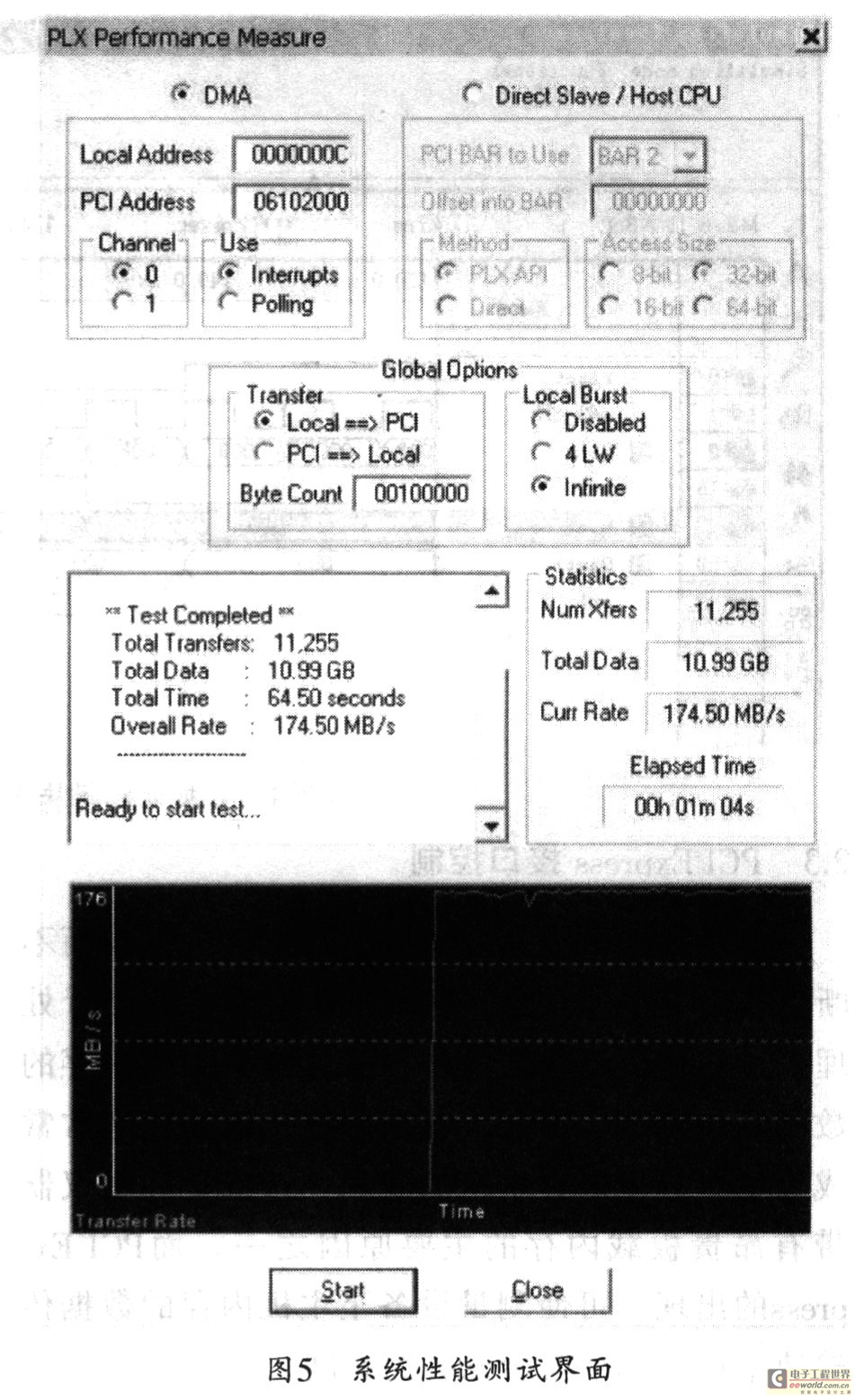

PLX SDK是由PLX公司提供的專門針對(duì)該公司生產(chǎn)的PCI Express接口芯片的軟件開發(fā)工具包。當(dāng)安裝完P(guān)LXSDK軟件后,,再把PEX8311開發(fā)板插入PCI Express插槽中,,就可以用PLXMon對(duì)PEX8311的DMA模式下的數(shù)據(jù)傳輸進(jìn)行設(shè)置和分析。圖5所示是本系統(tǒng)的性能測(cè)試界面圖,。

4 結(jié)束語

基于PCI Express總線技術(shù)和Raid磁盤技術(shù)研制的高速大容量數(shù)據(jù)存儲(chǔ)系統(tǒng),,其最高采樣速率可達(dá)210MHz,存儲(chǔ)容量為2TB,。如果要擴(kuò)展存儲(chǔ)容量,,只需更換Raid磁盤陣列控制卡并增加硬盤數(shù)量即可。通過實(shí)際使用表明,,該系統(tǒng)可以在50MHz采樣率下穩(wěn)定,、可靠、持續(xù)不間斷的完成數(shù)據(jù)的采集和存儲(chǔ),,而且操作方便,,擴(kuò)展性強(qiáng),具有一定的工程應(yīng)用價(jià)值和參考價(jià)值,。