引言

CCD和CMOS圖像傳感器作為固體圖像傳感器領(lǐng)域的競爭對手,兩者在性能表現(xiàn)上各有優(yōu)劣。

相較于CCD圖像傳感器, CMOS圖像傳感器功耗低,結(jié)構(gòu)簡單,集成度高,體積小,成本低,這就使產(chǎn)品的便攜性和可靠性得以極大的提高。由于CMOS圖像傳感器的內(nèi)部結(jié)構(gòu),使其具有高抗輻照,抗干擾能力強,因此在圖像傳感,天文觀測、小衛(wèi)星、星敏感器等應(yīng)用領(lǐng)域表現(xiàn)出極大的應(yīng)用潛力[1]。另外基于CMOS圖像傳感器的加工工藝,可以較容易的制造出大面陣的CMOS體傳感器器件,更加擴(kuò)展了CMOS圖像傳感器的應(yīng)用范圍。

基于CMOS圖像傳感器的視頻采集系統(tǒng)充分的利用了CMOS圖像傳感器的優(yōu)點,采用USB總線供電,即插即用,電路簡單,功耗低,成品體積小,成像清晰,穩(wěn)定,很好的滿足了CMOS圖像采集系統(tǒng)的圖像采集要求。

一.CMOS圖像傳感器的內(nèi)部結(jié)構(gòu)

目前CMOS圖像傳感器主要分為無源象素傳感器(PPS)和有源象素傳感器(APS)[2]。PPS結(jié)構(gòu)簡單,量子效率高,但是缺點是噪聲大,并且不利于向大型陣列發(fā)展;APS在象素中加入了至少一個晶體管來實現(xiàn)對信號的放大和緩沖,改善了PPS的噪聲問題,但惡化了閾值和增益的一致性,也減小了填充系數(shù)。

CMOS圖像傳感器像元結(jié)構(gòu)主要有光敏二極管型無源像素結(jié)構(gòu)、光敏二極管型有源像素結(jié)構(gòu)(見圖1)和光柵型有源像素結(jié)構(gòu),其它特殊結(jié)構(gòu)還有對數(shù)傳輸型、釘扎光敏二極管型、浮柵放大器型等。

圖1 光敏二極管型有源像素結(jié)構(gòu)圖

一個典型的CMOS圖像傳感器通常包含:一個圖像傳感器核心,相應(yīng)的時序邏輯和控制電路、AD轉(zhuǎn)換器、存儲器、定時脈沖發(fā)生器和譯碼器等 [3] 。

定時控制電路用來設(shè)置傳感器的工作模式,產(chǎn)生工作時序,控制數(shù)據(jù)的輸出等。像素采集到的信號在芯片內(nèi)部就經(jīng)過了放大、AD轉(zhuǎn)換、存儲等處理,最后可輸出需要的數(shù)字信號,也可以輸出模擬信號,這給用戶在設(shè)計時提供了較大的靈活性[4]。

二.CMOS圖象視頻采集系統(tǒng)工作原理。

本視頻采集系統(tǒng)整體上按照功能可以分為三個部分:CMOS成像部分、CPLD時序控制部分、USB傳輸部分。

整個圖像采集系統(tǒng)的工作原理如下:通過CPLD發(fā)送正確時序信號給CMOS圖像傳感器,驅(qū)動其正常工作,采取合適的快門方式,并將采集到的圖像數(shù)據(jù)進(jìn)行打包處理,輸出給USB傳輸芯片, USB傳輸芯片再將圖像數(shù)據(jù)傳入主機(jī),并通過上層應(yīng)用程序得到采集到的圖像。

三.系統(tǒng)采用的主要芯片。

3.1 CMOS圖像傳感器芯片IBIS5-A-1300。

本系統(tǒng)CMOS圖像采集芯片選用了Fillfactory公司的IBIS5-A-1300 COMS圖像傳感器芯片,分辨率為1280×1024,全幀采集速率最高可達(dá)27fps,動態(tài)范圍最大達(dá)到100db,6.7 m×6.7 m高填充系數(shù)像元,填充系數(shù)可達(dá)66%,支持卷簾快門和同步快門兩種快門方式。內(nèi)部集成可調(diào)整增益和偏置的輸出放大器,以及40Msamples/s高速A/D轉(zhuǎn)換模塊,A/D量化等級為10bit,可直接輸出模擬信號或數(shù)字信號,內(nèi)部有大量的寄存器和控制器,可以對傳感器的工作狀態(tài)進(jìn)行實時調(diào)整。芯片支持開窗技術(shù)亞采樣技術(shù),根據(jù)實際需要實時提高幀速率[5]。

3.2 數(shù)據(jù)采集芯片 EZ-USB FX2

USB傳輸部分選用了CYPRESS公司的EZ-USB FX2芯片,它是一個USB2.0集成外圍控制器,該芯片支持12M/S的全速傳輸和480M/S的高速傳輸,可以使用(具有)4種USB傳輸方式:控制傳輸、中斷傳輸、塊傳輸和同步傳輸;該器件集成有一個增強型的8051、8.5kB的RAM、4kB的FIFO存儲器、串行接口引擎(SIE)、通用可編程接口(GPIF)、I/O口、數(shù)據(jù)總線、地址總線[6]。

3.3 Altra公司的CPLD控制芯片EPM570。

系統(tǒng)的時序控制芯片采用Atral公司的CPLD控制芯片EPM570。該芯片可以很好的完成系統(tǒng)的時序控制要求。

四.CMOS視頻成像系統(tǒng)設(shè)計。

4.1系統(tǒng)的硬件實現(xiàn)。

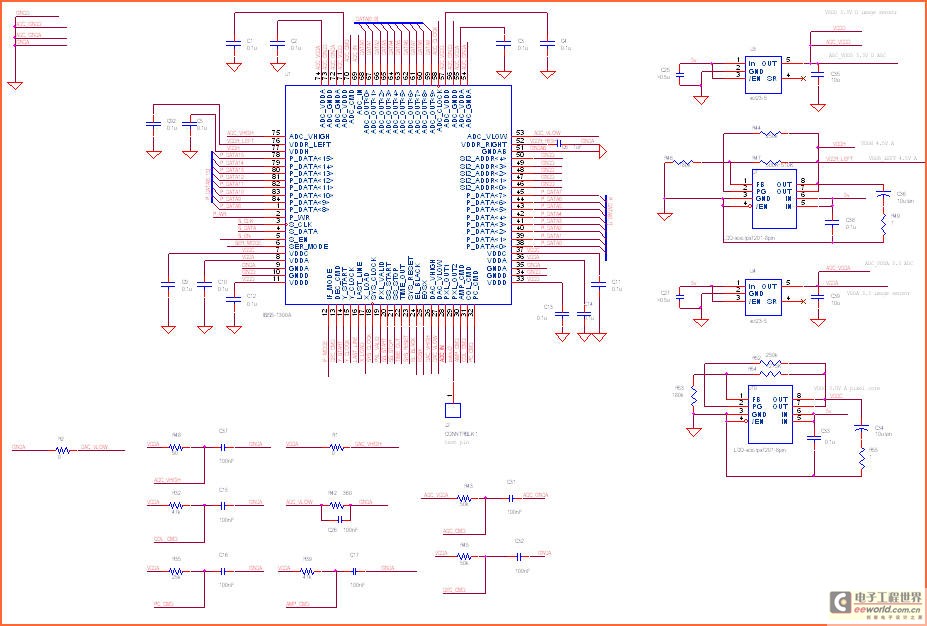

本采集系統(tǒng)為兩塊四層PCB板組合而成,其中一塊為視頻采集板,一塊為USB數(shù)據(jù)傳輸板。其核心CMOS視頻圖像采集板如圖3所示。

圖3:CMOS視頻圖像采集板原理圖

從硬件設(shè)計的原理圖可以看出,CMOS圖像傳感器只需提供少量的電源轉(zhuǎn)換器件即可正常工作,這是因為CMOS圖像傳感器功耗很小,只需采用USB總線提供的5v電壓就可以驅(qū)動其正常工作。另外CMOS圖像傳感器芯片僅需要少數(shù)的幾個外部控制信號即可完成圖像的采集(本系統(tǒng)的控制信號由USB數(shù)據(jù)傳輸板上的CPLD芯片提供),且芯片內(nèi)部集成了輸出放大器,數(shù)模轉(zhuǎn)換模塊,只需修改芯片中的特殊寄存器值即可改變輸出放大器的偏置電壓,增益等參數(shù),這樣就大大降低了硬件設(shè)計的復(fù)雜度和成品的體積,具有很高的應(yīng)用價值。

4.2.系統(tǒng)的時序設(shè)計。

CMOS圖像傳感器結(jié)構(gòu)簡單,內(nèi)部集成度高,因此僅需很少的外部控制信號即可完成視頻圖像的采集輸出

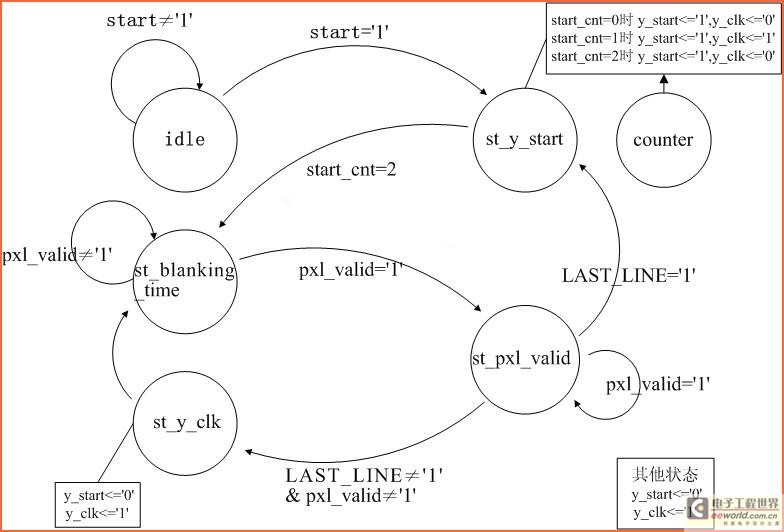

本系統(tǒng)時序采用VHDL硬件描述語言設(shè)計,其核心部分為一個有限狀態(tài)機(jī),具體狀態(tài)關(guān)系如下

系統(tǒng)工作過程如下:當(dāng)系統(tǒng)上電后,CPLD產(chǎn)生復(fù)位信號復(fù)位整個芯片到初始狀態(tài),然后對芯片進(jìn)行并行數(shù)據(jù)注入,向CMOS圖像傳感器的特殊寄存器寫入預(yù)定值,設(shè)置諸如像元積分時間,像素讀出行數(shù),輸出放大器增益等參數(shù)。隨后CPLD給CMOS芯片提供 ss_start信號,標(biāo)志開始像素積分,ss_stop信號結(jié)束像素積分,隨后圖像傳感器即處于可讀出狀態(tài)。向CMOS發(fā)出y_start信號開始一幀圖像的讀出,發(fā)出y_clock信號,開始一行圖像的讀出,當(dāng)CMOS圖像傳感器有像素信號輸出時, pxl_valid引腳信號為高,此時CMOS圖像傳感器正在進(jìn)行一行圖像的輸出,當(dāng)pxl_valid變低時,一行圖像輸出結(jié)束,CPLD再提供下一個y_clock信號,啟動CMOS進(jìn)行下一行圖像的讀出。當(dāng)一幀圖像的最后一行開始讀出時,CMOS芯片的LAST_LINE引腳變高,標(biāo)志一幀圖像讀出的結(jié)束,CPLD再產(chǎn)生下一個ss_start信號,開始下一幀圖像的讀出。這樣,CMOS就在CPLD的時序控制下,正常工作,循環(huán)讀出圖像。系統(tǒng)圖像采集模塊時序仿真波形如圖4

圖4:系統(tǒng)圖像采集模塊時序仿真波形

4.3.USB圖像采集模塊設(shè)計。

本系統(tǒng)的數(shù)據(jù)采集模塊采用cypress公司的EZ_USB FX2 ,USB傳輸芯片,通過編寫固件程序,使該芯片工作在高速批量傳輸方式。本系統(tǒng)采用芯片中的SLAVE FIFO傳輸模式[7],即不通過USB芯片中增強型8051核控制和干預(yù),將數(shù)據(jù)直接通過USB總線,高速的傳輸?shù)絧c機(jī)中。最后利用visual c++6.0編寫上層用戶端程序,采用多線程技術(shù),創(chuàng)建兩個線程:USB傳輸線程和圖像實時顯示線程,實現(xiàn)了在pc機(jī)中的實時圖像顯示。

五.試驗結(jié)果

從試驗拍攝的鑒別率靶圖像可以看到,CMOS圖像傳感器成像清晰,穩(wěn)定,分辨率高。整個CMOS視頻采集系統(tǒng)結(jié)構(gòu)簡單,時序設(shè)計容易,開發(fā)周期短,其成品體積小,外圍器件少,成本低,采用USB總線供電,即插即用,具有很高的實用價值。