摘要:本文介紹了一種基于直接數(shù)字合成(Direct Digital Synthesis,DDS)技術(shù)的超聲波功率源的設(shè)計。詳細介紹了基于現(xiàn)場可編程邏輯門陣列(FPGA)的DDS信號產(chǎn)生電路、功率放大電路以及超聲波功率源與換能器的匹配設(shè)計,與傳統(tǒng)的DDS相比,本系統(tǒng)的功率已經(jīng)達到工業(yè)應(yīng)用的水平。

關(guān)鍵字:直接數(shù)字合成 可編程邏輯門陣列 超聲波

近年來,超聲波在工業(yè)中的應(yīng)用不斷涌現(xiàn),比如超聲波探傷,超聲波清洗等等。伴隨著超聲研究的熱門,如何有效的產(chǎn)生符合要求的超聲波功率源也變的迫切起來,其性能特點直接影響著超聲的研究工作。上述研究需要超聲波具有高分辨率、高穩(wěn)定性、大功率、頻率大范圍可調(diào)等特點,為此,本文提出了一種基于現(xiàn)場可編程邏輯門陣列(FPGA)的DDS技術(shù)用來產(chǎn)生超聲波功率源的方案,并已將其應(yīng)用在實際的聲學(xué)研究中。

一.系統(tǒng)原理及特點

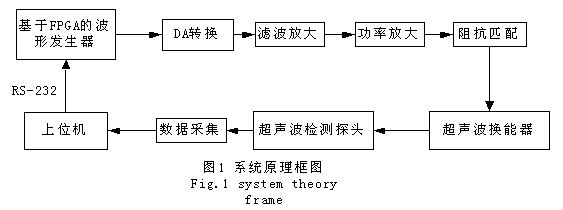

系統(tǒng)原理如圖1所示。用現(xiàn)場可編程邏輯門陣列(FPGA)芯片,通過直接數(shù)字頻率合成(DDS)技術(shù)產(chǎn)生頻率為1kHz~100kHz的波形信號;功率放大采用功放模塊;功率放模塊的輸出通過輸出變壓器和電感組成的匹配網(wǎng)絡(luò)驅(qū)動壓電換能器激發(fā)超聲波。

本系統(tǒng)的主要特點有 :

(1)用數(shù)字DDS技術(shù)產(chǎn)生波形信號,分辨率高、穩(wěn)定性好、頻率范圍大,系統(tǒng)頻率不會隨工作時間出現(xiàn)漂移。

(2)功率放大功放模塊,系統(tǒng)性能穩(wěn)定,功率可達500W左右。

(3)系統(tǒng)通過上位機串行口輸入控制數(shù)據(jù)或接收反饋,操作靈活方便。

二.系統(tǒng)硬件實現(xiàn)

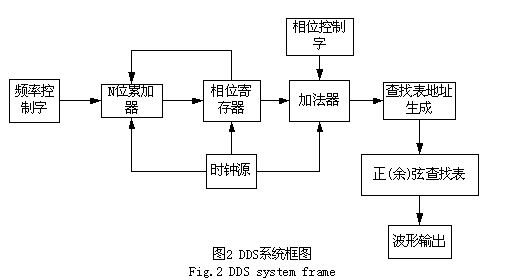

2.1 DDS原理及電路實現(xiàn)  DDS技術(shù)是一種用數(shù)字控制信號的相位增量技術(shù),具有頻率分辨率高、穩(wěn)定性好、可靈活產(chǎn)生多種信號的優(yōu)點。基于DDS的波形發(fā)生器是通過改變相位增量寄存器的值△phase(每個時鐘周期的度數(shù))來改變輸出頻率的。如圖2所示,每當(dāng)N位全加器的輸出鎖存器接收到一個時鐘脈沖時,鎖存在相位增量寄存器中的頻率控制字就和N位全加器的輸出相加。在相位累加器的輸出被鎖存后,它就作為波形存儲器的一個尋址地址,該地址對應(yīng)的波形存儲器中的內(nèi)容就是一個波形合成點的幅度值,然后經(jīng)D/A轉(zhuǎn)換變成模擬值輸出。當(dāng)下一個時鐘到來時,相位累加器的輸出又加一次頻率控制字,使波形存儲器的地址處于所合成波形的下一個幅值點上。最終,相位累加器檢索到足夠的點就構(gòu)成了整個波形。

DDS技術(shù)是一種用數(shù)字控制信號的相位增量技術(shù),具有頻率分辨率高、穩(wěn)定性好、可靈活產(chǎn)生多種信號的優(yōu)點。基于DDS的波形發(fā)生器是通過改變相位增量寄存器的值△phase(每個時鐘周期的度數(shù))來改變輸出頻率的。如圖2所示,每當(dāng)N位全加器的輸出鎖存器接收到一個時鐘脈沖時,鎖存在相位增量寄存器中的頻率控制字就和N位全加器的輸出相加。在相位累加器的輸出被鎖存后,它就作為波形存儲器的一個尋址地址,該地址對應(yīng)的波形存儲器中的內(nèi)容就是一個波形合成點的幅度值,然后經(jīng)D/A轉(zhuǎn)換變成模擬值輸出。當(dāng)下一個時鐘到來時,相位累加器的輸出又加一次頻率控制字,使波形存儲器的地址處于所合成波形的下一個幅值點上。最終,相位累加器檢索到足夠的點就構(gòu)成了整個波形。

DDS的輸出信號頻率由下式計算:

Fout=(△phase×FCLK)/2N (1)

DDS的頻率分辨率定義為:

Fout=FCLK/2N (2)

由于基準時鐘的頻率一般固定,因此相位累加器的位數(shù)決定了頻率分辨率,位數(shù)越多,分頻率越高。

2.2 DDS的FPGA實現(xiàn)

FPGA(現(xiàn)場可編程邏輯門陣列)是從80年代中期開始出現(xiàn)的一種新的可編程器件,它們的編程方式先進高速,可以在線編程修改,一般工作頻率可以達到100MHz,所以在數(shù)字電路設(shè)計領(lǐng)域得到越來越廣泛的應(yīng)用。本系統(tǒng)中采用Altera公司的cyclone系列的FPGA進行DDS的設(shè)計,采用的芯片是EP1C3T144C8。

(1)相位字寄存器

它是一個24位的并行輸入并行輸出寄存器,用來存放24位的相位值,即頻率控制字,系統(tǒng)工作時,可以通過上位機的串口輸入頻率控制字。

(2)相位累加器

相位累加器用于對代表頻率的相位字進行累加運算,相位字的值決定了輸出信號的頻率。

如圖3,本系統(tǒng)中的累加器采用的是24位的結(jié)構(gòu),如果直接采用很寬位數(shù)的加法器構(gòu)成累加器,則加法器的延時會大大的限制累加器的操作速度,所以采用的是3個8位的累加器級連的結(jié)構(gòu),每一級采用一個小的累加器實現(xiàn)部分位的累加,然后再將進位值傳給下一級做進一步的累加,從而提高了系統(tǒng)的運算速度。  (3)查找表的結(jié)構(gòu)

(3)查找表的結(jié)構(gòu)

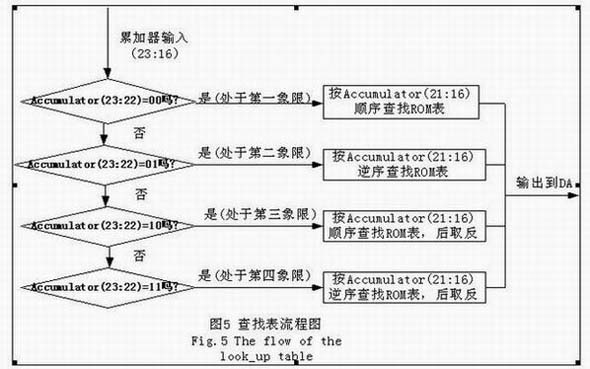

本系統(tǒng)將累加器的高8位作為查表表的地址,其中高兩位用來確定象限。

在FPGA中,正弦表是用ROM來實現(xiàn)的,為了節(jié)省資源,考慮到正弦波的對稱性,實際上只需要存儲正弦值在第一象限的值,如圖4所示。查找表的邏輯流程如圖5。

2.3 DA轉(zhuǎn)換電路的實現(xiàn)

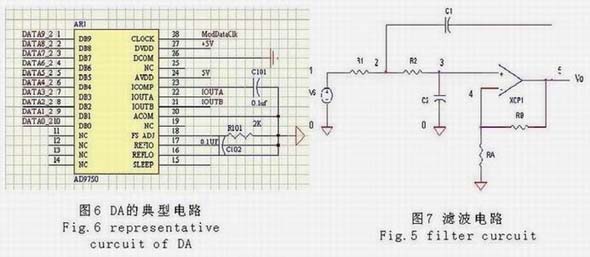

本系統(tǒng)中,考慮到系統(tǒng)在高頻時要求DA的轉(zhuǎn)換速度較快,所以選用了DA公司的AD9750,它是10位的DA芯片,具有125MSPS的轉(zhuǎn)換速度,其典型接法如圖6:

2.4濾波放大及阻抗匹配的實現(xiàn)

考慮到系統(tǒng)中的超聲波的頻率范圍大概處于1k至100k之間,所以前向濾波采用的是Sallen-Key Low-Pass Filter濾波器,其電路結(jié)構(gòu)如圖7所示。

為了使系統(tǒng)能高效穩(wěn)定的工作,我們選用了集成功率放大模塊D-500W。

在超聲波功率源的設(shè)計中,發(fā)生器與換能器的匹配設(shè)計非常重要,在很大程度上決定了超聲設(shè)備能否正常、高效地工作。超聲波發(fā)生器與換能器的匹配包括兩個方面:阻抗匹配和調(diào)諧匹配。阻抗匹配使換能器的阻抗變換為最佳負載,即起阻抗變換作用。調(diào)諧匹配使換能器兩端的電壓和電流同相,從而使效率最高,同時串聯(lián)諧振可以提高換能器兩端電壓,有利于對壓電換能器激勵。  本系統(tǒng)中的阻抗匹配采用的是一個高頻變壓器,功放的輸出經(jīng)過高頻變壓器的耦合以后加在超聲波換能器上,如圖8所示,取得了較好的匹配效果。

本系統(tǒng)中的阻抗匹配采用的是一個高頻變壓器,功放的輸出經(jīng)過高頻變壓器的耦合以后加在超聲波換能器上,如圖8所示,取得了較好的匹配效果。

三 試驗結(jié)果

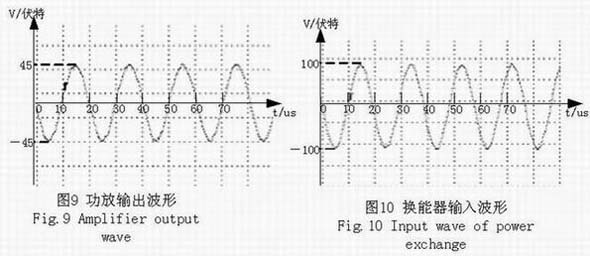

試驗中采用的超聲波換能器的參數(shù)如下:諧振頻率f(KH) 49.05等效阻抗R(Ω)73.9靜電容C0(nf)4.94,F(xiàn)PGA產(chǎn)生的正弦波的頻率設(shè)定位49.5KHz,測得的功放的輸出電壓和換能器兩端的輸入電壓的波形如下圖所示。

可見,系統(tǒng)在高頻下的波形較為穩(wěn)定,且可在較高的功率下連續(xù)工作,獲得了較為完好的波形。