本文介紹了一種選用高性能、低功耗的32位微處理器STM32F103和射頻收發(fā)芯片nRF24L01來設(shè)計(jì)短距離無線數(shù)據(jù)傳輸系統(tǒng)的具體方法。

1 系統(tǒng)設(shè)計(jì)

短距離無線數(shù)傳系統(tǒng)主要由電源管理器AMC7635、微控制器STM32F103、射頻收發(fā)器nrf24l01三部分組成。下面分別介紹其關(guān)鍵電路。

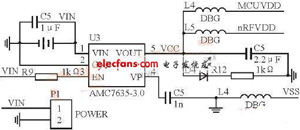

1.1 電源電路

本設(shè)計(jì)的電源采用3.7V鋰電池供電,然后經(jīng)低壓降電源管理芯片AMC7635,以產(chǎn)生3.0V的電壓來為STM32F103和nRF24L01供電,圖1所示是本系統(tǒng)的供電電路。

圖1 系統(tǒng)供電電路

1.2 微控制器電路

微控制器選用帶ARM Cortex -M3內(nèi)核的STM32F103。STM32F103控制器具有高性能、低功耗、低電壓等特性,同時(shí)具有高集成度和易于開發(fā)的優(yōu)勢(shì)。圖2所示是該系統(tǒng)中的微控制器電路。控制器與射頻收發(fā)器nRF24L01的接口采用SPI口來實(shí)現(xiàn),即圖2中SPICS、MOSI、MISO和SCK四條信號(hào)線和CE和INT0兩條信號(hào)線。另外,該控制器還可以擴(kuò)展一路主板RS232口和8路GPIO口輸出。

圖2 微控制器電路

1.3 射頻收發(fā)電路

nRF24L01可工作于2.4GHz~2.5GHz ISM頻段,該收發(fā)器內(nèi)置頻率合成器、功率放大器、晶體振蕩器、調(diào)制器等功能模塊,是一款集成度較高的無線收發(fā)器。nRF24L01的外部電路比較簡(jiǎn)單,而且融合了增強(qiáng)型ShockBurst技術(shù),其中輸出功率和通信頻道可通過程序進(jìn)行配置。同時(shí),該芯片的功耗極低,在以-6dBm的功率發(fā)射時(shí),其工作電流只有9mA;而在接收時(shí),工作電流只有12.3mA。nRF24L01的控制電路可與STM32控制器的SPI口和GPIO口相連接。圖3所示是該芯片組成的射頻收發(fā)電路原理圖。

圖3 射頻收發(fā)電路

2 系統(tǒng)程序設(shè)計(jì)

本系統(tǒng)可在STM32F103上移植UCOSII操作系統(tǒng)。系統(tǒng)程序主要分為主機(jī)的系統(tǒng)初始化程序、鍵盤和顯示程序及射頻收發(fā)器nRF24L01的控制程序三大部分。圖4所示是其軟件程序流程。

圖4 系統(tǒng)程序流程圖

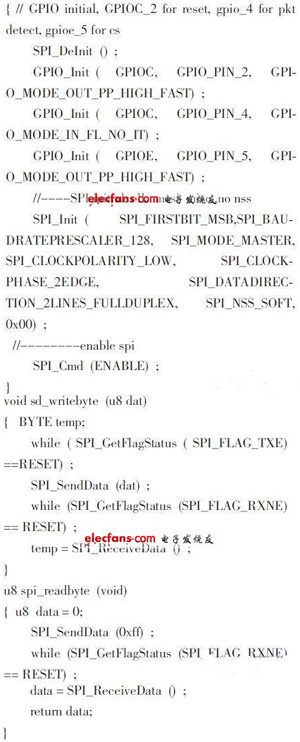

系統(tǒng)程序設(shè)計(jì)的關(guān)鍵是UCOSII操作系統(tǒng)的移植和SPI口通信控制。有關(guān)操作系統(tǒng)的移植,芯片廠商在官網(wǎng)上已有范例提供,本文不再贅述。

下面列出系統(tǒng)SPI初始化及收發(fā)函數(shù)的程序源碼。

void SPI_Initial (void)

當(dāng)然,也可以用GPIO口來實(shí)現(xiàn)SPI通信,但前提是通信速率要求不是很高。由于要通過GPIO口模擬實(shí)現(xiàn)SPI的突發(fā)傳送協(xié)議,而且要兼顧其通用性,故其程序較為復(fù)雜。下面給出通過GPIO口實(shí)現(xiàn)SPI收發(fā)的一般程序:

3 結(jié)束語

經(jīng)現(xiàn)場(chǎng)調(diào)試證明,本文給出的無線數(shù)傳系統(tǒng)具有成本低,速率高,傳輸可靠等優(yōu)點(diǎn)。在實(shí)際應(yīng)用中,還可根據(jù)需要將nRF24LOl組成一對(duì)一、一對(duì)多、多對(duì)多的結(jié)構(gòu)。