摘要:介紹了QDPSK信號的優(yōu)點(diǎn),,并分析了其實(shí)現(xiàn)原理,提出一種QDPSK高性能數(shù)字調(diào)制器的FPGA實(shí)現(xiàn)方案,。采用自頂向下的設(shè)計(jì)思想,,將系統(tǒng)分成串/并變換器、差分編碼器,、邏輯選相電路,、四相載波發(fā)生器等4大模塊,用原理圖輸入,、VHDL語言設(shè)計(jì)和調(diào)用PLL核相結(jié)合的多種設(shè)計(jì)方法,,分別實(shí)現(xiàn)了各模塊的具體設(shè)計(jì),并給出了其在QuartusⅡ環(huán)境下的仿真結(jié)果,。結(jié)果表明,,基于PLL的QDPSK調(diào)制器,設(shè)計(jì)簡單,,便于修改和調(diào)試,,性能穩(wěn)定。

關(guān)鍵詞:QDPSK,;串/并變換,;數(shù)字調(diào)制器;FPGA

FPGA器件(Field Programmable Gate Array)是八十年代中期出現(xiàn)的一種新概念,。利用FPGA技術(shù)設(shè)計(jì)的產(chǎn)品具有重量輕,、體積小、速度快,、保密程度高,、功耗低等特點(diǎn),極大地提高了產(chǎn)品的性價(jià)比和競爭力,,大大縮短了設(shè)計(jì)周期,,減少了設(shè)計(jì)費(fèi)用,降低了設(shè)計(jì)風(fēng)險(xiǎn),。

數(shù)字調(diào)制信號又稱為鍵控信號,,調(diào)制過程可用鍵控的方法由基帶信號對載頻信號的振幅、頻率及相位進(jìn)行調(diào)制。這種調(diào)制的最基本方法有3種:振幅健控(ASK),、頻移鍵控(FSK),、相移鍵控(PSK)。根據(jù)所處理的基帶信號的進(jìn)制不同,,它們可分為二進(jìn)制和多進(jìn)制調(diào)制(M進(jìn)制),。多進(jìn)制數(shù)字調(diào)制與二進(jìn)制相比,其頻譜利用率更高,。其中QPSK(即4PSK)是MPSK(多進(jìn)制相移鍵控)中應(yīng)用較廣泛的一種調(diào)制方式,,該方式廣泛應(yīng)用于衛(wèi)星通信、電纜調(diào)制解調(diào),、視頻會議系統(tǒng),、蜂窩電話和其他數(shù)字通信領(lǐng)域。然而QPSK信號在解調(diào)的時(shí)候易產(chǎn)生相位模糊問題,,即可能會產(chǎn)生0,、π/2,、π,、3π/2 4種相位模糊。解決的方法就是采用四進(jìn)制差分相位鍵控(QDPSK),,對于相對移相,,基帶信號是由相鄰兩碼元相位的變化來表示,它與載波相位無直接關(guān)系,,即使采用同步解調(diào)也不存在相位模糊問題,,因此在實(shí)際設(shè)備中相對移相得到了廣泛運(yùn)用。本文研究了基于FPGA的QDPSK調(diào)制電路的實(shí)現(xiàn)方法,,重點(diǎn)闡述了串/并變換,、差分編碼、四相載波發(fā)生器等電路的原理與實(shí)現(xiàn)方法,,并給出了其在QuartusⅡ環(huán)境下的仿真結(jié)果,。

1 QDPSK調(diào)制原理

1.1 四相絕對移相鍵控(QDPSK)

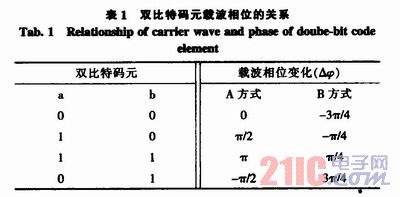

相對調(diào)相(相對移相),即DPSK(Differential Phase Shift Keying),,也稱為差分調(diào)相,,這種方式用載波相位的相對變化來傳送數(shù)字信號,即利用前后碼之間載波相位的變化表示數(shù)字基帶信號,。在QDPSK信號中,,若以前一雙比特碼元相位作為參考,并令△φ為當(dāng)前雙比特碼元的相位差,,則可得到雙比特碼元與載波相位變化關(guān)系如表1所示,,從表中可以看出,A方式中,載波相位互差π/2,,實(shí)現(xiàn)比較容易,,因此采用A方式。

1.2 QDPSK的調(diào)制方法

QDPSK的產(chǎn)生方法可采用調(diào)相法和相位選擇法,。圖1為相位選擇法產(chǎn)生QDPSK的原理框圖,。在圖1中,四相載波發(fā)生器分別送出調(diào)相需的4種頻率相同,、相位互差π/2的載波,,輸入二進(jìn)制數(shù)字基帶信號經(jīng)串/并變換為四進(jìn)制數(shù)字基帶信號,經(jīng)差分編碼變?yōu)樗倪M(jìn)制差分碼,,邏輯選相電路根據(jù)差分編碼后的雙比特碼cd,,每隔時(shí)間間隔T選擇輸出其中一種相位的載波。虛線內(nèi)的信號均為數(shù)字信號,,可直接利用FPGA來實(shí)現(xiàn)ODPSK調(diào)制,。

2 QDPSK數(shù)字調(diào)制器的實(shí)現(xiàn)

2.1 串/并轉(zhuǎn)換、相位選擇的實(shí)現(xiàn)

順序輸入的二進(jìn)制信息經(jīng)過串/并變換器,,變換成速率減半的雙比特序列,,可采用2個(gè)D觸發(fā)器來實(shí)現(xiàn),其原理如圖2所示,。其中DFFinst和DFFinst3構(gòu)成一個(gè)兩位移位寄存器,,將串行輸入信號變成并行輸出信號;DFFinst4和NOTinst8構(gòu)成二分頻器,,實(shí)現(xiàn)速率減半,;DFFinst1和DFFinst2為鎖存器,使信號同步輸,。圖3為串/并變換器s-p的仿真結(jié)果,,其中AB為變換后的雙比特碼元。由圖可以看出,,當(dāng)輸入DataAB為01010101時(shí),,在延時(shí)約80 ns后,輸出DataA為0000,。DataB為1111,。邏輯選相電路主要實(shí)現(xiàn)在4種不同的相位中選擇一種輸出,即四選一電路,,電路結(jié)構(gòu)簡單,,用VHDL語言或組合邏輯電路均可實(shí)現(xiàn),這里不作祥細(xì)介紹,。

2.2 差分編碼器的實(shí)現(xiàn)

差分編碼器的功能就是實(shí)現(xiàn)絕對碼變換為相對碼,,在相碼中,,1、0分別用相鄰碼元電平是否發(fā)生跳變來表示,。若用相鄰電平發(fā)生跳變來表示碼元1,,則稱為傳號差分碼,記做NRZ碼,。絕對碼一相對碼之間的關(guān)系為:

![]()

由表達(dá)式(1)可得到其變換電路如圖4所示,。

采用VHDL設(shè)計(jì)的主體代碼如下:

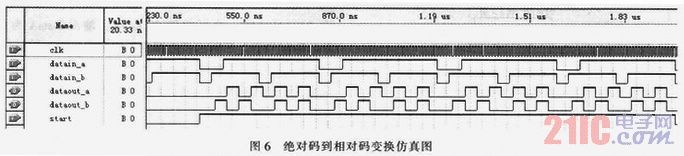

經(jīng)編譯后,可生成如圖5所示元件,,元件名為QDPSK_PL,,其中clk為系統(tǒng)時(shí)鐘;start為同步信號,,高電平有效,;datain_a和datain_b分別兩路輸入信號;dataout_a和dataout_b分別兩路輸出信號,,其波形仿真圖如圖6所示,。由圖6可以得到:當(dāng)start為低電平時(shí),兩路輸出信號都為0,;當(dāng)start信號為高電平時(shí),,對輸入信號(datain_a)有:datain_a=011111111001,此時(shí)dataout_a=010101010001,,對輸入信號(datain_b)有:datain_b=011110111101,,此時(shí)Dataout_b=010100101001,,由此可以得出,,元件QDSP_PL實(shí)現(xiàn)了由絕對碼到相對碼的變換。

2.3 四相載波發(fā)生器的實(shí)現(xiàn)

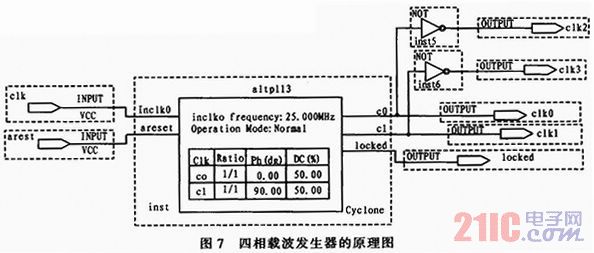

由圖3可知,,四相載波發(fā)生器主要產(chǎn)生4種頻率相同,、相位互差π/2的載波信號。實(shí)現(xiàn)四相載波有很多種不同方法,??上扔烧袷庪娐樊a(chǎn)生一定頻率的信號,再利用RC移相電路得到不同相位的波形,;也可以利用NCO的Implementation項(xiàng)目設(shè)置啟用相位調(diào)制功能,,通過設(shè)置相位調(diào)制精度輸出4種不同的相位。該系統(tǒng)利用QuartusⅡ5.2內(nèi)部的PLL直接產(chǎn)生clk0和elk1兩路頻率相同,、相位相差π/2的信號,,再用2個(gè)非門分別對clk0和clk1取反,得到clk2和clk3,。這樣就可以實(shí)現(xiàn)四相載波發(fā)生器的功能,,其原理圖如圖7所示,,圖8為輸出波形仿真圖。

把上述各部分所生的symbol在QuartusⅡ5.2提供的BlockDiagram/SchematicFile中用Graphic Editor編輯連接起來,,就形成了圖1的虛線所示的部分,,編譯后進(jìn)行整體模塊仿真,經(jīng)過器件編程,,可將整體模塊程序燒寫到合適的FPGA芯片中,,再配以相應(yīng)的D/A器件及其他外圍電路,調(diào)試后即完成設(shè)計(jì),。

3 結(jié)束語

用FPGA來實(shí)現(xiàn)QDPSK信號發(fā)生器,,電路簡單,設(shè)計(jì)靈活,,便于修改和調(diào)試,,可靠性高。另外,,Ahera公司的QuartusⅡ5.2應(yīng)用軟件具有較強(qiáng)大的開放性和綜合性,。它可以利用其他各種EDA資源以及先進(jìn)的設(shè)計(jì)方法,使其功能更加完善和強(qiáng)大,。它可以實(shí)現(xiàn)從簡單的接口電路設(shè)計(jì)到復(fù)雜的狀態(tài)機(jī),,甚至“Sys-temon Chip”。它的可編程特性帶來了電路設(shè)計(jì)的靈活性,,縮短了產(chǎn)品的“Time ToMarket”,。

本文作者創(chuàng)新點(diǎn):基于PLL提出了一種QDPSK的FPGA實(shí)現(xiàn)方案,采用自頂向下的設(shè)計(jì)思想,,將系統(tǒng)分成串/并變換器,、差分編碼器、邏輯選相電路,、四相載波發(fā)生器等4大模塊,,用原理圖輸入、VHDL語言設(shè)計(jì)和調(diào)用PLL核相結(jié)合的多種設(shè)計(jì)方法,,分別實(shí)現(xiàn)了各模塊的具體設(shè)計(jì),,該方案極大地簡化了系統(tǒng)的設(shè)計(jì)過程和難度,甚至可做到不需要編寫任何程序?qū)崿F(xiàn)QDPSK調(diào)制器的設(shè)計(jì),。