嵌入式系統(tǒng)(Embedded system),是一種“完全嵌入受控器件內(nèi)部,為特定應(yīng)用而設(shè)計(jì)的專用計(jì)算機(jī)系統(tǒng)”,根據(jù)英國(guó)電器工程師協(xié)會(huì)( U.K. InstitutiON of Electrical Engineer)的定義,嵌入式系統(tǒng)為控制、監(jiān)視或輔助設(shè)備、機(jī)器或用于工廠運(yùn)作的設(shè)備。與個(gè)人計(jì)算機(jī)這樣的通用計(jì)算機(jī)系統(tǒng)不同,嵌入式系統(tǒng)通常執(zhí)行的是帶有特定要求的預(yù)先定義的任務(wù)。由于嵌入式系統(tǒng)只針對(duì)一項(xiàng)特殊的任務(wù),設(shè)計(jì)人員能夠?qū)λM(jìn)行優(yōu)化,減小尺寸降低成本。由于嵌入式系統(tǒng)通常進(jìn)行大量生產(chǎn)。所以單個(gè)的成本節(jié)約,能夠隨著產(chǎn)量進(jìn)行成百上千的放大。

PCI總線是現(xiàn)今最為流行的工業(yè)控制總線之一。它廣泛地應(yīng)用在計(jì)算機(jī)中,很多目標(biāo)嵌入式設(shè)備中的解決方案都包含了PCI總線。這里介紹一種基于CPLD(復(fù)雜可編程邏輯器件)的PCI總線仲裁器的設(shè)計(jì)方法,可以為系統(tǒng)量身定制適合于系統(tǒng)本身的PCI總線仲裁器。

1 PCI總線仲裁簡(jiǎn)介

1.1 PCI總線的仲裁原理

PCI總線是一種共享式的總線,可以連接多個(gè)主設(shè)備,但由于數(shù)據(jù)傳輸?shù)莫?dú)占性,每一時(shí)刻只能由一個(gè)主設(shè)備占用總線。因此,為了有效地利用PCI總線寬帶,必須設(shè)置一個(gè)總線仲裁器,按照一定的算法協(xié)調(diào)系統(tǒng)中各個(gè)主設(shè)備的操作。

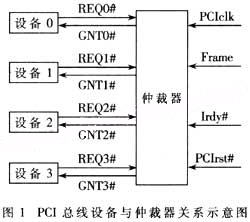

PCI總線仲裁的裁決過程可以在PCI傳輸期間完成,并不占用PCI總線的寬帶,這稱為隱式仲裁,即需要發(fā)起PCI操作的設(shè)備可以隨時(shí)發(fā)出請(qǐng)求REQ#,PCI仲裁器立即批準(zhǔn)該請(qǐng)求被給出GNT#,但是真正的傳輸操作一定要等到當(dāng)前傳輸完成,即總線空閑后才可以開始,圖1描述了PCI總線設(shè)備與仲裁器的關(guān)系。

1.2 PCI總線仲裁規(guī)則約定

(1)仲裁器的仲裁算法必須保證所有的設(shè)備都能得到授權(quán)的機(jī)會(huì),否則將會(huì)出現(xiàn)某個(gè)優(yōu)先級(jí)低的設(shè)備永遠(yuǎn)不能占有總線進(jìn)行事務(wù)操作的情況。

(2)如果FRAME無(wú)效,GNT可以在任意時(shí)間撤銷,以便服務(wù)于另一個(gè)主設(shè)備或者作為對(duì)主設(shè)備車REQ的響應(yīng)。

(3)如果GNT信號(hào)被撤銷但FRAME有信號(hào),當(dāng)前的總線正在傳輸數(shù)據(jù),則操作合法。

(4)如果總線不處于空閑狀態(tài),則允許一個(gè)GNT的撤銷和另一個(gè)GNT的發(fā)生在同一個(gè)周期,如果處在空閑狀態(tài),則要求一個(gè)GNT撤銷到下一個(gè)GNT的發(fā)出之間必須有一個(gè)時(shí)鐘周期間隔,否則可能會(huì)在AD線和PAR線上出現(xiàn)沖突。

(5)GNT信號(hào)的每次發(fā)出,只限于相應(yīng)的總線主控器可以使用總線進(jìn)行一次總線操作。仲裁器會(huì)按照特定的仲裁算法來(lái)決定是否仍判給該主設(shè)備。

(6)一個(gè)主控器可以在任意時(shí)刻撤銷其REQ信號(hào),REQ信號(hào)一旦撤銷,仲裁器將認(rèn)為該設(shè)備不再請(qǐng)求使用總線,因而撤銷其GNT信號(hào)。

(7)如果當(dāng)前的主控器在它的GNT信號(hào)發(fā)出后,持續(xù)16個(gè)空閑周期還沒有開始總線操作,則仲裁器視其為超時(shí),仲裁器可以在任意時(shí)刻撤銷GNT信號(hào)。

1.3 PCI總線仲裁的算法

目前,應(yīng)用于PCI總線仲裁的算法主要有固定優(yōu)先級(jí)算法和動(dòng)態(tài)優(yōu)先級(jí)算法兩種,在固定優(yōu)先級(jí)算法中,各個(gè)設(shè)備的優(yōu)先級(jí)是事先確定好的,仲裁器針對(duì)事先設(shè)定好的優(yōu)先級(jí)為每個(gè)設(shè)備分配使用權(quán)。最常用的是循環(huán)優(yōu)先級(jí)算法,即每次仲裁授權(quán)后將排隊(duì)中的設(shè)備優(yōu)先級(jí)加1。因其算法簡(jiǎn)單,且對(duì)大部分應(yīng)用都十分有效。

1.4 總線停靠

當(dāng)PCI總線空閑時(shí),一個(gè)設(shè)備從申請(qǐng)總線到被授權(quán)使用,最小也需要2個(gè)時(shí)鐘周期,這對(duì)于PCI總線是一種浪費(fèi)。因此仲裁器通常選中一個(gè)最經(jīng)常占用總線的設(shè)備,PCI總線空閑時(shí)將GNT#賦予它,這叫做總線停靠。當(dāng)總線空閑時(shí),該設(shè)備需要占用總線時(shí)可馬上得到批準(zhǔn)。

2 雙主設(shè)備PCI總線仲裁器的實(shí)現(xiàn)

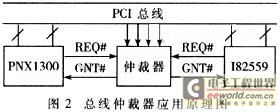

下面描述了一個(gè)具有兩個(gè)設(shè)備的總線仲裁器的硬件實(shí)現(xiàn),其一為TriMedia嵌入式DSPCPU PNX1300,其二為Intel i82559網(wǎng)絡(luò)控制器,系統(tǒng)結(jié)構(gòu)如圖2所示。

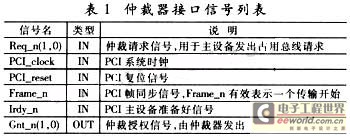

該仲裁器的接口信號(hào)如表1所示。

為了設(shè)計(jì)方便起見,在程序中設(shè)計(jì)三類狀態(tài)機(jī):總線狀態(tài)狀態(tài)機(jī)、總線主設(shè)備查詢狀態(tài)機(jī)、仲裁狀態(tài)機(jī)。

2.1 總線狀態(tài)狀態(tài)機(jī)

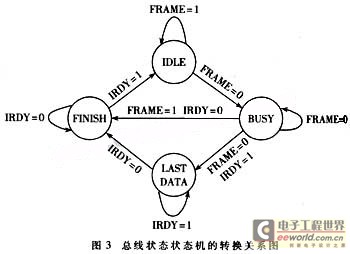

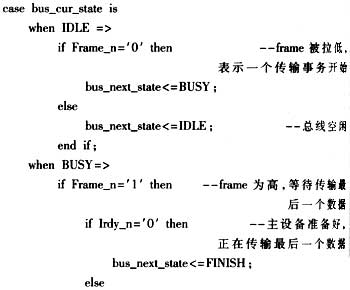

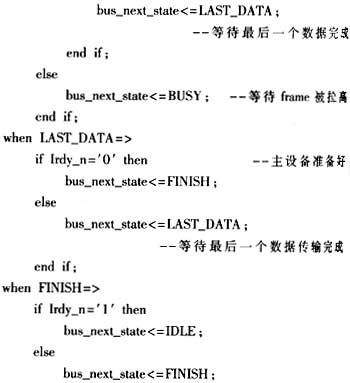

總線狀態(tài)狀態(tài)機(jī)用于記錄總線事務(wù)的狀態(tài),定義如下:

type bus_state is(IDLE,BUSY,LAST_DATA,F(xiàn)INISH)

四種狀態(tài)分別表示總線空閑、忙、最后一個(gè)數(shù)據(jù)傳輸期以及傳輸完成。狀態(tài)圖如圖3。

下面是以VHDL代碼形式實(shí)現(xiàn)的該狀態(tài)機(jī)的狀態(tài)轉(zhuǎn)換關(guān)系。

2.2總線主設(shè)備查詢狀態(tài)機(jī)

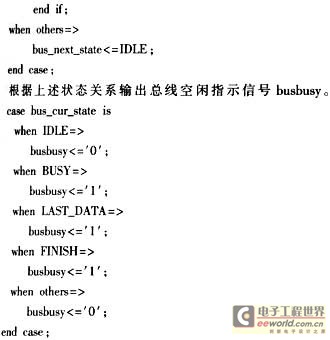

總線主設(shè)備查詢狀態(tài)機(jī)用來(lái)決定當(dāng)前是否需要重新指定一個(gè)主設(shè)備,重新指定一個(gè)主設(shè)備的條件是:(1)當(dāng)前被授權(quán)的設(shè)備已開始傳輸;(2)當(dāng)前被授權(quán)的設(shè)備沒有開始傳輸并且超時(shí)。將主設(shè)備查詢狀態(tài)分為IDLE、GNT1、GNT2、WAIT_NOBUSY和WAIT_BUSY2五個(gè)狀態(tài),并設(shè)置計(jì)數(shù)器count,當(dāng)總線上某個(gè)設(shè)備被授權(quán),16個(gè)周期仍然沒有開始操作,count超過16,被視為超時(shí),仲裁器可以撤銷其仲裁授權(quán),并傳授其他設(shè)備,程序根據(jù)這個(gè)狀態(tài)機(jī)的輸出結(jié)果決定仲裁狀態(tài)機(jī)是否改變。

狀態(tài)轉(zhuǎn)換如圖4所示,狀態(tài)機(jī)描述的VHDL代碼略。

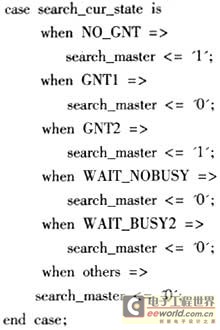

主設(shè)備查詢狀態(tài)機(jī)的輸出信號(hào)search_master:

該狀態(tài)機(jī)的驅(qū)動(dòng)條件是由總線狀態(tài)狀態(tài)機(jī)的輸出結(jié)果、仲裁狀態(tài)機(jī)的狀態(tài)以及計(jì)數(shù)器產(chǎn)生的超時(shí)信號(hào)組成。該狀態(tài)機(jī)的輸出search_master作為仲裁狀態(tài)機(jī)狀態(tài)轉(zhuǎn)換使能信號(hào),該信號(hào)有效時(shí),仲裁狀態(tài)機(jī)才進(jìn)行當(dāng)前狀態(tài)的改變。

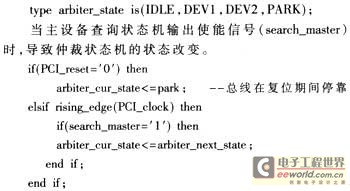

2.3 仲裁狀態(tài)機(jī)

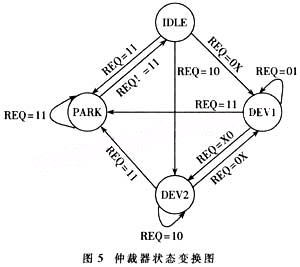

仲裁狀態(tài)機(jī)表示總線仲裁器的狀態(tài),定義如下:

狀態(tài)轉(zhuǎn)變過程如圖5所示,狀態(tài)機(jī)描述的VHDL代碼略。

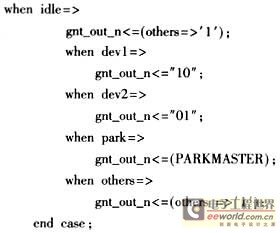

仲裁器根據(jù)仲裁狀態(tài)機(jī)當(dāng)前狀態(tài)控制仲裁授權(quán)信號(hào)的給出。

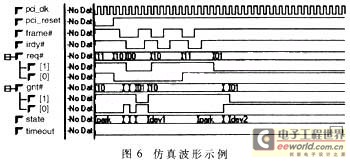

2.4仿真波形圖

由圖6可看出,測(cè)試文件模擬了一個(gè)設(shè)備申請(qǐng)和兩個(gè)設(shè)備同時(shí)申請(qǐng)的情況,并給出了總線授權(quán)信號(hào),驗(yàn)證了仲裁器邏輯的正確性。

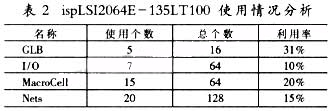

2.5 資源占用情況分析

可編程邏輯器件使用Lattice公司的ispLSI2064E135LT100,在ispLever中綜合本例程序,結(jié)果如表2。

綜合后的延遲分析顯示,該邏輯的時(shí)鐘周期最小為7.5ns,即該邏輯可以運(yùn)行在133MHz以下的系統(tǒng)中,完全可以勝任33MHz PCI總線的仲裁工作。