以FPGA 芯片為載體,, 通過QuartusII 的LPM_ROM 模塊和VHDL 語言為核心設(shè)計一個多功能信號發(fā)生器,,根據(jù)輸入信號的選擇可以輸出遞增鋸齒波、遞減鋸齒波,、三角波,、階梯波和方波等5 種信號,通過QuartusII 軟件進(jìn)行波形仿真,、定時分析,,仿真正確后,利用實驗板提供的資源,,下載到芯片中實現(xiàn)預(yù)定功能,。

信號發(fā)生器又稱為波形發(fā)生器, 是一種常用的信號源,,廣泛應(yīng)用于電子電路,、通信、控制和教學(xué)實驗等領(lǐng)域,。它是科研及工程實踐中最重要的儀器之一,, 以往多用硬件組成,,系統(tǒng)結(jié)構(gòu)比較復(fù)雜,,可維護(hù)性和可操作性不佳。隨著計算機(jī)技術(shù)的發(fā)展,,信號發(fā)生器的設(shè)計制作越來越多的是用計算機(jī)技術(shù),,種類繁多,,價格、性能差異很大,。用FPGA 或CPLD 來實現(xiàn),,它的優(yōu)點是可以進(jìn)行功能仿真,而且FPGA 和CPLD 的片內(nèi)資源豐富,,設(shè)計的流程簡單,。用FPGA 所構(gòu)成的系統(tǒng)來產(chǎn)生波形信號,,這個系統(tǒng)既能和主機(jī)系統(tǒng)相連,用相應(yīng)的上層軟件展示波形信號,, 又方便程序的編寫,, 而且還有A/D0809接口可以產(chǎn)生模擬信號的輸出和外面的示波器相連。

1 正弦信號發(fā)生器的LPM 定制

正弦信號發(fā)生器由計數(shù)器或地址發(fā)生器(6 位),、正弦信號數(shù)據(jù)ROM (6 位地址線,,8 位數(shù)據(jù)線, 含有64 個8 位數(shù)據(jù),, 一個周期),、原理圖頂層設(shè)計和8 位D/A ( 實驗中用DAC0832 代替)。

其框圖如圖1 所示,。其中信號產(chǎn)生模塊將產(chǎn)生所需的各種信號,這些信號的產(chǎn)生可以有多種方式,,如用計數(shù)器直接產(chǎn)生信號輸出,,或者用計數(shù)器產(chǎn)生存儲器的地址,在存儲器中存放信號輸出的數(shù)據(jù),。信號發(fā)生器的控制模塊可以用數(shù)據(jù)選擇器實現(xiàn),, 用8 選1 數(shù)據(jù)選擇器實現(xiàn)對5 種信號的選擇。

圖1 信號發(fā)生器結(jié)構(gòu)框圖

最后將波形數(shù)據(jù)送入D/A 轉(zhuǎn)換器,,將數(shù)字信號轉(zhuǎn)換為模擬信號輸出,。用示波器測試D/A 轉(zhuǎn)換器的輸出,可以觀測到5 種信號的輸出,。

1.1 定制初始化數(shù)據(jù)文件

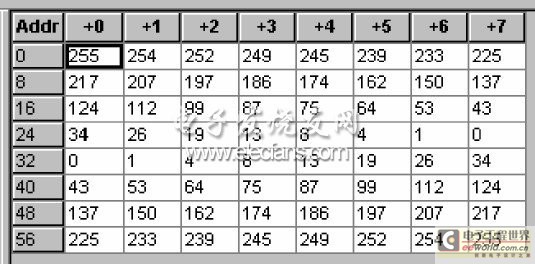

QuartusII 能接受的LPM_ROM 模塊中的初始化數(shù)據(jù)文件的格式有兩種:,。mif 格式文件和。hex 格式文件,。實際應(yīng)用中只要使用其中一種格式的文件即可,。下面采用。mif 格式文件,,調(diào)出產(chǎn)生ROM 數(shù)據(jù)文件大小的選擇窗,。根據(jù)64 點8 位正弦數(shù)據(jù)的情況,可選ROM 的數(shù)據(jù)數(shù)Number 為64,,數(shù)據(jù)寬Word size 取8 位,。單擊OK 按鈕,將出現(xiàn)圖2 所示的空的,。mif數(shù)據(jù)表格,,表格中的數(shù)據(jù)格式可通過鼠標(biāo)右鍵單擊窗口邊緣的地址數(shù)據(jù)彈出的窗口選擇。

圖2 .mif 數(shù)據(jù)表格

將波形數(shù)據(jù)填入mif 文件表中也可以使用QuartusII 以外的編輯器設(shè)計MIF 文件,,其格式如下:

#include

#include "math.h"

main()

{int i,;float s,;

for (i=0;i<1024,; i++)

{ s = sin(atan(1)*8*i/1024),;

printf("%d : %d;\n",,i,,(int)((s+1)*1023/2)); }}

把上述程序編譯成程序后,, 可在DOS 命令行下執(zhí)行命令:

romgen > sin_ rom. mif,;

1.2 定制LPM 元件

打開Mega Wizard Plug_In Manager 初始對話框, 選擇Create a new custom… 項,。單擊Next 按鈕后,,選擇Storage 項下的LPM_ROM, 再選擇ACEX1K 器件和VHDL 語言方式,;最后輸入ROM 文件存放的路徑和文件名:F:\sing_gnt\data_rom (定制的ROM 元件文件名),,單擊Next 按鈕,選擇ROM 控制線,、地址線和數(shù)據(jù)線,。這里選擇地址線位寬和ROM 中數(shù)據(jù)數(shù)分別為6 和64; 選擇地址鎖存控制信號inclock,。

對于地址信號發(fā)生器的設(shè)計,。方法一:用VHDL 語言設(shè)計6 位計數(shù)器,產(chǎn)生其元件符號,;方法二:仍采用LPM 定制的方法,。

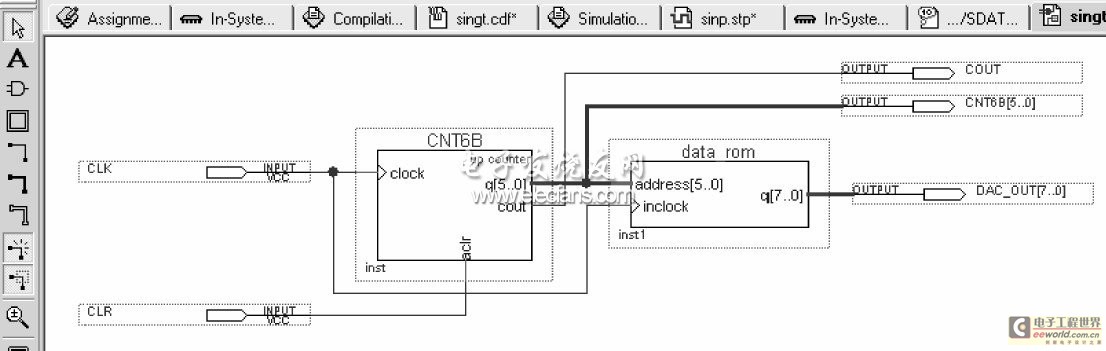

1.3 完成頂層設(shè)計

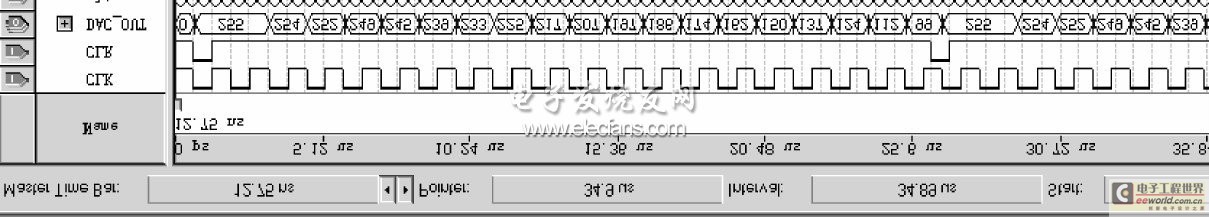

按圖3 畫出頂層原理圖,然后進(jìn)行編譯,,波形仿真如圖4所示,。

圖3 簡易正弦信號發(fā)生器頂層電路設(shè)計

圖4 當(dāng)前工程仿真波形輸出

對當(dāng)前設(shè)計通過執(zhí)行Quartus II 的命令Create ∠ Update/ Create Symbol Files for Current File,可以為設(shè)計電路建立一個元件符號,,以便被頂層設(shè)計多功能信號發(fā)生器所調(diào)用,。

2 其他信號部分原程序

其他各信號發(fā)生器可參照正弦信號發(fā)生器的設(shè)計方法設(shè)計或直接采用VHDL 硬件描述語言進(jìn)行設(shè)計。

LIBRARY IEEE,;--遞增鋸齒波的設(shè)計

USE IEEE.STD LOGIC 1164.ALL,;

USE IEEE.STD LOGIC UNSIGNED.ALL;

ENTITY signal2 IS --遞增鋸齒波signal1

PORT(clk,,reset:IN std_logic,;--復(fù)位信號reset, 時鐘信號clk

q:OUT std_logic_vector (7 DOWNTO 0)),;--輸出信號q

END signal2,;

ARCHITECTURE b OF signal2 IS

BEGIN

PROCESS(clk,,reset)

VARIABLE tmp:std_logic_vector(7 DOWNTO 0);

BEGIN

IF reset='0' THEN

tmp:="00000000",;

ELSIT rising_ege(clk)THEN

IF tmp="11111111"THEN

tmp:="00000000",;

ELSE

tmp:=tmp+1; --遞增信號的變化

END IF,;

END IF,;

q<=tmp:

END PROCESS;

END b,;

LIBRARY IEEE,;--方波的設(shè)計

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL,;

entity signal5 is --方波signal5

PORT(clk,,reset:in std_logic; --復(fù)位信號reset,,時鐘信號clk

q:out std_logic_vector (7 DOWNTO 0)),; --輸出信號q,8 位數(shù)字信號

END signal5,;

ARCHITEECTURE a OF signal5 IS

SIGNAL; a:std_logic,;

BEGIN

PROCESS(clk,,reset)

YARIABLE tmp:std_logic_vector(7 downto 0);

BEQIN

IF reset='0' then

a<='0',;

elsif rising_edge(clk)THEN

IF tmp="11111111" THEN

tmp:="00000000",;

ELSE

tmp:=tmp+1;

END IF,;

if tmp<="10000000" then

a<='1',;

else

a<='0';

END IF,;

END IF,;

END PROCESS;

PROCESS(clk,,a)

BEGIN

IF rising_edge(clk)THEN

IF a='1' THEN

q<="11111111",;

ELSE

q<="00000000";

END IF,;

END IF,;

END PROCESS;

END a,;

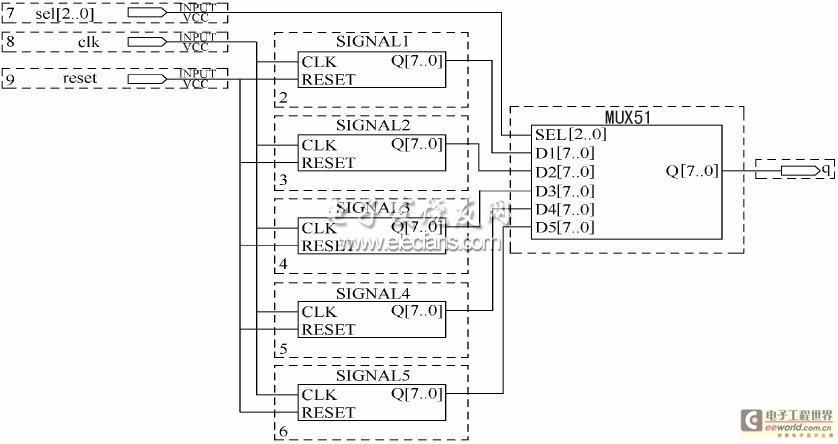

3 頂層電路的設(shè)計

將上述6 個模塊生成符號,,供頂層電路調(diào)用,。這些模塊分別是:遞減鋸齒波信號產(chǎn)生模塊signall、遞增鋸齒波信號產(chǎn)生模塊signal2,、三角波信號產(chǎn)生模塊signal3,、階梯波信號產(chǎn)生模塊signal4、方波信號產(chǎn)生模塊signal5 和數(shù)據(jù)選擇器mux51,。頂層電路的連接如圖5 所示,。

圖5 信號發(fā)生器頂層電路

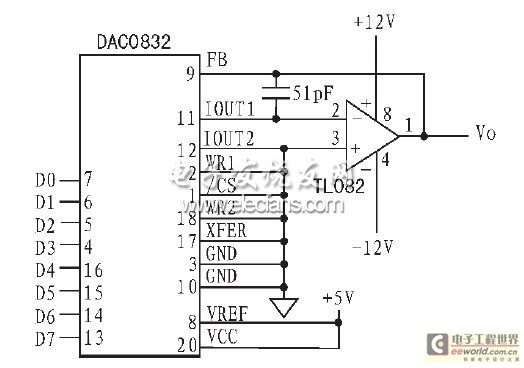

4 D/A 轉(zhuǎn)換器的連接

選擇一個D/A 轉(zhuǎn)換器,將數(shù)據(jù)選擇器的輸出與D/A 轉(zhuǎn)換器的輸入端連接,。D/A 轉(zhuǎn)換器的可選范圍很寬,,這里以常用的DAC0832 為例。DAC0832 的連接電路如圖6 所示,。

圖6 DAC0832 的連接電路

5 實現(xiàn)與測試

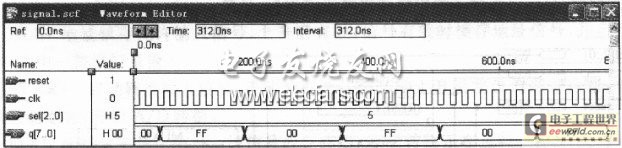

信號發(fā)生器頂層電路的仿真波形如圖7 所示,,這里只就輸入選擇信號等于5 時的情況進(jìn)行仿真,此時輸出波形是方波,,輸出的數(shù)字信號為周期性的全0 或全1,。

圖7 信號發(fā)生器頂層電路的仿真波形

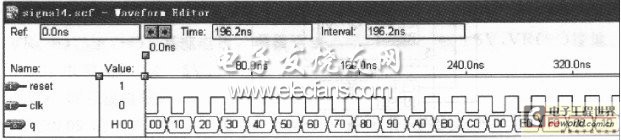

信號發(fā)生器的底層電路模塊也可以分別進(jìn)行仿真,例如對階梯波信號產(chǎn)生模塊signal4 進(jìn)行仿真,,仿真波形如圖8 所示,,輸出的數(shù)字信號為階梯狀變化。

圖8 階梯波信號產(chǎn)生模塊signal4 的仿真波形

6 結(jié)束語

硬件電路設(shè)計主要是設(shè)計相關(guān)模塊的設(shè)計思想的可視化,,是相關(guān)模塊的電路圖的匯總和其相關(guān)仿真波形的集錦,,該部分條理清晰,思路明確,,從中我們可以清晰地看到該設(shè)計方案的具體模塊和整個設(shè)計的原理結(jié)構(gòu)實圖,;程序設(shè)計這一部分主要闡述該設(shè)計的設(shè)計方法與設(shè)計思想,進(jìn)一步從軟件設(shè)計上揭示設(shè)計構(gòu)思,,主要包含了整個設(shè)計所用到的模塊的硬件描述語言的設(shè)計,, 本文設(shè)計思路清晰,通過QuartusII 軟件進(jìn)行波形仿真成功,,特別是正弦信號發(fā)生器的LPM 定制對于編程不是特別強(qiáng)的人員提供另一種途徑來實現(xiàn),,加深理解EDA 的層次設(shè)計思想,很好的把握住了教學(xué)的改革方向,,更好的鍛煉了學(xué)生理論聯(lián)系實踐的能力,。