電能的高效率應用能夠使家用電器成本降低并保護環(huán)境。絕大多數(shù)的家用電器,如電冰箱、洗衣機、烘干機、洗碗機以及空調(diào),都是由電機驅(qū)動的。這些設備通常包括了電源、電機、電機控制電路和機械系統(tǒng)。我們可以采用多種方法來改善系統(tǒng)效率。包括:

1. 維持電壓恒定;

2. 盡量減少相位不平衡;

3. 維持功率因數(shù)恒定;

4. 保持良好的電源質(zhì)量;

5. 采用可調(diào)式速度驅(qū)動或雙速電機;

6. 控制好溫度;

7. 匹配電機運行速度。

利用數(shù)字電路或FPGA控制模擬電機電路將使系統(tǒng)成本和功耗大大降低。采用FPGA除了可以節(jié)能之外,還能夠?qū)⑶度胧綌?shù)字信號處理(DSP)、微控制器、I/O接口等功能整合到一起,從而實現(xiàn)完整的家電設計。

脈沖寬度調(diào)制

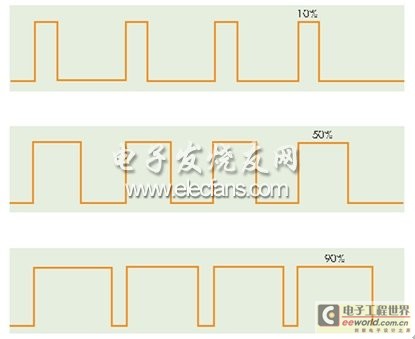

用數(shù)字方式控制模擬電機電路的一種典型方法是采用脈沖寬度調(diào)制(PWM)。此時方波的時間周期是恒定的,而接通時間(TON)即信號保持高電平的時間可以被改變或調(diào)制。因此,信號的占空比或平均直流電平是變化的。借助于數(shù)字系統(tǒng)的支持,PWM已經(jīng)成為控制模擬電路的一種極好方式。圖1就是數(shù)字脈沖的接通時間改變的例子。

應用實例包括電壓調(diào)整,即通過改變占空比將輸出電壓控制到所要求的電平。另一個例子是功率發(fā)送,這時的平均發(fā)送功率是調(diào)制占空比的函數(shù)。 PWM的實現(xiàn)取決于具體的使用方法,對于簡單的電壓調(diào)整,可以使用CPLD(例如Altera MAX II)實現(xiàn),而對于需要利用內(nèi)部DSP模塊的復雜控制算法,可以使用低成本的FPGA(例如Altera Cyclone III)實現(xiàn)。

圖2是PWM的基本方框圖,而圖3則是一個驅(qū)動模擬電機接口電路的調(diào)制輸出。UP和DOWN輸入信號被用來調(diào)整輸出信號的占空比,它們可以由微控制器產(chǎn)生。第一個模塊利用所有MAX II器件中都有的UFM振蕩器來產(chǎn)生兩個頻率不同的時鐘。來自該模塊的4位輸出信號DUTY_CYCLE的增加或降低取決于UP或DOWN信號的證實。第二個4位輸出信號COUNT以第一個模塊中產(chǎn)生的較高時鐘頻率連續(xù)增加。該信號與第二個模塊中相同頻率的DUTY_CYCLE信號進行比較。比較的結(jié)果是分配到最終輸出信號PWM的單個位。信號DUTY_CYCLE是一個4位的變量,因此輸出信號的占空比具有16個不同的取值。在本設計實現(xiàn)中,輸入UP的優(yōu)先級要高于DOWN。因此,如果兩個信號同時為高電平,輸出信號將被視作占空比的增加。

圖1:PWM波形示例。

圖2:PWM基本框圖

圖3:電機模擬驅(qū)動電路。

DSP電機控制

Cyclone III FPGAs中的嵌入式DSP功能塊(如圖4所示)為設計更復雜和效率更高的電機控制系統(tǒng)提供了關鍵要素。基于FPGA的DSP芯片使得大型家電制造商能夠降低研發(fā)時間和成本,并且在未來升級時不需要重新布板。FPGA所提供的可重配置解決方案可用來實現(xiàn)DSP應用以及滿足高DSP吞吐率的需求。由于 FPGA可以實現(xiàn)硬件重配置,因而能實現(xiàn)完整的硬件定制并實現(xiàn)復雜的電機控制DSP功能。因此,由FPGA實現(xiàn)的DSP系統(tǒng)可以具有定制的架構(gòu)、定制的總線結(jié)構(gòu)、定制的存儲器、定制的硬件加速器模塊和各種大量的乘法-累加(MAC)塊。

圖4:FPGA中的嵌入式DSP塊。

為了使交流電機的運行效率更高,內(nèi)部永久磁鐵的位置與施加的交流電壓頻率同步至關重要。可以使用傳感器來檢測磁轉(zhuǎn)子的位置,并以此調(diào)節(jié)電壓的頻率。該方法類似于伺服控制鎖相環(huán)(PLL)系統(tǒng),只不過這里采用DSP來實現(xiàn)這一任務。

圖5:典型的應用方框圖。

新一代的家電將需要更復雜的電路來監(jiān)控電機和整個系統(tǒng)的運行狀況。使用FPGA中DSP功能的先進控制算法設計將能夠?qū)崿F(xiàn)比特殊應用標準產(chǎn)品(ASSP)或特殊應用集成電路(ASIC)更靈活的系統(tǒng)。由于FPGA可以編程,因此可以根據(jù)市場需求的變化修改或加入新功能。如果加入一個以太網(wǎng) IP核,F(xiàn)PGA還能夠通過IP網(wǎng)絡與外界進行通訊,從而允許系統(tǒng)安排好系統(tǒng)發(fā)生故障之前的維護和服務工作,并實現(xiàn)用戶家庭網(wǎng)絡的無線通信。

微控制器

新一代家電設備將通過微控制器實現(xiàn)用戶接口和其他的功能控制。具有嵌入式微控制器的FPGA提供了一個集成的解決方案,無需另外再配外部專用處理器。嵌入式處理器設計師面臨的主要挑戰(zhàn)是如何選擇處理器,使之最適合具體的應用但又不過分地浪費或犧牲功能。像Altera的Nios? II軟件處理器就允許設計師創(chuàng)建理想的硬件(CPU,外設以及定制硬件加速器)、軟件(存儲器接口)和成本的綜合環(huán)境,以滿足每一個新的家電設計階段的獨特需求。

此外,Altera公司的 Nios II C-to-Hardware Acceleration (C2H) Compiler可以幫助那些對FPGA比較陌生的工程師利用ANSI C代替原理圖或RTL輸入進行嵌入式處理器系統(tǒng)設計。

LCD面板接口

FPGA中內(nèi)置的LVDS I/O接口允許直接耦合并驅(qū)動簡單文本或視頻質(zhì)量的顯示器面板,因而在系統(tǒng)中可以很容易設計出用于顯示器的視頻處理器和定時控制器。一片Cyclone III FPGA可以被設計和配置成為一個驅(qū)動典型液晶顯示器(LCD)接口的圖像增強引擎。而預先經(jīng)過優(yōu)化的IP MegaCore?功能,例如去交織、量化、濾波以及色彩空間轉(zhuǎn)換器,都可以處理來自任何源設備的視頻輸入,并輸出到象具有網(wǎng)絡功能的電冰箱上的視頻顯示器這樣的LCD面板上。

本文小結(jié)

低成本的FPGA或CPLD可以幫助家電設計師利用靈活的、集成有DSP算法的單片集成解決方案實現(xiàn)節(jié)能的電機控制。此外,這些具有內(nèi)置軟處理器的可編程器件還有助于簡化設備的用戶接口設計。利用這些器件還可以使新一代的家電設備能夠與用戶的家庭網(wǎng)絡進行無線通信。