介紹了Intersil公司推出的可編程數(shù)字" title="數(shù)字">數(shù)字上變頻" title="變頻">變頻器HSP50415" title="HSP50415">HSP50415的結(jié)構(gòu)、功能和特點(diǎn),給出了HSP50415在數(shù)字上變頻應(yīng)用中與TMS320VC5509的接口電路。

1 引言

軟件無線電的基本思想是在一個(gè)通用的硬件平臺上,通過軟件加載的方式用軟件實(shí)現(xiàn)所有無線電臺的功能。軟件無線電的理想結(jié)構(gòu)是將A/D、D/A盡可能地靠近天線。考慮到目前A/D、D/A的帶寬及DSP的處理能力,一般采用中頻采樣的軟件無線電結(jié)構(gòu)。

2 HSP50415的功能和特點(diǎn)

2.1 HSP50415的內(nèi)部結(jié)構(gòu)和功能

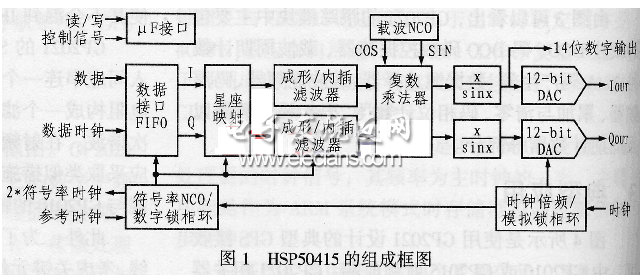

HSP50415由256深度的FIFO數(shù)據(jù)緩沖器、星座映射器、成形和內(nèi)插濾波器、復(fù)數(shù)乘法器、符號率NCO、載波NCO及雙路DAC組成。其內(nèi)部組成如圖1所示。各組成部分的功能如下:

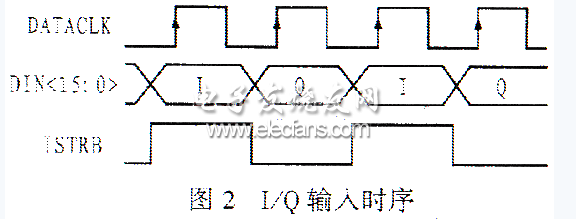

前端數(shù)據(jù)輸入模塊:HSP50415的信號輸入管腳是DIN(0~15)、ISTRB、TXEN和DATACLK。數(shù)據(jù)輸入有兩種方式:一種是固定符號速率傳輸方式,一種是猝發(fā)傳輸方式。在固定符號速率傳輸方式下,數(shù)據(jù)將以2倍采樣率進(jìn)入數(shù)據(jù)緩沖區(qū),緩沖區(qū)為256×32bit的FIFO。一旦一對I和Q數(shù)據(jù)進(jìn)入FIFO,數(shù)據(jù)會(huì)以采樣率讀出。因?yàn)镕IFO完成了一個(gè)串并變換,將一路信號變換成I和Q兩路信號,因此輸入端數(shù)據(jù)率是輸出端的2倍。在猝發(fā)方式下,當(dāng)數(shù)據(jù)滿或半滿時(shí),F(xiàn)IFO的標(biāo)志位可觸發(fā)DSP的中斷,通知DSP停止發(fā)數(shù)據(jù),這時(shí)可讀數(shù)據(jù)。I/O輸入時(shí)序如圖2所示。

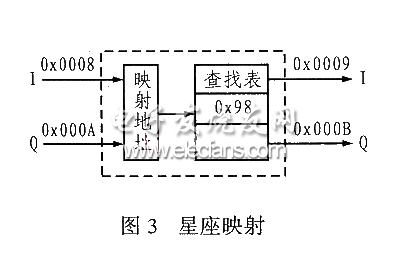

星座映射圖:星座映射圖中有一個(gè)用戶可編程查找表(256×8bit RAM),這個(gè)查找表僅支持I/Q最大位寬為4bit(256QAM)的數(shù)據(jù),可完成各種正交的PM和AM基帶碼映射。I和Q數(shù)據(jù)合并成8bit的數(shù)據(jù)作為地址去查表,得到映射數(shù)據(jù)并以Iout<3:0>和Qout<3:0>的形式輸出,如圖3所示。

成形濾波器:成形濾波器的基本內(nèi)插率為×4、×8或×16。此外,還有一個(gè)可選的2bit模式以供用戶將抽樣率減少1/2。成形濾波器的運(yùn)算由移位累加來完成,其最大輸入采樣率為MIN((CLK×2×2^twoBitMode)/(#bit×interpolationRate),CLK/4)。若使用2bit模式,則式中twoBitMode為1,否則為0,#bit為輸入數(shù)據(jù)的位數(shù),interpolationRate為內(nèi)插率。

半帶濾波器:半帶濾波器的內(nèi)插率為2,由于其系數(shù)在偶數(shù)點(diǎn)上為零,因此可將計(jì)算量減少一倍。

內(nèi)插濾波器:內(nèi)插濾波器將半帶濾波器的輸出采樣率插值到最終的采樣率Fsout。

數(shù)控振蕩器(NCO):為內(nèi)插濾波器提供時(shí)鐘,并允許輸入和輸出采樣率有非整數(shù)倍關(guān)系。

乘法器:把基帶信號調(diào)制到可編程中頻上。

輸出模塊:HSP50415內(nèi)部集成了雙路12位DAC,并由x/sinx濾波器提供滾降補(bǔ)償,可以實(shí)現(xiàn)模擬輸出。另外還提供了14位數(shù)字輸出。

2.2 HSP50415的特點(diǎn)

HSP50415是一個(gè)功能強(qiáng)大的可編程調(diào)制器,編程十分靈活,信號的極性可以通過編程來改變,內(nèi)部集成了高速D/A轉(zhuǎn)換器,性價(jià)比較高。HSP50415具有功耗低、 精度高、可靠性強(qiáng)等優(yōu)點(diǎn),其主要性能參數(shù)如下:

●最高輸出采樣率達(dá)100MHz?最高輸入數(shù)據(jù)率達(dá)25MHz。

●編程載波NCO和符號NCO均為32位,精度高。

●x/sinx滾降補(bǔ)償。

●每路有四片64×72位的FIR濾波器,其系數(shù)RAM可由Intersil公司提供的軟件來產(chǎn)生。

●成形濾波器的內(nèi)插率可編程設(shè)置,達(dá)24個(gè)符號間隔,半帶濾波器和內(nèi)插濾波器的系數(shù)是固定的。

●數(shù)字信號處理能力大于70dB(SFDR)。

●14位數(shù)字輸出或雙路12位D/A模擬輸出,D/A處理能力大于50dB。微處理器端口有18個(gè)控制寄存器,可方便地控制256×32位FIFO及其深度、成形濾波器的階數(shù)、增益調(diào)整、符號速率、載波頻率及是否旁路某些模塊等。

2.3 HSP50415的主要管腳功能:

CLK: 系統(tǒng)時(shí)鐘

SYSCLK/2: 系統(tǒng)內(nèi)部時(shí)鐘

DIN<15:0>: 數(shù)據(jù)總線

CDATA<7:0>: 微處理器數(shù)據(jù)總線

RD: 微處理器讀

WR: 微處理器寫

ADDR<2:0>: 微處理器地址總線

Iout<13:0>,Qout<13:0>: 數(shù)字輸出

IOUTA,IOUTB,QOUTA,QOUTB: 模擬輸出

2*SYMCLK: 采樣時(shí)鐘的2倍

REFCLK: 參考時(shí)鐘

DATACLK: 異步數(shù)據(jù)時(shí)鐘

TXEN: 猝發(fā)模式選通信號

ISTRB: 路數(shù)據(jù)選通信號

INTREQ: 中斷請求信號

FEMPT,FOVER,FFULL: FIFO電平監(jiān)控信號

LOCKDET: 數(shù)字鎖相環(huán)的狀態(tài)標(biāo)志

ICOMP,QCOMP: 為減小串音提供的補(bǔ)償信號

REFLO: 內(nèi)部參考選擇

REFIO: 外部參考電壓輸入

FSADJ: 滿量程電流調(diào)整

2.4 HSP50415的初始化及參數(shù)設(shè)置

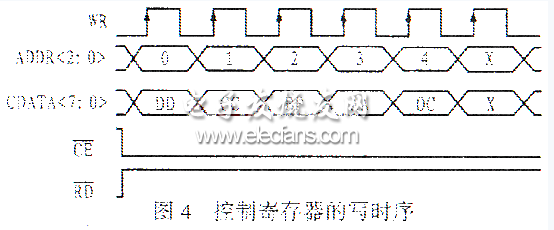

HSP50415的初始化包括兩部分,一是對控制寄存器的初始化,二是對成形濾波器系數(shù)RAM及星座映射器RAM的初始化。HSP50415總共有18個(gè)寄存器,通過對這些控制寄存器的訪問,可以方便地控制256×32位FIFO及其深度、成形濾波器的階數(shù)、增益調(diào)整、符號速率、載波頻率以及是否旁路某些模塊等,從而便于進(jìn)行硬件調(diào)試。系數(shù)和控制字的值可以使用Intersil公司網(wǎng)站提供的可執(zhí)行文件sim415.exe和modulator.exe方便地產(chǎn)生。圖4表示將值為AABBCCDD的控制字送入地址為0C的控制寄存器的時(shí)序。

HSP50415的參數(shù)可由下面的公式確定:

符號率NCO=(symbolrate/Fsout)×232

載波NCO=(carrierFrequency/Fsout)×232

3 HSP50415的調(diào)制原理及實(shí)現(xiàn)

3 HSP50415的調(diào)制原理及實(shí)現(xiàn)

HSP50415的復(fù)數(shù)乘法器可完成如下運(yùn)算:

S(n)=I(n)cos(ω0ts)-Q(n) sin(ω0ts)?

其中,S(n)為輸出信號,ω0為載波頻率,ts為取樣間隔。根據(jù)I(n)和Q(n)編碼方式的不同,可以完成BPSK、QPSK、m-QAM等調(diào)制方式。如令Q(n)=0,則:

S(n)=I(n)cos(ω0ts)

此時(shí)即可得到DSB調(diào)制信號。

4 用HSP50415實(shí)現(xiàn)數(shù)字上變頻

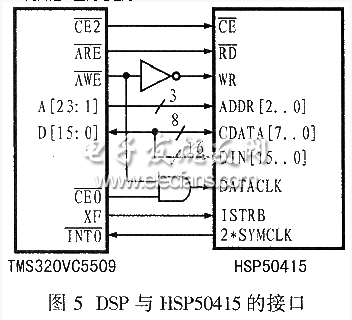

HSP50415編程靈活,可應(yīng)用于無線電臺的發(fā)射系統(tǒng)中。圖5為HSP50415與TMS320VC5509的接口電路,可用來實(shí)現(xiàn)數(shù)字上變頻技術(shù)。

圖中采用了兩個(gè)片選信號,用于區(qū)分微處理器端口和數(shù)據(jù)端口。初始化時(shí)CE2選通,DSP通過微處理器接口訪問HSP50415。初始化完成后CE0選通,DSP每收到一個(gè)中斷,便通過DATA/FIFO接口向HSP50415發(fā)一個(gè)數(shù)據(jù)。XF連接ISTRB以表明這個(gè)數(shù)據(jù)是I數(shù)據(jù)還是Q數(shù)據(jù)。CE0與AWE相或產(chǎn)生DATACLK信號。中斷信號由2*SYMCLK產(chǎn)生。

5 典型程序代碼

5.1 一個(gè)32位寄存器初始化代碼

amov #BUFF0,xar0 ;BUFF0定義為片選2空間的地址0x400000

mov #0xDD, *ar0

amov #BUFF1, xar0 ;BUFF1定義為片選2空間的地址0x400001

mov #0xCC, *ar0

amov #BUFF2, xar0 ;BUFF2定義為片選2空間的地址0x400002

mov #0xBB, *ar0

amov #BUFF3, xar0 ;BUFF3定義為片選2空間的地址0x400003

mov #0xAA, *ar0

amov #BUFF4,xar0 ;BUFF4定義為片選2空間的地址0x400004

mov #0x0C, *ar0

5.2 簡單的發(fā)送程序(以正弦波為例)

mov #63, ac0 ;設(shè)發(fā)射通常為64,循環(huán)發(fā)送

amov real_data, xar1 ;xar1中存放實(shí)數(shù)

amov imag_data, xar2 ;xar2中存放虛數(shù)

send:

amov #FIFO, xar0 ;定義FIFO為片選0空間地址為0x02000

bset xf

mov *ar1+, *ar0

bclr xf

mov *ar2+, *ar0

sub #1, ac0

bcc qq, ac0==0

reti

qq: mov #63, ac0

amov real_data, xar1

amov imag_data, xar2

reti