1 引言

FPGA 技術(shù)在國(guó)內(nèi)外經(jīng)過(guò)歷時(shí)十余載的以硬件、系統(tǒng)及應(yīng)用設(shè)計(jì)為主要內(nèi)容的迅速發(fā)展 之后,其現(xiàn)代信息處理與控制技術(shù)的發(fā)展已開(kāi)始崛起。顯然,一系列以乘法和加法為主的現(xiàn) 代信息處理算法能夠發(fā)揮FPGA 全并行算法的優(yōu)勢(shì),然而,算法中反復(fù)遇到的數(shù)字信息在節(jié) 點(diǎn)與模塊之間的序貫傳遞和交接,則給多路并行處理過(guò)程帶來(lái)了時(shí)差和異步的問(wèn)題。例如, 系統(tǒng)辨識(shí)[1]的最小二乘參數(shù)估計(jì)算法中,信息壓縮矩陣與模型參數(shù)估計(jì)向量在并行地進(jìn)行著 遞推計(jì)算,而無(wú)數(shù)次循環(huán)的中間結(jié)果則需要進(jìn)行首尾交接;人工神經(jīng)網(wǎng)絡(luò)[2]的訓(xùn)練與執(zhí)行中 同一層的所有節(jié)點(diǎn)的各路輸入在進(jìn)行著并行的加權(quán)求和與活化函數(shù)的代入計(jì)算,但層與層之 間則需要進(jìn)行節(jié)點(diǎn)間的數(shù)據(jù)交錯(cuò)傳遞;同樣,Kalman 濾波[3]算法中的觀測(cè)向量、狀態(tài)向量、 控制向量與噪聲向量都在相鄰的兩個(gè)時(shí)刻之間進(jìn)行著數(shù)據(jù)傳遞。由于在同一層次上被并行地 執(zhí)行的各路的行進(jìn)速度并不相同,交接的過(guò)程就需要互相等待,整個(gè)過(guò)程就需要統(tǒng)一控制, 否則將會(huì)出現(xiàn)數(shù)據(jù)丟失或傳輸阻塞。

本文將從硬件結(jié)構(gòu)與功能的Verilog 語(yǔ)言數(shù)據(jù)流描述的角度,逐層討論問(wèn)題的解決辦法 。

2 FPGA 的數(shù)據(jù)傳輸接口

2.1 模塊內(nèi)的數(shù)據(jù)傳輸

在一個(gè)模塊內(nèi),變量之間的數(shù)據(jù)傳輸接口的性質(zhì)可分別用 reg(寄存功能,有延時(shí)性) 和wire(連線功能,無(wú)延時(shí)性)來(lái)定義。Reg 型常表示“always”( 觸發(fā)器)模塊的指定信 號(hào),前者由后者通過(guò)使用行為描述語(yǔ)句來(lái)表達(dá)邏輯關(guān)系。

而wire 型常表示“assign”關(guān)鍵字的制定組合邏輯信號(hào)。當(dāng)輸入輸出信號(hào)類型默認(rèn)時(shí)自 動(dòng)定義為wire 型。wire 型信號(hào)可以用作任何方程式的輸入,并且wire 型變量通常是用來(lái)表 示單個(gè)門(mén)驅(qū)動(dòng)或連續(xù)賦值語(yǔ)句驅(qū)動(dòng)的網(wǎng)絡(luò)型數(shù)據(jù)。

2.2 模塊間的數(shù)據(jù)傳輸

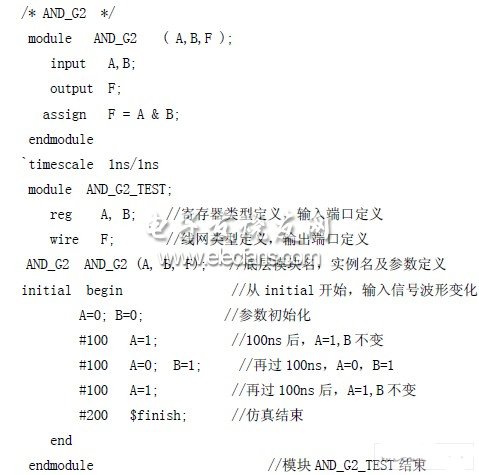

模塊間的數(shù)據(jù)傳輸接口例如延時(shí)輸出寄存器,它是一個(gè)使用了可控延時(shí)寄存器功能的AND 邏輯模塊(記作AND_G2)的數(shù)據(jù)流描述如下:

該程序中AND_G2_teST 為頂層模塊,AND_G2 作為一個(gè)單獨(dú)的模塊被頂層模塊所調(diào) 用。通過(guò)綜合控制,A、B 的輸入信號(hào)達(dá)到同步。

3 FPGA-信息處理實(shí)例—簡(jiǎn)單人工神經(jīng)網(wǎng)絡(luò)設(shè)計(jì)

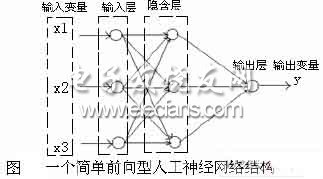

一個(gè)包括三個(gè)輸入、單個(gè)輸出、一個(gè)三節(jié)點(diǎn)隱含層的前向型人工神經(jīng)網(wǎng)絡(luò)結(jié)構(gòu)如圖1 所示。下面從多個(gè)角度討論數(shù)據(jù)的處理與傳輸。

3.1 信息處理數(shù)學(xué)過(guò)程為:

3.2 算法的Verilog 數(shù)據(jù)流描述:

3.2 算法的Verilog 數(shù)據(jù)流描述:

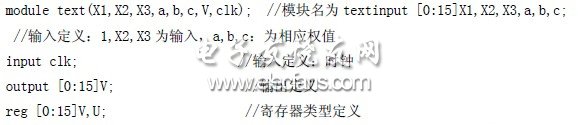

1)一個(gè)節(jié)點(diǎn)的模塊:

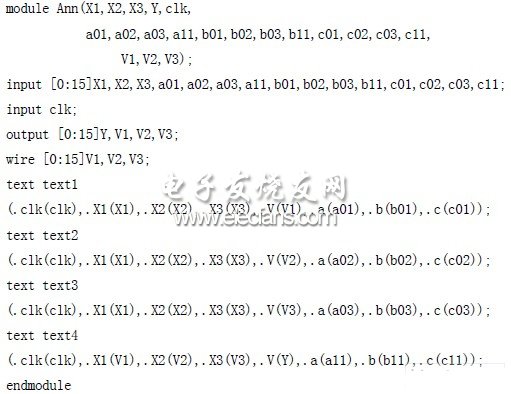

2)頂層整體調(diào)用模塊

3)信息傳輸界面問(wèn)題

上述人工神經(jīng)網(wǎng)絡(luò)運(yùn)算中不同層次間的數(shù)據(jù)交錯(cuò)序列式傳輸采用了如下方式:從輸出到 輸入、從輸入到運(yùn)算邏輯通過(guò)wire 定義的網(wǎng)線執(zhí)行無(wú)延時(shí)傳輸;各節(jié)點(diǎn)輸出通過(guò)reg 定義 為寄存器,使信號(hào)能實(shí)現(xiàn)各自異步計(jì)算而同步輸出的效果,而輸出的條件用always 進(jìn)行檢 測(cè)。逐層的交錯(cuò)傳輸采用頂層模塊套用子模塊的方式進(jìn)行,同一層次的各節(jié)點(diǎn)的同類型運(yùn)算 均并行操作,既節(jié)省了時(shí)間,又節(jié)省了模塊。

4 結(jié)束語(yǔ)

通過(guò)網(wǎng)線、寄存器、鎖存器、多層次模塊套用等技術(shù)的應(yīng)用與數(shù)學(xué)算法的變換處理,大多數(shù)現(xiàn)代信息處理、統(tǒng)計(jì)學(xué)計(jì)算及控制過(guò)程的復(fù)雜算法都可以實(shí)現(xiàn)完全并行處理與序貫交錯(cuò) 傳遞的最佳時(shí)間性綜合運(yùn)行而體現(xiàn)其快速、遞推、多維和實(shí)時(shí)性。 在Xilinx 公司提供的 ISE10.1 設(shè)計(jì)工具軟件平臺(tái)上對(duì)LC3S400PQ205 型FPGA 產(chǎn)品進(jìn)行上述簡(jiǎn)單前向型人工神經(jīng)網(wǎng) 絡(luò)的硬件結(jié)構(gòu)數(shù)據(jù)流描述設(shè)計(jì),得到的整體模塊只占用了將近15 萬(wàn)個(gè)門(mén)(而整個(gè)芯片具有 40 萬(wàn)個(gè)門(mén)),完成一組采樣值的全過(guò)程計(jì)算時(shí)間為16ms。加上FPGA 的在線實(shí)時(shí)可重構(gòu)性, 使得該項(xiàng)技術(shù)可以在宇宙或環(huán)球航行、高空與深海測(cè)量、危險(xiǎn)區(qū)或動(dòng)物體非介入性試驗(yàn)等多 種領(lǐng)域的高科技信息處理與控制中發(fā)揮特殊作用。