1、簡(jiǎn)介

每個(gè)HBLED制造商的目標(biāo)都是花更少的錢獲得更多的光輸出。面對(duì)強(qiáng)大的競(jìng)爭(zhēng)和眾多技術(shù)障礙,至關(guān)重要的是所有的生產(chǎn)步驟的推進(jìn)都要產(chǎn)生最佳的效果。優(yōu)化的刻蝕" title="等離子刻蝕">等離子刻蝕提供了幾種方法以改善器件的輸出并降低制造成本,從而實(shí)現(xiàn)雙重贏利。

2、圖形化藍(lán)寶石襯底

現(xiàn)在藍(lán)寶石仍是生長(zhǎng)HBLED結(jié)構(gòu)的襯底選擇。不過(guò),采用藍(lán)寶石生長(zhǎng)也存在兩個(gè)問(wèn)題:藍(lán)寶石沒(méi)有完美的晶格匹配,光提取會(huì)因?yàn)橛袃蓚€(gè)平行的反射面而減少。未來(lái)解決這兩個(gè)問(wèn)題,從2005年起一些公司就在生長(zhǎng)之前就在藍(lán)寶石上刻蝕了圖形。這可以使一個(gè)成品器件的光提取性能改善98%以上。

藍(lán)寶石是一種非常穩(wěn)定的物質(zhì),熔點(diǎn)在2054度,因此難以進(jìn)行等離子刻蝕。不過(guò),在降低到通常的150度之前,用來(lái)實(shí)現(xiàn)非常具體的圖案形成的光阻仍有一個(gè)溫度上限。PR是這個(gè)過(guò)程選擇的掩膜,最終的“圓頂”狀依賴于所有掩膜去除的完成,其形狀與藍(lán)寶石和掩膜的相對(duì)刻蝕速率密切相關(guān)。由于簡(jiǎn)化了生產(chǎn)流程,降低每流明的整體成本,PR也成為了首選。

為了對(duì)材料進(jìn)行刻蝕,Cl2、BCl3、Ar的組合常用于以較高等離子源實(shí)現(xiàn)的較高刻蝕速率。不過(guò),這增加了試樣的熱負(fù)荷,因此,使用PR作為掩膜可以保持較高的刻蝕速率,為此有必要對(duì)晶圓試樣進(jìn)行有效的冷卻。

硅產(chǎn)業(yè)習(xí)慣于將單晶圓緊固在溫度控制工作臺(tái)上,并在工作臺(tái)和晶圓之間引入了傳熱介質(zhì),通常是氦。“氦背面冷卻”已經(jīng)成為單晶圓溫度控制的標(biāo)準(zhǔn)方法。HBLED制造目前市區(qū)批次較小的襯底,傳送到輸送板上的刻蝕工具。對(duì)于圖形化藍(lán)寶石襯底刻蝕,HBLED器件仍然主要制造2英寸或者4英寸晶圓,因此可以顯著降低成本,它對(duì)以一次運(yùn)行處理盡可能多的晶圓是可行的方法。大量光阻延膜晶圓的刻蝕要求控制好每個(gè)晶圓的溫度,這需要了解怎樣將來(lái)自等離子的熱量從試樣到冷卻電極轉(zhuǎn)移出來(lái)。氦氣背面冷卻是關(guān)鍵,同時(shí)要了解怎樣使每片晶圓德奧有效冷卻,以確保成功。這種技術(shù)的批量規(guī)模從20*2英寸到高達(dá)43*2英寸,刻蝕速率在50nm/分和100nm/分之間,速率取決于PR掩膜和PSS形狀要求。

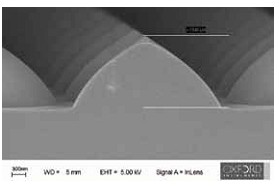

圖1 典型的圓頂PSS特性

3、GaN刻蝕

GaN的化學(xué)穩(wěn)定性和高鍵合強(qiáng)度、其熔點(diǎn)2500度和鍵能也是它具有很高的耐酸或堿刻蝕劑濕刻蝕能力。到目前為止,由于缺乏合適的濕刻蝕工藝,使人們對(duì)開(kāi)發(fā)合適HBLED生產(chǎn)的干刻蝕工藝產(chǎn)生了極大的興趣。這必須是單批次進(jìn)行大量晶圓刻蝕。20世紀(jì)90年代后期,等離子刻蝕批次規(guī)模從4*2英寸晶圓增加至今天的55*2英寸或3*8英寸,現(xiàn)在的問(wèn)題是在其吸引力消失之前它可以處理多大批次。隨著晶圓尺寸從2英寸到4英然后是6英寸的向上遷移,這個(gè)問(wèn)題也得到了解決。GaN刻蝕的主要應(yīng)用領(lǐng)域是淺接點(diǎn)刻蝕和高深寬比結(jié)構(gòu)刻蝕。

4、淺接點(diǎn)刻蝕

當(dāng)刻蝕進(jìn)入到接點(diǎn)層時(shí),至關(guān)重要的是對(duì)半導(dǎo)體造成的等離子損傷最小,否則可能會(huì)增加接點(diǎn)電阻。刻蝕工藝需要仔細(xì)優(yōu)化,以最大限度地提高吞吐量,同時(shí)保持器件的性能。光滑的表面通常表面高品質(zhì)的刻蝕,如圖2所示。

圖2 PR試樣中器件接點(diǎn)的淺GaN刻蝕

未經(jīng)優(yōu)化的刻蝕處理可能導(dǎo)致GaN刻蝕的位錯(cuò),進(jìn)而導(dǎo)致麻點(diǎn)表面和接點(diǎn)電阻的增加。同樣,PR是這一步掩膜的選擇,因?yàn)樗亲詈?jiǎn)單的處理方法。據(jù)報(bào)道由于典型批刻蝕速率高達(dá)140nm/分的溫度限制,PR的使用可降低所使用的功率。

5、深隔離刻蝕

當(dāng)需要高達(dá)7微米深度時(shí),刻蝕速率是這一工藝的關(guān)鍵。這一步的作用是刻蝕到有源器件之間的底層藍(lán)寶石襯底。由于藍(lán)寶石是不導(dǎo)電的,在物理分離之前就隔離了器件。如果使用PR掩膜,這一刻蝕步驟的主要挑戰(zhàn)是散熱,因?yàn)楦呖涛g速率是用高等離子密度實(shí)現(xiàn)的。這意味著單晶圓的緊固問(wèn)題,通常的方法是使用靜電吸盤。可以使用介質(zhì)硬掩膜,這將可能實(shí)現(xiàn)高刻蝕速率批處理,此時(shí)整個(gè)批次的一致性決定了產(chǎn)量。

6、光子晶體圖形化

利用稱為光子晶體的準(zhǔn)晶體陣列圖形化HBLED的發(fā)光表面可以提高光提取能力。其極端的表現(xiàn)如圖3所示,此時(shí)600nm蝕象已被刻蝕了4微米深,實(shí)現(xiàn)了大于6:1的高深寬比結(jié)構(gòu)。這里的挑戰(zhàn)是保持蝕象的垂直剖面,以確保光子晶體的光學(xué)性能。

圖3 高深寬比GaN深刻蝕

7、設(shè)備

為了達(dá)到高刻蝕速率和低損傷的要求,行業(yè)開(kāi)發(fā)了幾種高密度等離子源:電感耦合等離子(ICP)、變壓器耦合等離子(TCP)、高密度等離子(HDP)。所有技術(shù)都提供了一個(gè)固定試樣驅(qū)動(dòng)臺(tái),獨(dú)立等離子源可實(shí)現(xiàn)高等離子密度,而不會(huì)增加試樣的DC偏差。DC偏差已被證明可增加敏感表面的等離子損傷,所以這是一個(gè)至關(guān)重要的系統(tǒng)特性。