0 引言

目前,在PCM/FM遙測(cè)體系中模擬信號(hào)采集普遍采用8位量化,全部模擬信號(hào)均歸一化到O~5 V范圍內(nèi),隨著需要采集的模擬信號(hào)的類型多樣化,勢(shì)必增加信號(hào)調(diào)理電路的多樣性,不利于系統(tǒng)的簡(jiǎn)化和模塊化,。在量化位數(shù)一定的系統(tǒng)中,被衰減處理的信號(hào)中實(shí)際量化誤差等于N倍(N是信號(hào)被衰減的倍數(shù))的最小量化誤差,因此合理的信號(hào)調(diào)理電路和A/D取值是保證量化精度的關(guān)鍵,。本文提供的方式有效地解決了這個(gè)問題,既簡(jiǎn)化了前端信號(hào)調(diào)理電路的復(fù)雜度,又充分利用了A/D轉(zhuǎn)換器的輸入電壓動(dòng)態(tài)范圍和量化位數(shù)優(yōu)勢(shì),實(shí)現(xiàn)了對(duì)多路模擬信號(hào)的自適應(yīng)采集,對(duì)其他信號(hào)采集系統(tǒng)也具有一定的借鑒意義,。

l 系統(tǒng)設(shè)計(jì)

該系統(tǒng)主要由信號(hào)調(diào)理電路、采集電路和時(shí)序控制等幾部分組成,。被測(cè)模擬信號(hào)經(jīng)過信號(hào)調(diào)理電路后,經(jīng)多路選擇器的快速切換,按需求依次送入A/D轉(zhuǎn)換器進(jìn)行采樣,采樣后的數(shù)據(jù)送入FPGA中處理,系統(tǒng)框圖如圖1所示,。

系統(tǒng)設(shè)計(jì)的主要指標(biāo):模擬信號(hào)通道數(shù)為46路;系統(tǒng)采樣率大于300 Kb/s;量化位數(shù)為8位;頻率響應(yīng)范圍為DC~1 kHz;通道采樣率為100 Hz,200 Hz,400 Hz,500 Hz,800 Hz,1 kHz,2 kHz,4 kHz可選;A/D轉(zhuǎn)換器允許輸入信號(hào)的最大幅度為±10 V。

2 系統(tǒng)各部分功能及實(shí)現(xiàn)

2.1 信號(hào)調(diào)理電路

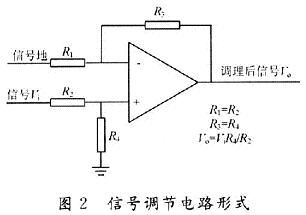

信號(hào)調(diào)理電路主要完成被測(cè)信號(hào)的阻抗匹配和電壓變換,設(shè)計(jì)時(shí)信號(hào)調(diào)理電路均采用差分輸入電路形式,。針對(duì)不同類型的信號(hào),通過調(diào)整電阻阻值即可實(shí)現(xiàn)信號(hào)的衰減,、放大或者阻抗匹配,有利于電路形式的模塊化和標(biāo)準(zhǔn)化。信號(hào)調(diào)節(jié)電路如圖2所示,。

整個(gè)信號(hào)調(diào)理電路采用±12 V供電,根據(jù)信號(hào)類型將全部模擬信號(hào)調(diào)理到合適的范圍內(nèi),以便充分利用A/D的輸入動(dòng)態(tài)范圍來實(shí)現(xiàn)自適應(yīng)采集,。

2.2 采集電路

采集電路主要包括多路選擇器和A/D轉(zhuǎn)換器等,多路選擇器采用ADG406,通過級(jí)聯(lián)可以形成46路模擬信號(hào)通道,采用±12 V供電,保證調(diào)理后的信號(hào)不失真通過,12根地址線用來控制模擬信號(hào)的切換;A/D轉(zhuǎn)換器采用AD7892-1,其具有±10 V的輸入電壓動(dòng)態(tài)范圍和12位的量化能力,信號(hào)輸入范圍設(shè)置為±10 V,控制線用來控制A/D轉(zhuǎn)換器的工作狀態(tài),并將轉(zhuǎn)換后的12位數(shù)據(jù)全部接入FPGA中進(jìn)行處理。

2.3 時(shí)序控制

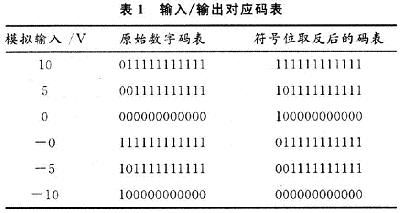

時(shí)序控制通過FPGA程序來實(shí)現(xiàn),主要完成多路選擇器的切換,A/D轉(zhuǎn)換器的控制和自適應(yīng)采集邏輯等功能,。對(duì)于多路選擇器的切換和A/D轉(zhuǎn)換器的控制邏輯,只要注意多路選擇器的開關(guān)穩(wěn)定時(shí)間和A/D轉(zhuǎn)換器的采樣時(shí)刻即可完成數(shù)據(jù)采集,。自適應(yīng)采集就是根據(jù)已知模擬信號(hào)的類型自動(dòng)選擇A/D的轉(zhuǎn)換器輸出碼位來實(shí)現(xiàn)的。為了便于對(duì)后文的理解,表1給出AD7892-l輸入/輸出對(duì)應(yīng)碼表和處理后的碼表,。

前面信號(hào)調(diào)理電路根據(jù)模擬信號(hào)的類型把信號(hào)分別調(diào)理到0~5 V,-5~-O V,-5~+5 V,O~+10 V,-10~-0 V,-10~+10 V等范圍內(nèi),結(jié)合表1的內(nèi)容即可實(shí)現(xiàn)對(duì)模擬信號(hào)的自適應(yīng)采集,保證信號(hào)的采集精度,。數(shù)據(jù)自動(dòng)轉(zhuǎn)換模塊的FPGA程序示例如下:

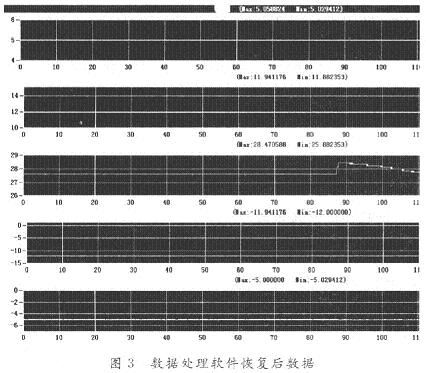

通過測(cè)試驗(yàn)證,該法是可行的。在不改變?nèi)魏斡布娐返那闆r下,通過FPGA程序可有效實(shí)現(xiàn)模擬信號(hào)的動(dòng)態(tài)量化,確保信號(hào)的量化精度,。通過數(shù)據(jù)處理軟件即可恢復(fù)原始信號(hào),如圖3所示,。

3 結(jié)語

設(shè)計(jì)的基于FPGA的多路模擬信號(hào)自適應(yīng)采集系統(tǒng),在有限的量化位數(shù)限制下,充分利用信號(hào)調(diào)理電路、A/D轉(zhuǎn)換器的輸入電壓動(dòng)態(tài)范圍和12位的位寬,在相同的量化位數(shù)下提高了大部分模擬信號(hào)的采樣精度,具有一定的參考價(jià)值。