在電力系統(tǒng)中,要實(shí)現(xiàn)對(duì)電能質(zhì)量各項(xiàng)參數(shù)的實(shí)時(shí)監(jiān)測(cè)和記錄,必須對(duì)電能進(jìn)行高速的采集和處理,尤其是針對(duì)電能質(zhì)量的各次諧波的分析和運(yùn)算,系統(tǒng)要完成大量運(yùn)算處理工作,同時(shí)系統(tǒng)還要實(shí)現(xiàn)和外部系統(tǒng)的通信、控制、人機(jī)接口等功能。而電能質(zhì)量監(jiān)測(cè)系統(tǒng)大多以微控制器或(與)DSP為核心的軟硬件平臺(tái)結(jié)構(gòu)以及相應(yīng)的設(shè)計(jì)開(kāi)發(fā)模式,存在著處理能力不足、可靠性差、更新?lián)Q代困難等弊端。本文將SoPC技術(shù)應(yīng)用到電力領(lǐng)域,在FPGA中嵌入了32位NiosⅡ軟核系統(tǒng)。可實(shí)現(xiàn)對(duì)電能信號(hào)的采集、處理、存儲(chǔ)與顯示等功能,實(shí)現(xiàn)了實(shí)時(shí)系統(tǒng)的要求。

1 系統(tǒng)概述

1.1 電能質(zhì)量檢測(cè)系統(tǒng)的基本原理

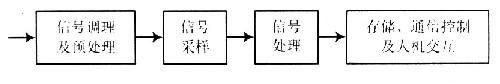

電能質(zhì)量監(jiān)測(cè)主要是對(duì)電能質(zhì)量各參數(shù)進(jìn)行實(shí)時(shí)監(jiān)測(cè)和記錄,其功能流程為:把電網(wǎng)中的電壓、電流經(jīng)過(guò)PT、CT變成-5~+5 V的電壓信號(hào)、1~2 mA的電流信號(hào),預(yù)處理后進(jìn)行采樣,對(duì)采樣值進(jìn)行數(shù)據(jù)處理,處理結(jié)果可以存儲(chǔ)在數(shù)據(jù)存儲(chǔ)單元,也可以通過(guò)通信模塊與計(jì)算機(jī)終端進(jìn)行通信,根據(jù)需要控制且查看處理結(jié)果。其系統(tǒng)基本原理方框圖如圖1所示。

圖1 系統(tǒng)基本原理方框圖

1.2 算法介紹

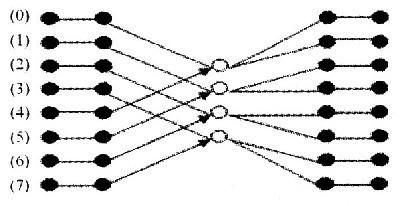

本文在處理諧波數(shù)據(jù)時(shí),采用基2的DIT方式的FFT算法。傳統(tǒng)的基2算法的蝶形圖中輸入采用的是按碼位顛倒的順序排放的,輸出是自然順序。同一位置不同級(jí)的蝶形的輸入數(shù)據(jù)的位置不固定,難以實(shí)現(xiàn)循環(huán)控制,用FPGA編程時(shí)難以并行實(shí)現(xiàn),通過(guò)對(duì)傳統(tǒng)的基2蝶形圖分析,調(diào)整其旋轉(zhuǎn)因子的位置,使得各級(jí)蝶形圖一致,如圖2所示,可以實(shí)現(xiàn)循環(huán)控制。

圖2 蝶形圖

這種結(jié)構(gòu)的輸入是順序的,而輸出是位反碼的,每級(jí)的旋轉(zhuǎn)因子都是放在FPGA的片內(nèi)ROM里的。調(diào)整后的旋轉(zhuǎn)因子的尋址有一定規(guī)律,對(duì)于N點(diǎn)的FFT(N=2k,K為級(jí)數(shù)),旋轉(zhuǎn)因子有,…,,共N/2個(gè),將他們按位碼倒序的形式排成一個(gè)含有N/2個(gè)元素的數(shù)組,記為:,,則第i級(jí)(i=O.1,2,…,K-1)的旋轉(zhuǎn)因子排列順序是W(O),W(1),W(2),…,W(2i)重復(fù)2k-i-l次得到的。其特點(diǎn)是每級(jí)的輸入、輸出數(shù)據(jù)的順序是不變的,因此每級(jí)幾何結(jié)構(gòu)是固定的。用這種結(jié)構(gòu)尋址方便,易于用FPGA編程,實(shí)現(xiàn)內(nèi)部并行的FFT硬件結(jié)構(gòu),從而明顯加快FFT的運(yùn)算速度。

2 電能質(zhì)量檢測(cè)系統(tǒng)硬件設(shè)計(jì)

2.1 A/D轉(zhuǎn)換器

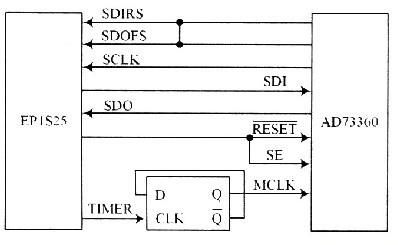

根據(jù)實(shí)測(cè)數(shù)據(jù),如果采用12位分辨率的A/D轉(zhuǎn)換芯片,對(duì)15次諧波而言至少會(huì)引起1.67%的誤差,而在實(shí)際諧波測(cè)量中一般測(cè)到30次或更多次諧波,因此現(xiàn)場(chǎng)監(jiān)測(cè)單元中A/D轉(zhuǎn)換器的分辨率應(yīng)保證為14位或14位以上。本文采用AD73360作為采樣系統(tǒng)的模數(shù)轉(zhuǎn)換芯片。它的六路輸入通道可被分為三對(duì),以分別對(duì)應(yīng)電力系統(tǒng)中的三相。該芯片可以8 kHz,16 kHz,32 kHz,64 kHz的采樣速率同時(shí)進(jìn)行六通道的信號(hào)采樣。AD73360可滿足裝置對(duì)高速采樣的要求。AD73360與FPGA的連接如圖3所示。

圖3 AD73360與FPGA的連接

2.2 NiosⅡ軟核處理器

基于32位RISC嵌入式軟核NiosⅡ的SoPC,有著其他SoPC(如基于FPGA嵌入式IP硬核SoPC)不可比擬的優(yōu)勢(shì)。采用NiosⅡ軟核處理器,用戶(hù)將不會(huì)局限于一般的處理器技術(shù)而是根據(jù)自己的標(biāo)準(zhǔn)裁剪和定制處理器,按照需要選擇合適的外設(shè)、存儲(chǔ)器和接口,輕松集成自己專(zhuān)有的功能,比如DSP、用戶(hù)邏輯等。這非常有利于設(shè)計(jì)高次諧波這種計(jì)算量大且控制邏輯復(fù)雜的系統(tǒng)。

為了滿足今后的性能要求,該電能質(zhì)量監(jiān)測(cè)系統(tǒng)應(yīng)能隨時(shí)被改進(jìn)升級(jí)。可以加入多個(gè)NiosⅡCPU、定制指令集、硬件加速器等,以達(dá)到更好的性能目標(biāo)。還可以通過(guò)Avalon交換架構(gòu)調(diào)整系統(tǒng)性能,該架構(gòu)支持多種并行數(shù)據(jù)通道可實(shí)現(xiàn)大吞吐量的應(yīng)用。

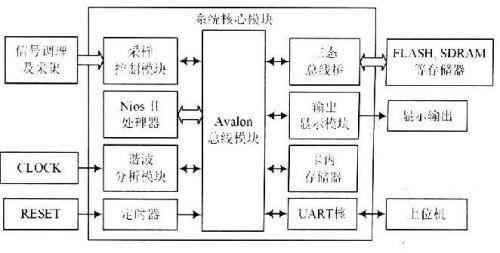

圖4 電能質(zhì)量監(jiān)測(cè)系統(tǒng)硬件結(jié)構(gòu)框圖

2.3 硬件系統(tǒng)平臺(tái)設(shè)計(jì)

圖4是整個(gè)系統(tǒng)的硬件結(jié)構(gòu)框圖。系統(tǒng)組成主要包括:

(1)系統(tǒng)核心模塊采用STRATIX系列的EPlS25型的FPGA,它包含:10個(gè)DSP模塊、25 660個(gè)邏輯單元、48個(gè)嵌入式乘法器、RAM總量高達(dá)1 922576 b,6個(gè)數(shù)字鎖相環(huán)、可用的I/O口最多達(dá)到702個(gè)。它是一款采用高性能結(jié)構(gòu)體系的PLD器件,結(jié)合了強(qiáng)大內(nèi)核性能,大存儲(chǔ)器,DSP功能,高速I(mǎi)/O和模塊化設(shè)計(jì)。其內(nèi)嵌的DSP模塊,提供了高于DSP處理器的數(shù)據(jù)處理能力,可以完成較為耗費(fèi)資源的乘法器單元。這些資源對(duì)一個(gè)電能質(zhì)量監(jiān)測(cè)系統(tǒng)來(lái)說(shuō)是已經(jīng)綽綽有余。

(2)NiosⅡ軟核處理器是整個(gè)系統(tǒng)模塊的CPU,它的具體特性已在前面詳細(xì)敘述。NiosⅡ軟核處理器除了要協(xié)調(diào)控制各個(gè)硬件設(shè)備外,電能參數(shù)相關(guān)數(shù)據(jù)的軟件算法也要在此執(zhí)行。

(3)Avalon交換式總線由SoPC Buiider自動(dòng)生成,它是一種用于系統(tǒng)CPU和外設(shè)之間的內(nèi)聯(lián)總線。傳統(tǒng)的總線結(jié)構(gòu)缺點(diǎn)是每次只能有一個(gè)主機(jī)能接入總線,導(dǎo)致帶寬瓶頸。而在Avalon總線結(jié)構(gòu)里,總線主機(jī)不搶占總線本身。Avalon交換結(jié)構(gòu)可實(shí)現(xiàn)數(shù)據(jù)在外設(shè)與性能最佳數(shù)據(jù)通道之間的無(wú)縫傳輸,并且它同樣支持用戶(hù)設(shè)計(jì)的片外處理器和外設(shè)。

(4)諧波分析模塊采用內(nèi)嵌的DSP對(duì)采集過(guò)來(lái)的16位數(shù)字信號(hào)進(jìn)行處理,輸入電能計(jì)量指標(biāo)參數(shù)的處理算法程序,將結(jié)果暫存在片內(nèi)存儲(chǔ)器,最后NiosⅡ軟核控制單元通過(guò)RS 232或.RS 485串口完成數(shù)據(jù)的傳輸和人機(jī)對(duì)話。諧波是一個(gè)周期性的正弦波分量,其頻率為基波頻率的整數(shù)倍。進(jìn)行諧波變換的方法很多,本文采用的是FFT,完成電壓有效值、電流有效值、有功功率、無(wú)功功率、視在功率、頻率、功率因子和穩(wěn)態(tài)諧波分量等檢測(cè)。

以上是本文提出的一個(gè)基于NiosⅡ的基本電能質(zhì)量監(jiān)測(cè)系統(tǒng)的硬件平臺(tái)。根據(jù)不同要求,還可以采取往系統(tǒng)核心模塊里添加DMA、自定義模塊等措施,從而形成功能更加完善的電能質(zhì)量監(jiān)測(cè)系統(tǒng)。

3 電能質(zhì)量檢測(cè)系統(tǒng)軟件設(shè)計(jì)

3.1 SoPC Builder設(shè)計(jì)

對(duì)應(yīng)系統(tǒng)的硬件平臺(tái)結(jié)構(gòu),添加NiosⅡProcessor,選擇其為快速型,以確保系統(tǒng)的速度性能。再添加SPI,PIO,Character LCD,F(xiàn)LASH Memory,Avalon Tristate Bridge,SDRAM Controller,On chip Memory,DSP,timer這些模塊。設(shè)置好模塊的各項(xiàng)參數(shù)后,點(diǎn)擊System控件里的兩個(gè)選項(xiàng)為各模塊主動(dòng)分配地址和中斷。然后在NiosⅡMore“CPU”Setting里選Reset Address為FLASH,選Exception AddFess為SDR-AM。最后點(diǎn)擊Generate生成對(duì)應(yīng)的ptf文件。這樣系統(tǒng)的SoPC Buider設(shè)計(jì)基本完成。

3.2 NiosⅡIDE設(shè)計(jì)

進(jìn)入NiosⅡIDE后新建一個(gè)應(yīng)用工程,選擇ptf文件和Black Project,這樣一個(gè)基于已有SoPC的空白應(yīng)用工程建立完畢。然后在System Library里進(jìn)行必要工程設(shè)置。接著將電能參數(shù)算法的C程序填入工程里,再進(jìn)行軟件的編譯調(diào)試等。調(diào)試完畢后,一并將所有程序與可執(zhí)行文件全下載到FPGA上。至此,一個(gè)基于NiosⅡ的電能質(zhì)量監(jiān)測(cè)SoPC設(shè)計(jì)完成。

4 結(jié)果分析

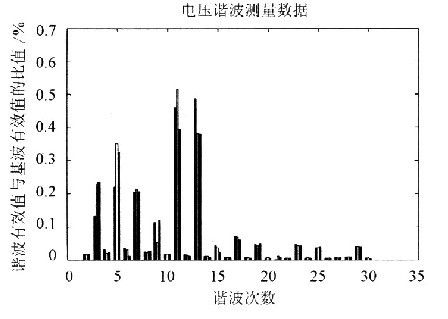

電能質(zhì)量檢測(cè)結(jié)果主要包括電流、電壓的諧波分析數(shù)據(jù)、電功率測(cè)量值數(shù)據(jù)、供電電壓的測(cè)量數(shù)據(jù)、頻率的測(cè)量數(shù)據(jù)、三相不平衡度的測(cè)量數(shù)據(jù)、閃變的測(cè)量數(shù)據(jù)以及誤差分析等。從實(shí)測(cè)數(shù)據(jù)中可以看出,由于各種非線性電力電子裝置的廣泛使用,增加了高次諧波的含有量,現(xiàn)以三相電壓的諧波分析數(shù)據(jù)為例,得到第2~30次諧波的諧波含有率,即第n次諧波有效值與基波有效值的比值,如柱狀圖5所示。

圖5 電壓諧波有效值與基波有效值的比值

圖5中,連續(xù)的三根柱子分別代表A相、B相、C相的電壓諧波含有率。可以看出,奇數(shù)次諧波的諧波含有率明顯比偶數(shù)次諧波含有率高,其中以第3,5,7,9,1l,13諧波含量最為明顯,且A,B,C三相電壓相應(yīng)的諧波含有率差不多,除了B相的第9次和第13次諧波含有率比A相,C相略高一些。應(yīng)該盡可能地降低諧波含有量,比如從電源電壓、線路阻抗、負(fù)荷特性等方面著手,降低高次諧波含有量。

5 結(jié)語(yǔ)

本文提出一種基于NiosⅡ的電能質(zhì)量監(jiān)測(cè)系統(tǒng)的設(shè)計(jì)方案,可以實(shí)現(xiàn)對(duì)電能信號(hào)的采集、處理、存儲(chǔ)與顯示等功能,達(dá)到實(shí)時(shí)系統(tǒng)的要求。但由于經(jīng)驗(yàn)及技術(shù)有限,該系統(tǒng)在某些方面還有待提高。譬如如何進(jìn)一步減小三相不平衡度、閃變的危害等。本系統(tǒng)利用了可配置的優(yōu)勢(shì),有興趣的朋友可以在此基礎(chǔ)上根據(jù)自己的具體需求來(lái)進(jìn)行相應(yīng)的填充、修改、完善,得到更優(yōu)秀的電能質(zhì)量監(jiān)測(cè)SoPC。