1、引言

電荷耦合器件(CCD)是一種光電轉(zhuǎn)換式圖像傳感器,,它將圖像信號(hào)直接轉(zhuǎn)換成電信號(hào),。由于 CCD 具有集成度高、低功耗,、低噪聲,、測(cè)量精度高、壽命長(zhǎng)等諸多優(yōu)點(diǎn),,因此在精密測(cè)量,、非 接觸無(wú)損檢測(cè)、文件掃描與航空遙感等領(lǐng)域中得到了廣泛的應(yīng)用[1],。面陣列CCD成像器件分為 全幀轉(zhuǎn)移(Full Frame)CCD,、幀轉(zhuǎn)移(Frame. Transfer)CCD、行間轉(zhuǎn)移(Interline Transfer) CCD 三種類型,。行間轉(zhuǎn)移CCD 中的成像區(qū)與存儲(chǔ)區(qū)呈列交錯(cuò),,因此不需要機(jī)械快門,速度最 快且能連續(xù)成像,;同時(shí)在真正的成品中,,會(huì)在每個(gè)像素上加微透鏡從而彌補(bǔ)了填充因子小的缺 點(diǎn)。典型的消費(fèi)級(jí)的相機(jī),,一般用的都是行間轉(zhuǎn)移CCD,。

CCD器件需要驅(qū)動(dòng)脈沖信號(hào)才能正常工作,而驅(qū)動(dòng)電路就為CCD提供所需的時(shí)序邏輯和相關(guān) 的電壓信號(hào),,所以驅(qū)動(dòng)電路的研制就顯得十分的重要,。CCD的驅(qū)動(dòng)電路主要由供電模塊、驅(qū)動(dòng)器 電路和驅(qū)動(dòng)時(shí)序產(chǎn)生電路三部分組成。常用的幾種CCD 驅(qū)動(dòng)時(shí)序產(chǎn)生方法包括:中小規(guī)模數(shù)字 邏輯電路驅(qū)動(dòng)方法,、使用只讀存儲(chǔ)器方法,、微處理器或數(shù)字信號(hào)處理器(DSP)、使用可編程邏輯 器件,,CPLD或FPGA等,。本文中驅(qū)動(dòng)時(shí)序采用第三種方法可編程邏輯器件FPGA來(lái)實(shí)現(xiàn)。

2,、Kodak CCD KAI-0340 簡(jiǎn)介

KAI-0340 是Kodak 公司生產(chǎn)的一款行間轉(zhuǎn)移型面陣CCD,,單(雙)通道輸出可選擇(本文中選用單通道輸出模式)。主要的性能參數(shù)如下:

具有以下特征:

·水平,、垂直均為兩相驅(qū)動(dòng),,其中一相垂直轉(zhuǎn)移時(shí)鐘為三電平

·電子快門

·低暗電流、高靈敏度

·每行左右兩端各有 24 個(gè)暗像元,,可以作為暗電平參考

3,、CCD 供電模塊

為了保證 CCD KAI-0340S 正常工作,需要的驅(qū)動(dòng)電壓和直流偏置電壓具體要求如表1 所示,。

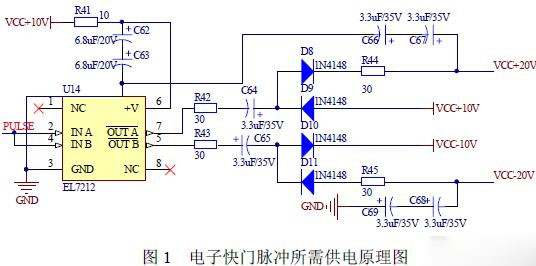

對(duì)表 1 進(jìn)行分析可知:只需+15V 和-9V 兩組電壓就可實(shí)現(xiàn)對(duì)CCD 的基本偏置,;H1、H2 水 平移位驅(qū)動(dòng)工作電壓峰峰值為5V(-5V~0V),,R 復(fù)位驅(qū)動(dòng)的工作電壓峰峰值也為5V(-3V~+2V),, 因此取+5V 作為水平和復(fù)位驅(qū)動(dòng)時(shí)鐘的工作電壓;V1 垂直轉(zhuǎn)移的工作電壓9V(-9V~0V),,V2 為三電平(-9V,、0V、+9V),, 從而取±9V 作為垂直驅(qū)動(dòng)時(shí)鐘的工作電壓,;電子快門脈沖電壓為 VAB~VAB+40V(峰峰值為40V),需要±20V 電路來(lái)實(shí)現(xiàn),。同時(shí)結(jié)合整個(gè)CCD 成像系統(tǒng)供電 需求,,得出所需電壓電平種類為:+3.3V,+5V,,±9V,,+10V,+15V,,±20V,。為了提高系統(tǒng) 的電源效率,設(shè)定整個(gè)供電系統(tǒng)的外部輸入電壓為三種:+5V,,-10V,,+15V,。+9V、+10V 和+3.3V 電壓通過(guò)集成穩(wěn)壓器LT 1764EQ 和LT 1764EQ-3.3 來(lái)實(shí)現(xiàn),;-9V 通過(guò)-10V 電壓分壓得到,;產(chǎn)生 電子快門高壓脈沖所需±20V 電源采用±10V 脈沖倍壓電路實(shí)現(xiàn),具體電路的原理圖如圖1 所示[2],。經(jīng)實(shí)際應(yīng)用表明,,電源模塊滿足各功能電路所需電壓及功耗。

4,、驅(qū)動(dòng)器電路

面陣 CCD KAI-0340S 的驅(qū)動(dòng)時(shí)鐘分為水平移位時(shí)鐘,、復(fù)位時(shí)鐘、垂直轉(zhuǎn)移時(shí)鐘,、電子快門 時(shí)鐘四種,需要的驅(qū)動(dòng)電壓具體要求見表1,。

CCD 在單端輸出模式下,, 水平移位時(shí)鐘對(duì)應(yīng)圖像傳感器的管腳連接如下: H1=H1S(5)+H1BL(4)+H2BR(9); H2=H2S(7)+H2BL(3)+H1BL(8)。H1,,H2,,R 共用一片74AC04 驅(qū)動(dòng)器,每個(gè)時(shí)鐘使用兩個(gè)門驅(qū)動(dòng),,再配合濾波電容和鉗位電路便可以實(shí)現(xiàn)對(duì)面陣CCD 的水平 和復(fù)位驅(qū)動(dòng),。

垂直轉(zhuǎn)移需要 V1、V2 兩相驅(qū)動(dòng)時(shí)鐘,,其中V2 為三電平,,因?yàn)镕PGA 產(chǎn)生的信號(hào)只有‘0’ 和‘1’兩種狀態(tài),所以需要將信號(hào)V2 分解成V2HM 和V2ML 兩個(gè)信號(hào),。V1 通過(guò)一片EL7212 進(jìn)行驅(qū)動(dòng),,配合濾波電容和鉗位電路實(shí)現(xiàn)。

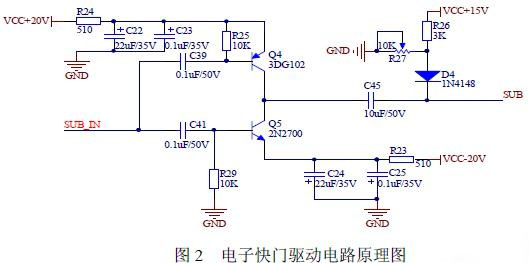

V2 驅(qū)動(dòng)器選用一片MAX4426,,通過(guò)V2HM 控制其 電源端(將V2HM 反向),。當(dāng)V2HM 為高的時(shí)候,MAX4426 產(chǎn)生峰峰值9V 的輸出信號(hào),,當(dāng) V2HM 由高變低時(shí),,MAX4426 的電源端被升到18V,從而產(chǎn)生出滿足要求的三電平信號(hào)V2,。 電子快門脈沖電壓為 VAB~VAB+40V(峰峰值為40V),,使用分立元件產(chǎn)生,具體電路的原 理圖如圖2 所示,。

5,、CCD 驅(qū)動(dòng)時(shí)序設(shè)計(jì)

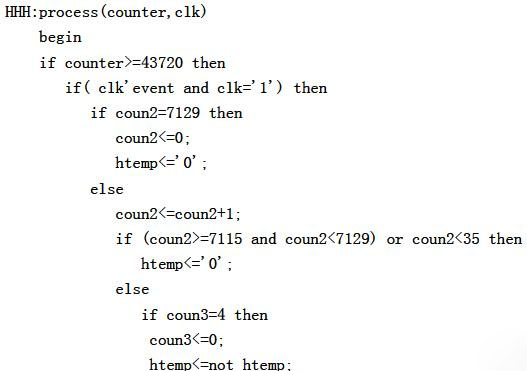

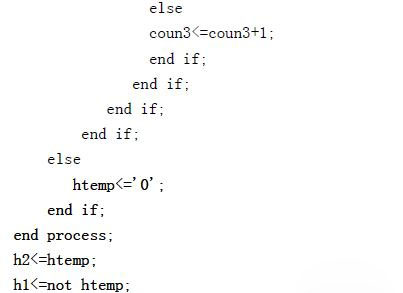

KAI-0340S工作需要6路驅(qū)動(dòng)信號(hào):分別是兩相水平移位寄存器時(shí)鐘H1、H2;復(fù)位脈沖時(shí)鐘 RL,;兩相垂直轉(zhuǎn)移時(shí)鐘V1,、V2(分解成V2HM和V2ML);電子快門時(shí)鐘SUB,。CCD成像的一個(gè) 工作周期分三個(gè)階段:曝光階段,,行間轉(zhuǎn)移階段和水平移位階段。CCD工作時(shí),,首先底層出現(xiàn)電 子快門脈沖將光敏區(qū)的電荷清除,,電子快門脈沖之后開始圖像信號(hào)積分階段,積分完成后V2上 的高電平把光敏區(qū)的包含圖像信息的電荷包轉(zhuǎn)移到擋光的垂直CCD上,,接下來(lái)通過(guò)V1和V2的互補(bǔ) 時(shí)鐘逐行把垂直CCD中的電荷包轉(zhuǎn)移到水平CCD上,,再通過(guò)H1和H2的互補(bǔ)時(shí)鐘逐個(gè)把水平CCD上的電荷包轉(zhuǎn)移到浮置擴(kuò)散輸出節(jié)點(diǎn),進(jìn)行電荷測(cè)量供后續(xù)電路處理,,同時(shí)CCD又可進(jìn)行下一幀圖像 的曝光,。KAI-0340S的詳細(xì)驅(qū)動(dòng)時(shí)序關(guān)系參見其使用說(shuō)明書。其中實(shí)現(xiàn)H1和H2部分程序如下:

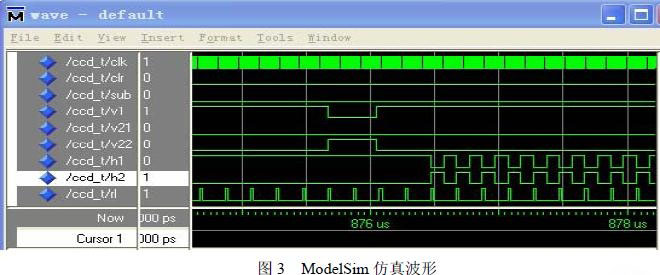

本文選用的FPGA 是Xilinx 公司的XC2S150,,一共有150,,000 個(gè)邏輯門,滿足整個(gè)系統(tǒng)的所有需求,;采用硬件描述語(yǔ)言VHDL 進(jìn)行邏輯設(shè)計(jì),,用ModelSim 仿真,關(guān)鍵部分的波形見圖3,。

6,、結(jié)論

本文的創(chuàng)新是:先將V2 三電平進(jìn)行分解,之后巧妙地利用兩個(gè)驅(qū)動(dòng)器和鉗位電路來(lái)實(shí)現(xiàn)三 電平階梯波形的時(shí)序驅(qū)動(dòng),;采用FPGA 器件來(lái)設(shè)計(jì)行間轉(zhuǎn)移面陣CCD 驅(qū)動(dòng)時(shí)序,。系統(tǒng)設(shè)計(jì)完成后, 由示波器測(cè)試各路輸出的驅(qū)動(dòng)信號(hào),,所顯示的波形與仿真波形一致,,得到令人滿意的結(jié)果。因 此本文的驅(qū)動(dòng)電路設(shè)計(jì)方案能夠滿足的 KAI-0340 的性能要求,,可以用來(lái)驅(qū)動(dòng)行間轉(zhuǎn)移型面陣 CCD KAI-0340S,。