1 引言

CF 卡(Compact Flsah Card)由于價(jià)格便宜、存儲容量大、體積小、兼容性好等優(yōu)點(diǎn)被廣泛應(yīng)用于嵌入式產(chǎn)品。然而現(xiàn)有的CF 卡接口電路存在接口復(fù)雜,穩(wěn)定性不高等缺點(diǎn),不能滿足客戶的需求。通過深入研究ARM 處理器AT91RM9200 的外部總線接口(EBI)、CF 卡和CPLD 的工作原理,提出利用CPLD來改進(jìn)CF 卡接口電路以解決現(xiàn)有接口電路中存在的缺點(diǎn)。

通過深入研究ARM 處理器AT91RM9200 的外部總線接口(EBI)及CF 卡、CPLD 的工作原理,設(shè)計(jì)了新的CF 卡接口電路。新的CF 卡接口電路中采用了CPLD 來代替一般CF 卡接口電路中的雙向緩沖器、與非門等所有邏輯器件,通過現(xiàn)場對CPLD 編程來實(shí)現(xiàn)不同的邏輯功能。實(shí)驗(yàn)表明,該電路更加簡單、靈活、穩(wěn)定、高速,對接口電路的設(shè)計(jì)有重要的參考價(jià)值。

2 器件簡介

2.1 外部總線接口

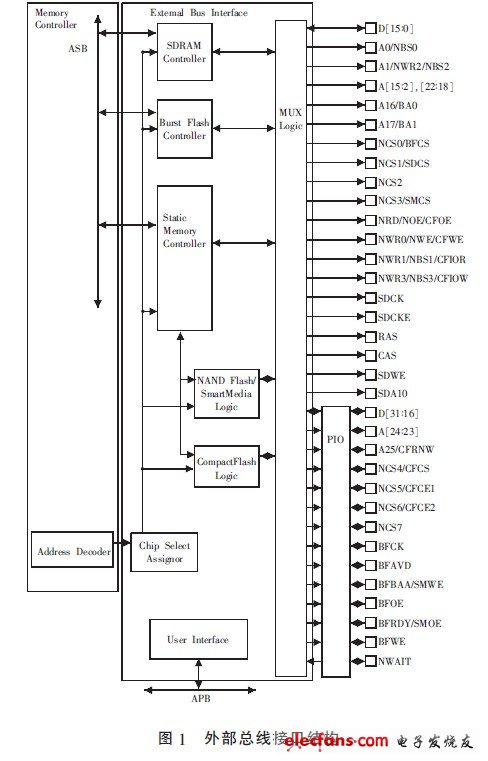

系統(tǒng)采用了以ARM920T 為內(nèi)核的AT91RM9200作為微處理器,它是完全圍繞ARM920T Thumb 處理器構(gòu)建的系統(tǒng)。它有豐富的系統(tǒng)與應(yīng)用外設(shè)及標(biāo)準(zhǔn)的接口,包括一個(gè)高速片上SRAM 工作區(qū)及一個(gè)低等待時(shí)間的外部總線接口(EBI)以完成應(yīng)用所要求的片外存儲區(qū)和內(nèi)部存儲器映射外設(shè)配置的無縫連接。外部總線接口結(jié)構(gòu)如圖1 所示。

EBI 通過集成電路支持CF 卡與SmartMedia 協(xié)議,從而極大地降低了對外部組件的需求。此外,EBI可處理多達(dá)8 個(gè)外設(shè)的數(shù)據(jù)傳輸,每個(gè)外設(shè)分配8 個(gè)在內(nèi)置存儲控制器中定義的地址空間。數(shù)據(jù)通過16 位或32 位數(shù)據(jù)總線進(jìn)行傳輸,地址總線高達(dá)26位,8個(gè)芯片選擇口(NCS[7:0])和在不同外部存儲控制器間復(fù)用的多個(gè)控制引腳進(jìn)行復(fù)用。

2.2 CF 卡

CF 卡(Compact Flash Card)是采用Flash Memory技術(shù)的存儲卡,具有體積小、價(jià)格低廉、兼容性強(qiáng)、存儲量大等優(yōu)點(diǎn)。CF 卡支持三種接口模式,分別是PCCard Memory Mode、PC Card I/O Mode、True IDEMode。因?yàn)門rue IDE Mode 不經(jīng)常使用,故接口電路以PC Card Memory Mode 和PC Card I/O Mode設(shè)計(jì)。

2.3 CPLD

CPLD(Complex Programmable Logic Device)是一種較PLD 復(fù)雜的邏輯元件[2],是一種用戶根據(jù)各自需要而自行構(gòu)造邏輯功能的數(shù)字集成電路。其基本設(shè)計(jì)方法是借助集成開發(fā)軟件平臺,用原理圖、硬件描述語言等方法,生成相應(yīng)的目標(biāo)文件,通過下載電纜(“在系統(tǒng)”編程)將代碼傳送到目標(biāo)芯片中,實(shí)現(xiàn)設(shè)計(jì)的數(shù)字系統(tǒng)。

該文采用的CPLD 是Altera 公司的MAX7000S系列的EPM7128SQL100-10。它有84 個(gè)引腳,其中5 根用于ISP(IN System Programmable)下載,可方便的對其進(jìn)行“在系統(tǒng)”編程。EPM7128SQL100-10支持對電壓工作,可以利用Altera 公司的第四代開發(fā)平臺quartus Ⅱ方便地進(jìn)行仿真、綜合和下載。

3 硬件接口電路設(shè)計(jì)

CF卡的硬件接口電路" border="0" height="471" src="http://files.chinaaet.com/images/20111130/c72d4d13-4e9d-46e5-9a9c-543c8c3de39d.jpg" width="532" />

硬件接口電路的電路圖如圖2 所示。在此電路中用CPLD 來實(shí)現(xiàn)一般CF 卡接口電路中的雙向緩沖器和與非門等一些邏輯器件的邏輯功能,使接口電路變的更為簡單、穩(wěn)定、高速,而且可以通過現(xiàn)場修改程序來實(shí)現(xiàn)不同的功能。

CF 卡中的_CD1、_CD2 是CF 卡是否安裝的狀態(tài)檢測信號,在CF 卡中接地。當(dāng)CF 卡沒有安裝時(shí),電路中_CD1、_CD2 由上拉電阻將其輸出拉為高電平;當(dāng)CF 卡安裝時(shí),_CD1、_CD2 由CF 卡接地輸出為低電平,_CD1、_CD2 相當(dāng)于CF 卡的總開關(guān)。在實(shí)際接口電路中_CD1、_CD2 要接10 kΩ 的上拉電阻。

將片選任務(wù)寄存器的CS4A 編程為1 則可使能EBI 的復(fù)用引腳NCS4/CFCS、NCS5/CFCE1、NCS6/CFCE2 為CompactFlash 信號CFCS、CFCE1、CFCE2,使能NOE/NRD/CFOE、NWR0/NEW/CFWE、NWR1/NBS1/CFIOR、NWR3/NBS3/CFIOW、A25/CFRNW為Compact Flash 信號CFOE、CFWE、CFIOR、CFIOW、CFRNW。這樣就可以通過訪問保留給NCS4 的地址空間來訪問外部的CF 卡。在NCS4 的地址空間中用當(dāng)前的傳輸?shù)刂穪矸直鍵/O 模式,通用存儲模式是標(biāo)志存儲模式。傳輸?shù)刂房偩€的A23 用作I/O 模式選擇。該文CF 卡用A22/REG 來分離通用存儲模式和標(biāo)志存儲模式。

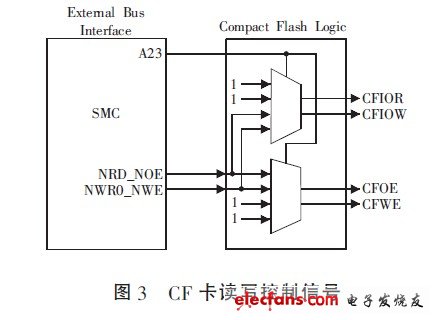

在I/O 模式下,CompactFlash 的邏輯驅(qū)動CFIOR與CFIOW 信號上SMC 的讀寫信號,此時(shí)CFOE 與CFWE 信號失效。同樣在通用存儲模式和標(biāo)志存儲模式下驅(qū)動CFOE 與CFWE 信號上的SMC,CFIOR與CFIOW 信號失效。該邏輯如圖3 所示。

CFOE 與CFWE 通過CPLD 和CF 卡的OE 與WE連接起來,這是CF 卡在Memory Mode 的讀寫使能。

CFIOE 與CFIOW 通過是I/O Mode 的使能。除了使能信號外,其他的信號對2 種模式都是相同的。

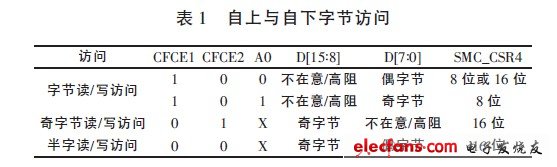

CFCE1 與CFCE2 信號使能CF 卡的數(shù)據(jù)總線由上或是由下訪問,具體信息見表1。只有當(dāng)NCS4 引腳上的SMC 配置為驅(qū)動8 位存儲器時(shí)才可進(jìn)行奇字節(jié)訪問,NCS4 地址空間中的片選寄存器必須如表1所示進(jìn)行設(shè)置。

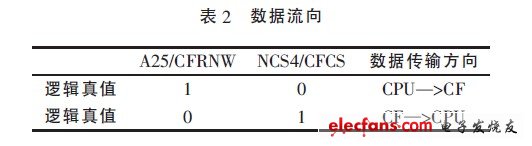

_CD1、_CD2 為低電平時(shí),CPU 的地址總線的低11 位A[10∶0]于CF 卡的地址總線A[10∶0]連通,CPU的數(shù)據(jù)總線的低16 位D[15∶0]與CF 卡的地址總線D[15∶0]連通。CPU 的A25/CFRNW 信號是數(shù)據(jù)流的方向的,NCS4/CFCS 信號是數(shù)據(jù)總線的傳輸使能。詳細(xì)內(nèi)容請參閱表2。

CPU 是高速器件,CF 卡是低速器件,在CPU 給CF 卡傳輸數(shù)據(jù)的時(shí)候就會發(fā)生因?yàn)榻邮账俣嚷鴣G失數(shù)據(jù)的情況。所以需要用_WAIT 信號來延遲CPU 的發(fā)送,這樣才能使CPU 的發(fā)送時(shí)序與CF 卡的接受時(shí)序匹配,使得數(shù)據(jù)的傳輸正確無誤。實(shí)際電路中CF 卡的_WAIT 信號通過CPLD 來控制CPU 的NWAIT 信號,_WAIT 要接10 kΩ 的上拉電阻。RDY/BSY 是CF 卡的工作狀態(tài)信號,當(dāng)RDY/BSY 為1 時(shí),CF 卡已經(jīng)做好準(zhǔn)備接收新的數(shù)據(jù);當(dāng)RDY/BSY 為0 時(shí),CF 卡正在接受數(shù)據(jù),這個(gè)信號也要接個(gè)10 kΩ上拉電阻。CF 卡的復(fù)位RESET 信號也是由系統(tǒng)的復(fù)位nRESET 信號在CPLD 中反相后產(chǎn)生的,以保持和系統(tǒng)的復(fù)位信號同步。

4 CPLD 程序開發(fā)

CPLD 程序在quartus Ⅱ下用Verilog HDL 語言編寫。程序經(jīng)過編譯后,下載到CPLD 中固化。連接電路板和CF 卡,對CF 卡進(jìn)行數(shù)據(jù)的讀寫操作,測試結(jié)果表明數(shù)據(jù)傳輸正確無誤,且傳輸速率更高。

5 結(jié)束語

該文重點(diǎn)研究了如何利用CPLD 來連接基于ARM 的嵌入式系統(tǒng)與CF 卡。其中使用的CPLD 不但簡化了接口電路,使其適合現(xiàn)場編程,同時(shí)改進(jìn)的接口電路還適合產(chǎn)生各種復(fù)雜組合邏輯和時(shí)序邏輯。這種存儲技術(shù)的正確性已在電路板上得到驗(yàn)證,它為基于ARM 的嵌入式系統(tǒng)的CF 卡存儲提供了一種有效的解決方案。