中心議題:

- MOSFET損耗問題

- 功率MOSFET結(jié)構(gòu)優(yōu)劣對比

- 橫向/分裂閘/超級接面FOM比較

解決方案:

- 確認(rèn)效益因數(shù)

- 超級接面功率MOSFET

采用超級接面結(jié)構(gòu)設(shè)計(jì)的新型低壓MOSFET已逐漸在市場上嶄露頭角,其不僅可克服現(xiàn)有功率MOSFET結(jié)構(gòu)的缺點(diǎn),亦能達(dá)到低RDS(on)、低QG和低QGD等特性,確保在兼顧晶片尺寸與功耗的前提下,提升DC-DC轉(zhuǎn)換效率與功率密度。

藉由對同步交流對交流(DC-DC)轉(zhuǎn)換器的功耗機(jī)制進(jìn)行詳細(xì)分析,可以界定必須要改進(jìn)的關(guān)鍵金屬氧化物半導(dǎo)體場效電晶體(MOSFET)參數(shù),進(jìn)而確保持續(xù)提升系統(tǒng)效率和功率密度。

分析顯示,在研發(fā)功率MOSFET技術(shù)的過程中,以往常見以QG和QGD(意即RDS(on)×QG和RDS(on)×QGD)為基礎(chǔ)的因數(shù)(FOM)已無法滿足需求,若堅(jiān)持采用固定因數(shù),將可能導(dǎo)致技術(shù)選擇無法達(dá)成最佳化。藉由此次分析的啟示,工程師們已定義一套FOM以應(yīng)用于新的低壓功率MOSFET技術(shù)研發(fā)。由此產(chǎn)生的30伏特(V)技術(shù)以超級接面(Superjunction)為基礎(chǔ)概念,是DC-DC轉(zhuǎn)換器的理想選擇;相較于橫向和分裂閘極溝槽MOSFET等競爭技術(shù),該技術(shù)可同時提供特定的低RDS(on)、QG、QGD、QOSS和高度閘極回跳抑制。

MOSFET損耗問題加劇 催生新功耗分析技術(shù)

多相同步降壓轉(zhuǎn)換器是微控制器(MCU)以及其他運(yùn)算密集型積體電路(IC),如數(shù)位訊號處理器(DSP)和繪圖處理器(GPU)供電的拓?fù)浣Y(jié)構(gòu)選擇。在同步降壓轉(zhuǎn)換器內(nèi),兩個功率MOSFET串聯(lián)形成半橋結(jié)構(gòu)。高處的MOSFET做為控制單結(jié)型FET;低處的MOSFET則為同步FET。

此電路拓?fù)溲葑兊年P(guān)鍵點(diǎn)在于2000年時,引進(jìn)Pentium 4微處理器以及相關(guān)的ATX12V電源規(guī)范,其中的功率軌(即轉(zhuǎn)換電壓)從5伏特提高至12伏特,以達(dá)成微處理器須要快速增加電流的要求。因此而產(chǎn)生的工作周期變化使得功率MOSFET在性能優(yōu)化方面發(fā)生重大變革,并全面采用QGD×RDS(on)和QG×RDS(on)等效益指數(shù)作為功率MOSFET的性能指標(biāo)。然而,過去10年以來,特定尺寸產(chǎn)品中此類FOM和RDS(on)已降低約十倍,QG和QGD已不再是影響功率MOSFET功耗的主要因素。

就控制FET而言,MOSFET封裝和印刷電路板(PCB)連線的寄生電感所產(chǎn)生的功耗可能超過由QGD產(chǎn)生的損耗。降低寄生電感的需求推動Power SO8封裝的普及化,并使整合動力的概念于2002年產(chǎn)生,意即將控制和同步FET與MOSFET驅(qū)動器整合于四方形平面無接腳封裝(QFN)中,此概念于2004年獲英特爾(Intel)DrMOS規(guī)范采用。

為因應(yīng)功率MOSFET多面性的損耗,一系列日趨復(fù)雜的運(yùn)算方式和效益指數(shù)逐被提出。在功耗機(jī)制研究領(lǐng)域中,最被看好的技術(shù)是利用如TSuprem4和Medici等TCAD工具制作詳細(xì)的行為模型,并結(jié)合詳細(xì)的電路模擬(如PSpice),進(jìn)而產(chǎn)生詳細(xì)的功耗分析結(jié)果。雖然此方法可針對不同的功耗機(jī)制進(jìn)行深入分析,但分析結(jié)果須轉(zhuǎn)換成一套以MOSFET參數(shù)為基礎(chǔ)的FOM,以用于新技術(shù)的研發(fā)。

確認(rèn)效益因數(shù)有助技術(shù)最佳化

為使DC-DC轉(zhuǎn)換中采用的MOSFET技術(shù)達(dá)成最佳化,首先須確定對目標(biāo)應(yīng)用的性能造成影響的關(guān)鍵元件參數(shù)為何。透過功耗機(jī)制分析得出的這些參數(shù)通常為一組關(guān)鍵效益因數(shù)(性能指標(biāo)),在確認(rèn)任何效益因數(shù)的有效性為實(shí)際限值(如可用尺寸和成本)時,功耗分析所采用的假設(shè)前提相當(dāng)重要。表1列出了用于新的功率MOSFET技術(shù)研發(fā)的FOM。

前三項(xiàng)性能指標(biāo)已廣泛用于評估技術(shù)的適用性,因此無須多作介紹,其僅用于告知設(shè)計(jì)工程師須盡可能減少單位面積上的RDS(on)值(即Sp.RDS(on)),以確保晶片在有限的封裝尺寸內(nèi)達(dá)成最高的功效。且對于特定的RDS(on),要盡量降低MOSFET電容CGS和CGD,以達(dá)成最低開關(guān)損耗。

第四個FOM為COSS,與降低輸出電容有關(guān),其重要性將逐漸增加。原因來自兩方面:第一,同步FET的閘極電荷損失已大幅降低,輸出電容充放電時產(chǎn)生的電荷損耗水準(zhǔn)已大致相當(dāng)。第二,控制FET的QGD相當(dāng)微小,以致于影響電壓升降時間的因素為電路電感對輸出電容進(jìn)行充電的時間,而非電路提供所需閘控充電的能力。在此請?zhí)貏e注意,表1中未列出儲存電荷Qrr,并非Qrr可忽略不計(jì),而是因?yàn)椴捎门c上述降低Sp.RDS(on)相同的技術(shù)使其獲得改善,此技術(shù)包含提高單元密度(導(dǎo)因于本體偏置效應(yīng))和削減漂移區(qū)塊等。

設(shè)計(jì)一款高性能MOSFET須在特定的參數(shù)之間做出權(quán)衡。例如,欲改善RDS(on)×QGD,可透過加大單元間距、犧牲Sp.RDS(on)而完成,亦可透過增加一個連接源極的閘極遮罩、犧牲RDS(on)×QOSS而完成。為避免產(chǎn)生不符理想的元件結(jié)構(gòu),須綜合這些FOM。此概念已被應(yīng)用于生產(chǎn)綜合加權(quán)同步FET(FET CWS)FOM,即綜合考量閘極電荷和輸出電容功耗的效應(yīng)。此種FOM組合有助于對元件性能做出更精確的評估,此外,透過將轉(zhuǎn)換電壓和閘極驅(qū)動電壓(VIN和VDR)合并后,QG和QOSS的相對重要性取決于應(yīng)用方式,進(jìn)而確保改善后的閘極電荷不會對輸出電容產(chǎn)生不利影響,反之亦然。

在理想狀態(tài)下,對于CWS和ACS FOM而言,QG應(yīng)在VDS=0和VGS=4.5伏特的條件下進(jìn)行測量。若無法達(dá)成上述條件,可根據(jù)閘極電荷曲線,利用公式1計(jì)算QG。公式中的QG1、QG2分別為VDS1和VDS2條件下測得的閘極電荷,此兩點(diǎn)均取自于閘極電荷曲線中QGD的部分之后。

QG=4.5V×(QG1-QG2)/(VDS1-VDS2)¨¨¨¨(公式1)

輸出電荷是一般資料手冊中不會提及的另一參數(shù),但使用者可根據(jù)輸出電容進(jìn)行估算。當(dāng)轉(zhuǎn)換電壓為12伏特時,假設(shè)理想的pn接面電壓為0.7伏特,則QOSS可用公式2計(jì)算,其中Vm用以表示測量COSS時的電壓。

QOSS=5.45×COSS(Vm)×(Vm+0.7)1/2¨¨(公式2)

最終的目標(biāo)是確保MOSFET不會因?yàn)殡娙菪噪娏髁鬟^閘漏電容(CGD)而導(dǎo)致寄生性導(dǎo)通,當(dāng)快速VDS瞬變電流產(chǎn)生時,CGD會向CGS電容器充電,致使其電壓超過閾值。閘極回跳比率(Gate-bounce Ratio, GBr)即用于此目標(biāo);其本質(zhì)在于,當(dāng)漏極電壓升至輸入電壓電平時,如果所有流經(jīng)CGD電容器的電容性電流都流入MOSFET的CGS,這時,CGS電容器的電壓仍必須低于電壓閾值。此一比例可利用QGD1和QGS1的值從閘極電荷曲線中輕易取得,其中,QGD1是VDS=VIN(CGD徹底充電)和VDS=VGS(CGD已放電)之間的QGD部分,QGS1為VGS=0至電壓閾值之間的QGS部分。

對于控制FET方面而言,由于現(xiàn)代功率MOSFET的高增益特性,其電流升降時間由電路和源極電感決定,因此其余能耗則由電壓升降時間決定,而這些時間則取決于QGD FOM。因此,單獨(dú)為控制FET定義一個FOM組合并無實(shí)際益處。雖然CWS FOM可達(dá)成最佳化以應(yīng)用于同步FET,也可用于判定COSS、CGD和CGS之間由于裝置結(jié)構(gòu)所產(chǎn)生的不利影響,但是要注意的是,由于現(xiàn)代元件的QGD相當(dāng)?shù)停虼耍琎GD不再是控制FET中功耗的主要因素。另外,由于控制FET的體積相對較小,基本上面積限制晶片尺寸的問題已不復(fù)存在,因此,采用面積受到限制的FOM亦無法增加優(yōu)勢。

功率MOSFET結(jié)構(gòu)各有優(yōu)劣

圖1標(biāo)示出目前常用的多種功率MOSFET元件結(jié)構(gòu)。圖1a中所示的高密度溝槽結(jié)構(gòu)采用較低的Sp.RDS(on),但QG和QGD較高,因?yàn)榇藘蓚€參數(shù)與單元密度成正比。此種結(jié)構(gòu)通常用于開關(guān)損耗較無重要性的應(yīng)用中(如電池保護(hù))。可透過加大單元間距、于溝槽底部加上厚氧化膜以改善此結(jié)構(gòu)的開關(guān)性能。

圖1 功率MOSFET結(jié)構(gòu)

因單元間距加大而導(dǎo)致的Sp.RDS(on)上升的問題,可針對MOSFET漂移區(qū)進(jìn)行設(shè)計(jì)處理以解決,如圖1b所示的場平衡結(jié)構(gòu)。目前最常采用的結(jié)構(gòu)為分裂閘極(或電荷平衡)溝槽MOSFET,如圖1c所示。此種結(jié)構(gòu)閘極的正下方采用一個連接源極的遮罩電極,既可降低QGD,且透過應(yīng)用降低表面電場(RESURF)原理,漂移區(qū)的電阻降至最低。當(dāng)然,此結(jié)構(gòu)也有其缺點(diǎn),其需要較高的單元密度(因此閘極電容較高)以獲得RESURF狀態(tài);另外,采用連接源極的遮罩電極將產(chǎn)生額外的QG和QOSS,并增加制程的復(fù)雜程度。

相反地,和溝槽結(jié)構(gòu)相比,橫向MOSFET結(jié)構(gòu)(圖1d)由于可采用RESURF技術(shù)且毋須增加單元密度,因此,可達(dá)成出色的QG和QGD FOM。但由于橫向結(jié)構(gòu)須要將漂移區(qū)納入單元間距中,因此,可達(dá)成的單元密度較低,導(dǎo)致Sp.RDS(on)較低,進(jìn)而影響到在小面積封裝中為同步FET提供所需低RDS(on)的能力。

為了克服現(xiàn)有功率MOSFET結(jié)構(gòu)的缺點(diǎn),目前已經(jīng)開發(fā)出一種采用超級接面概念的新型結(jié)構(gòu)。低壓超級接面MOSFET元件的結(jié)構(gòu)如圖2所示,此結(jié)構(gòu)采用N-type和P-type矽區(qū)域交替形成一個多重RESURF結(jié)構(gòu),換言之,相當(dāng)于將橫向MOSFET結(jié)構(gòu)先平行放置后,再垂直擺放,進(jìn)而獲得RESURF結(jié)構(gòu)。這種結(jié)構(gòu)克服橫向結(jié)構(gòu)的單元間距限制,同時,在漂移區(qū)內(nèi)達(dá)成RESURF無需如同以往分裂閘結(jié)構(gòu)必須依賴增加單元密度,和在每個溝槽閘下方增加CDS和CGD電容器。完成真正為DC-DC轉(zhuǎn)換量身打造的元件結(jié)構(gòu)。

圖2 低壓超級接面結(jié)構(gòu)

橫向/分裂閘/超級接面FOM比較

采用QOSS與QG加權(quán)組合作為性能指標(biāo)的優(yōu)點(diǎn)如圖3所示,其中QG、QOSS及其組合分別針對三個不同的30伏特功率MOSFET結(jié)構(gòu)產(chǎn)生RDS(on)函數(shù)。趨勢線的斜率反映不同的FOM。請注意:由于數(shù)據(jù)來自于資料手冊,因此數(shù)值包含封裝電阻。由圖3可知,相較于超級接面和分裂閘溝槽技術(shù),橫向技術(shù)的QG更佳。由于超級接面結(jié)構(gòu)在元件閘極和連接源極的漏極遮罩電極間增加了CGS,因此QG值低于分裂閘技術(shù)。

圖3 針對橫向/分裂閘/超級接面30V功率MOSEFT結(jié)構(gòu)的QG、QOSS和QG與QOSS加權(quán)組合(CWS FOM)的比較。

相較于采用表面漏極觸點(diǎn)的橫向元件而言,橫向結(jié)構(gòu)的基板與漏極連接,并在元件主體和基板間增加CDS元件,可產(chǎn)生較高的QOSS結(jié)構(gòu)。分裂閘結(jié)構(gòu)的QOSS值亦較高,因?yàn)槠湟蕾嚶┰礃O電容的產(chǎn)生以遮罩閘極電極,達(dá)到低QGD和RDS(on)。而超級接面結(jié)構(gòu)毋須增加額外的CDS元件,因此可達(dá)成三種結(jié)構(gòu)中最低的QOSS值。

選擇功率MOSFET結(jié)構(gòu)的重要因素,在于考量該結(jié)構(gòu)是否有助于提高元件性能。若選用橫向或分裂閘結(jié)構(gòu),須考慮在低側(cè)元件應(yīng)用中,是否值得為獲得低QGD和QG而犧牲QOSS性能。這些達(dá)成最佳化的結(jié)果如圖3下半部分所示,QOSS和QG使用5伏特閘極驅(qū)動電壓和12伏特轉(zhuǎn)換電壓進(jìn)行組合。顯然對于同步FET而言,超級接面結(jié)構(gòu)因其固有的低QOSS而具備最佳的綜合性能。此結(jié)果表明,僅藉由達(dá)成最佳化已不足以獲得最低QG和QGD FOM。這種情況更足以證明,溝槽結(jié)構(gòu)中閘極電荷已降至相當(dāng)?shù)停琎G不再扮演低側(cè)元件開關(guān)損耗的主要因素。

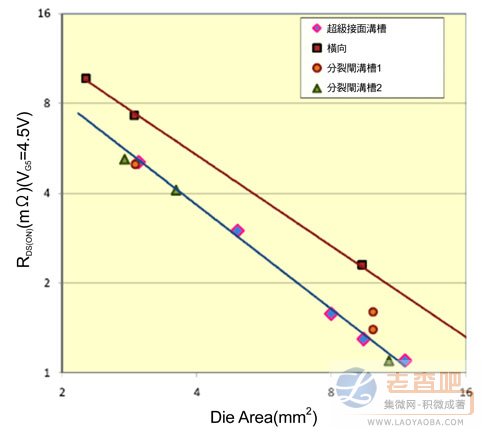

對于同步FET方面,也必須要針對Sp.RDS(on)進(jìn)行權(quán)衡和取舍,因?yàn)榧幢阍诟唛_關(guān)頻率下,導(dǎo)通狀態(tài)下的損耗仍占大部分比例。圖4顯示不同技術(shù)下RDS(on)與晶片面積的關(guān)系。顯而易見,橫向結(jié)構(gòu)需要更大的晶片才得以獲得與溝槽結(jié)構(gòu)相同的RDS(on)。若觀察競爭對手產(chǎn)品的最低典型RDS(on)值(VGS=4.5伏特時),將會發(fā)現(xiàn),橫向技術(shù)可達(dá)成的最佳結(jié)果為1.4毫歐姆(mΩ)(CSD17312Q5)、分裂閘結(jié)構(gòu)可達(dá)成1.1毫歐姆(FDMS7650),而超級接面結(jié)構(gòu)可達(dá)成1.1毫歐姆(PSMN1R0-30YLC)。就Sp.RDS(on)而言,競爭產(chǎn)品的基準(zhǔn)顯示,當(dāng)VGS=4.5伏特時,橫向技術(shù)單位面積的RDS(on)值較超級接面技術(shù)和分裂閘技術(shù)的RDS(on)值高出60%。如圖3所示,由于晶片的尺寸不一,上述差異并未充分反映出實(shí)際上最低的RDS(on)值。請注意,CSD17312Q5的額定閘極電壓為10伏特,而溝槽技術(shù)為20伏特。如果采用相同的額定閘極電壓元件進(jìn)行RDS(on)比較,則其差異將更明顯。

圖4 針對不同的功率MOSFET結(jié)構(gòu),晶片面積與RDS(on)的關(guān)系。

封裝面積縮小帶來更多挑戰(zhàn)

封裝面積縮小帶來另一個根本性的問題,即是否有必要犧牲Sp.RDS(on)以改善開關(guān)性能和FOM。例如,在3.3毫米(mm)×3.3毫米的QFN封裝中,晶片尺寸限制在4.5平方毫米(mm2)以內(nèi)。由于考量此封裝限制,才設(shè)計(jì)出面積限制的同步FET FOM。為闡明Sp.RDS(on)對同步FET功耗(PL)的影響,必須考量受晶片面積公式3影響的功耗元件,其中I0為輸出電流,tf為高溫條件下導(dǎo)致MOSFET阻抗上升的溫度因數(shù),dt為MOSFET的導(dǎo)通時間,fSW為開關(guān)頻率,VDR為閘極驅(qū)動電壓,QG0為VDS=0V時VDR的閘極電荷,VIN為轉(zhuǎn)換電壓。在此并未提及Qrr,因?yàn)楦怕远裕琎rr與晶片大小無關(guān)。

PL=IO2RDS(on)×tf×dt+fSW (VDR×QG0+1/2VIN×QOSS)¨¨¨¨¨(公式3)

假設(shè)tf=1.3(即在100℃環(huán)境下運(yùn)作)、導(dǎo)通時間為77%(相當(dāng)于從12伏特轉(zhuǎn)換至1.2伏特時,全負(fù)載效率的85%),上述公式可針對RDS(on)、QG0、單位面積Qoss數(shù)值以及活動區(qū)域AA改寫為公式4。此外,為達(dá)成最低功耗,我們對活動區(qū)域進(jìn)行區(qū)分,如公式4、5、6。

PL=IO2/AA×Sp.RDS(on)+AA×fSW (CWS FOM)/Sp.RDS(on)¨¨¨¨¨¨¨(公式4)

0=–IO2/AA2×Sp.RDS(on)+fSW (CWS FOM)/Sp.RDS(on)¨¨¨¨¨¨¨(公式5)

Sp.RDS(on)×IO=AA×(fSW(CWS FOM))1/2¨(公式6)

(Sp.RDS(on)×IO)/(AA×(fSW×CWS FOM)1/2)=1¨(公式7)

對于同步FET而言,只有在特定封裝的晶片尺寸具備足夠的活動區(qū)域,能夠確保ACS FOM=1時,才能將功耗降至最低。圖5顯示當(dāng)電流為25安培(A)、開關(guān)頻率為500kHz時,根據(jù)公式4得出的功耗與活動區(qū)域的關(guān)系。

圖5 不同的功率MOSFET結(jié)構(gòu)作為同步FET時,活動區(qū)域與功耗之間的關(guān)系。開關(guān)頻率為1MHz時,輸出電流為25安培。電壓由12伏特轉(zhuǎn)換為1.2伏特,閘極驅(qū)動電壓為5伏特。

表2列出針對Power SO8和QFN3333封裝的ACS FOM。對于Power SO8來說,分裂閘技術(shù)的ACS FOM最低,代表其最佳性能最易于達(dá)成。但由于CWS FOM值為最大(圖3),因此,并非最佳的技術(shù)選擇。值得注意的是,雖然分裂閘結(jié)構(gòu)的開關(guān)FOM不如橫向技術(shù),但由于橫向技術(shù)的Sp.RDS(on)較差,因此無法充分利用其開關(guān)FOM方面的優(yōu)勢。相反,在這三項(xiàng)技術(shù)中,超級接面結(jié)構(gòu)同時擁有最低的Sp.Rds(on)和CWS FOM,因而能夠在所需晶片面積內(nèi)發(fā)揮最佳性能。當(dāng)采用更小的QFN3333封裝時,這些技術(shù)均無法發(fā)揮其最佳性能(三者的ACS FOM>1)。然而,圖4所示的結(jié)構(gòu)中,明確標(biāo)示出須要進(jìn)一步降低Sp.RDS(on),盡管這樣做可能導(dǎo)致開關(guān)FOM變差,詳見分裂閘技術(shù)和橫向技術(shù)針對面積小于4平方毫米應(yīng)用的對比。

超級接面功率MOSFET損耗低

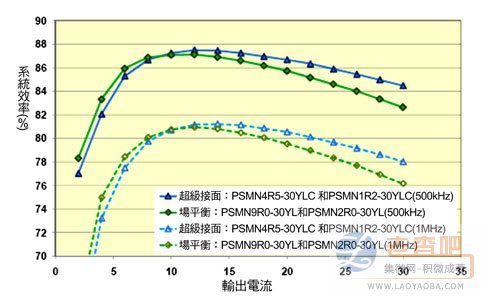

為展現(xiàn)超級接面功率MOSFET結(jié)構(gòu)的優(yōu)點(diǎn),可對系統(tǒng)效率進(jìn)行測量,并將測量結(jié)果與超級接面元件和晶片尺寸相似的場平衡結(jié)構(gòu)元件做比較,工作頻率為500kHz和1MHz、電壓從12伏特轉(zhuǎn)換為1.2伏特(圖6)。當(dāng)二者的晶片尺寸相同時,前者的導(dǎo)通狀態(tài)損耗優(yōu)于后者。當(dāng)工作頻率為500kHz和1MHz時,在30安培全負(fù)載和低負(fù)載條件下,系統(tǒng)效率均提高2%。超級接面晶片尺寸無論大小,均有可能出現(xiàn)下列情形,如重負(fù)載條件下的效率提升會犧牲輕負(fù)載效率,而輕負(fù)載條件的系統(tǒng)效率提升會犧牲重負(fù)載效率。采用RDS(on)較高的控制FET可能會改善效率,因?yàn)镼GD降低所帶來的益處大于RDS(on)升高所帶來的壞處。

圖6 超級接面技術(shù)與場平衡(FB)技術(shù)的效率測量結(jié)果對比,電壓為12V轉(zhuǎn)換至1.2V。

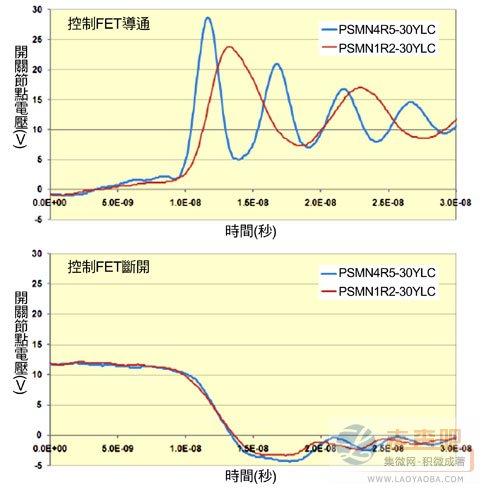

從上述中可知,控制FET的開關(guān)速度可能會受到QGD以外的其他因素限制。可從圖7明顯看出,低RDS(on)同步FET(PSMN1R2-30YLC)與中等RDS(on)同步FET(PSMN4R5-30YLC)的開關(guān)波形的比較。在這兩個例子中,PSMN4R5-30YLC均作為控制FET。可明顯地看出,開關(guān)節(jié)點(diǎn)(即控制FET和同步FET形成的半橋中點(diǎn))的上升時間與控制FET無關(guān)。換言之,開關(guān)節(jié)點(diǎn)電壓上升所導(dǎo)致的導(dǎo)通損耗不再受控制FET的QGD限制。

圖7 PSMN4R5-30YLC和PSMN1R2-30YLC在導(dǎo)通和斷開時的開關(guān)節(jié)點(diǎn)波形(即同步FET的VDS)

本例中的限制因素為電路通過寄生電感為同步FET的輸出電容充電所需要的時間。結(jié)果顯示使用者必須更加重視降低QOSS,而非CWS FOM隱含的值。斷開操作是控制FET功耗最集中的時候,此時低RDS(on)和中等RDS(on) MOSFET的開關(guān)節(jié)點(diǎn)電壓壓降幾乎是沒有差別,這表示開關(guān)時間仍然受高側(cè)元件的QGD影響。由于閘極電流比較低,且MOSFET閘極電阻具有內(nèi)部分配性,控制FET的斷開速度通常較慢于導(dǎo)通速度。因此控制FET極可能是決定元件斷開時開關(guān)速度的影響因素。

在評估DC-DC轉(zhuǎn)換的功率MOSFET性能時,不能僅考慮QG和QGD兩個數(shù)值,因?yàn)榻陙磉@些數(shù)值的降低,以致于必須考慮其他功耗機(jī)制。針對達(dá)成同步FET的性能最佳化,開發(fā)出兩種新的FOM,分別是CWS FOM,綜合了輸出電荷效應(yīng)(QOSS),以及考量晶片尺寸限制的ACS FOM。

新的FOM被用于分析三種不同的功率MOSFET結(jié)構(gòu)。結(jié)果顯示最近開發(fā)的低壓超級接面結(jié)構(gòu)可完美結(jié)合低RDS(on)、低QG和低QGD等特性,其性能優(yōu)于橫向和分裂閘等競爭產(chǎn)品結(jié)構(gòu)。此外,隨著封裝尺寸縮小,ACS FOM亦顯示出在功率MOSFET設(shè)計(jì)中,犧牲Sp.RDS(on)以改善開關(guān)頻率并非為最佳策略。