一、引言

當(dāng)今許多電信公司正密切關(guān)注著他們所致力的3G產(chǎn)品的研制和開(kāi)發(fā),例如移動(dòng)終端、基站以及其它大量的網(wǎng)絡(luò)設(shè)備。無(wú)可置疑地,3G產(chǎn)品和業(yè)務(wù)已經(jīng)成為無(wú)線(xiàn)通信市場(chǎng)的主流,而其中CDMA,尤其是寬帶CDMA(W-CDMA)憑借著其高性能、在系統(tǒng)容量運(yùn)用中的高效性以及物理資源使用中的便捷性,日益成為3G技術(shù)中的主導(dǎo)。

為了滿(mǎn)足3G的高技術(shù)復(fù)雜度以及高信號(hào)處理要求,基于FPGA/ASIC的專(zhuān)用硬件必須要符合不同用戶(hù)產(chǎn)品的規(guī)格。也就是說(shuō),在3G無(wú)線(xiàn)終端發(fā)展中,產(chǎn)品的尺寸、重量以及功率消耗這些參數(shù)將是十分關(guān)鍵和重要的決定因素。由此,系統(tǒng)芯片(SoC)作為一門(mén)新的設(shè)計(jì)方略被引入了3G的發(fā)展。SoC要求能夠?qū)^(qū)域有效信號(hào)處理算法與結(jié)構(gòu)的設(shè)計(jì)、發(fā)展都集成在一塊小的芯片上。

數(shù)字濾波器作為信號(hào)處理中最為常見(jiàn)的元件,被廣泛地應(yīng)用于無(wú)線(xiàn)通信的各個(gè)部分中。本文針對(duì)3G標(biāo)準(zhǔn)CDMA 2000中的脈沖成形FIR濾波器的ASIC實(shí)現(xiàn)進(jìn)行討論,并在此提出一種實(shí)效的實(shí)現(xiàn)結(jié)構(gòu):基于分布式運(yùn)算(DA)結(jié)構(gòu)的查表法。

二、脈沖成形濾波器

脈沖成形濾波器常用于旨在提高信號(hào)頻譜傳輸效率的基帶通信傳輸中。經(jīng)過(guò)D/A轉(zhuǎn)換后的成形濾波器通常是被設(shè)計(jì)為FIR濾波器,其作用是[1]:將信號(hào)的同相(I)和正交(Q)符號(hào)轉(zhuǎn)換為模擬的I、Q信號(hào)。

一般來(lái)說(shuō),F(xiàn)IR濾波器是需要有一個(gè)升余弦或者是平方根升余弦成形脈沖響應(yīng)的。這里需要注意的是,成形濾波器的采樣速率一般要求比輸入的I、Q符號(hào)速率要高(通常是其4~8倍)。因此,在此要有一個(gè)先于脈沖成形的過(guò)采樣。圖1描述了典型的成形過(guò)程,其中過(guò)采樣通過(guò)在連續(xù)的輸入采樣值中插入M-1個(gè)零值來(lái)實(shí)現(xiàn)的。CDMA2000標(biāo)準(zhǔn)中,對(duì)1個(gè)擴(kuò)頻速率的系統(tǒng)(碼片速率=1.2288 MCPS),用48階對(duì)稱(chēng)系數(shù)FIR濾波器;對(duì)3個(gè)擴(kuò)頻速率的系統(tǒng)(碼片速率=3×1.2288 MCPS),用108階的濾波器。由于濾波器運(yùn)行在4倍碼片速率下,因此輸入的I、Q符號(hào)應(yīng)該是過(guò)采樣的4倍,即圖1中M=4。

假設(shè)FIR濾波器傳遞函數(shù)為H(z),根據(jù)十進(jìn)制/插補(bǔ)理論[2],通過(guò)如圖2所示對(duì)H(z)的多相分解(在圖中設(shè)M=4),能更有效地完成過(guò)采樣及濾波器功能。在圖2中,Hk(z)表示子濾波器的傳遞函數(shù),其脈沖響應(yīng)hk(n)=h(4n+k), n=0,1,…11是由對(duì)h(n)抽值得出的。多相結(jié)構(gòu)的優(yōu)點(diǎn)在于:?jiǎn)蝹€(gè)子濾波器是工作在較低的抽樣速率上的,而將4個(gè)子濾波器相結(jié)合后,其系數(shù)總值與原來(lái)濾波器的H(z)系數(shù)相當(dāng)。也就是說(shuō),采用這個(gè)方法,整體的計(jì)算總量能減少3/4。同時(shí)從圖2可以看出,這種方法需要用到4個(gè)濾波器,因此就硬件的有效性來(lái)說(shuō),這并不是最理想的。

下面將介紹一種結(jié)構(gòu),對(duì)于ASIC來(lái)說(shuō)它更加得實(shí)際、實(shí)效,同時(shí)也保留了多相分解的優(yōu)點(diǎn)。

三、分布式運(yùn)算體系

在分布式運(yùn)算(DA)運(yùn)算法則中,濾波器的輸出可以表示為

![]()

其中ak是固定的濾波器系數(shù);

xk是輸入數(shù)據(jù)字。

如果將xk表示成B比特的二進(jìn)制補(bǔ)碼,|xk|<1,則有

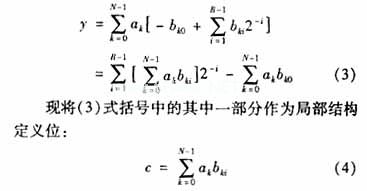

![]()

其中bki取值為0或是1,bk0是符號(hào)位,bk0為1表示數(shù)據(jù)為負(fù),bk0為0表示數(shù)據(jù)為正;bk,B-1是最低有效位(LSB)。將(2)式和(1)式合并后,我們可以得到y(tǒng)具體的比特位表達(dá)式[3]:

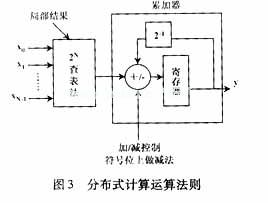

由于bki取值只有0或1, 則(4)式的值有2N種可能性。因此,可以預(yù)先算出這2N個(gè)局部結(jié)果并存放在一個(gè)固定的表中(表的寬度為對(duì)系數(shù)ak定義的寬度,深度為2N),N是能夠?qū)?shù)據(jù)源抽樣數(shù)據(jù)進(jìn)行處理的數(shù)據(jù)長(zhǎng)度[3]。然后按照輸入的數(shù)據(jù),直接對(duì)該表尋址并將結(jié)果導(dǎo)入累加器中。在B-1次查表之后,累加器的寄存器存儲(chǔ)有(3)式第一項(xiàng)所示的結(jié)果。最后一個(gè)查表給出局部結(jié)果 ,也就是(3)式中的第二項(xiàng),用于表示符號(hào)位,并且在寄存器的右移位操作中不包括該項(xiàng),即將它從寄存器的右移過(guò)程中減去。因此,在整個(gè)程序中只有在符號(hào)位時(shí)鐘上會(huì)使用減法控制。

,也就是(3)式中的第二項(xiàng),用于表示符號(hào)位,并且在寄存器的右移位操作中不包括該項(xiàng),即將它從寄存器的右移過(guò)程中減去。因此,在整個(gè)程序中只有在符號(hào)位時(shí)鐘上會(huì)使用減法控制。

DA運(yùn)算法則如圖3所示。所需的基礎(chǔ)操作有:查表排序、加法、減法以及輸入數(shù)據(jù)序列的移位。運(yùn)用DA結(jié)構(gòu)的前提是:輸入抽樣值必須要表示為2個(gè)補(bǔ)碼并將其轉(zhuǎn)換成一個(gè)比特串行形式。總共需要有N個(gè)B比特的移位寄存器,每個(gè)寄存器在一個(gè)時(shí)鐘周期下產(chǎn)生1比特來(lái)生成一個(gè)用于查找表(LUT)地址(N比特寬)。LUT存儲(chǔ)了所有濾波器系數(shù)狀態(tài)可能的局部結(jié)果,這些局部結(jié)果在寄存器中進(jìn)行加權(quán)(每個(gè)周期除以2)和累加,直到每個(gè)移位寄存器的最后一位為止。

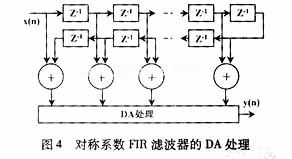

由于脈沖成形濾波器有著對(duì)稱(chēng)的沖擊響應(yīng),因此先把使用同一個(gè)脈沖響應(yīng)系數(shù)的2個(gè)輸入取樣值進(jìn)行相加,然后相繼地把N/2個(gè)加法器的輸出結(jié)果送入DA進(jìn)行處理,如圖4[4]所示。所以,LUT的個(gè)數(shù)也就從2N個(gè)減少到了2N/2個(gè)。

圖5所示為通用的FIR成形濾波器結(jié)構(gòu)框圖。比較圖4與圖5后可以看出,運(yùn)用DA結(jié)構(gòu)可以在程序的編寫(xiě)過(guò)程中大量減少乘法運(yùn)算,而乘法運(yùn)算在硬件程序中往往是占用資源最大的部分之一。運(yùn)用DA處理結(jié)構(gòu)能大大減少硬件資源,并在很大程度上提高程序運(yùn)算速度。

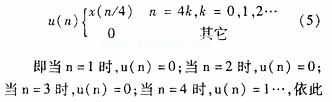

為了進(jìn)一步減小LUT的個(gè)數(shù),現(xiàn)在在過(guò)采樣中引入零抽樣值。設(shè)u(n)為過(guò)采樣程序塊的輸出序列:

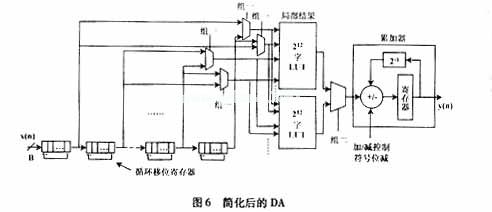

類(lèi)推,應(yīng)用u(n)后,48個(gè)抽頭中的36個(gè)采樣值將給定為零,這樣就有一半的加法器輸入為零采樣值,并在每個(gè)時(shí)鐘將零采樣值傳遞到對(duì)應(yīng)的乘法器。而另一半加法器的輸入值中也只有一個(gè)是非零采樣值。這樣一來(lái),在第一級(jí)就能減少24個(gè)加法器和一半的乘法器,也就意味著運(yùn)算出一個(gè)輸出采樣值只需調(diào)用一半的濾波器系數(shù)。對(duì)一個(gè)碼片速率輸入采樣值x(n)來(lái)說(shuō),經(jīng)過(guò)運(yùn)算得出4個(gè)輸出采樣:y(n)、y(n+1)、y(n+2)以及y(n+3),其中y(n)和y(n+3)需要調(diào)用的系數(shù)(組一)如下:h(0)、h(3)、h(4)、h(7)、h(8)、h(11)、h(12)、h(15)、h(16)、h(19)、h(20)、h(23);而y(n+1)和y(n+2)需要調(diào)用的系數(shù)(組二):h(1)、h(2)、h(5)、h(6)、h(9)、h(10)、h(13)、h(14)、h(17)、h(21)、h(22)。這樣就可以完成如圖6所示的實(shí)效DA。輸入序列即為碼片速率采樣值,并且輸出的數(shù)據(jù)是碼片速率的4倍,每輸入一個(gè)采樣值可以得出4個(gè)輸出采樣值,內(nèi)部時(shí)鐘速率為4×B×碼片速率。DA運(yùn)行中,常用電路移位寄存器(CSR)來(lái)代替一個(gè)移位寄存器保存數(shù)據(jù),直到每個(gè)芯片間隔運(yùn)算出最后的輸出采樣值為止。一旦輸入一個(gè)新的采樣值,這些CSR就要更新一次。在芯片的持續(xù)時(shí)間中一共有4個(gè)循環(huán),每個(gè)循環(huán)經(jīng)歷B個(gè)時(shí)鐘并產(chǎn)生一個(gè)輸出采樣值。一個(gè)循環(huán)過(guò)后,CSR移位回歸到初始數(shù)據(jù),為下一個(gè)循環(huán)處理做準(zhǔn)備,以生成另一個(gè)輸出采樣值。圖6中的2個(gè)LUT分別存儲(chǔ)了兩組濾波器系數(shù)各自生成的局部結(jié)果。選擇器是用來(lái)決定在每個(gè)循環(huán)中選擇這兩組輸入分支的哪一組的,其中當(dāng)高位LUT的結(jié)果在循環(huán)1和2輸出,低位LUT結(jié)果在循環(huán)3和4輸出的時(shí)候選擇組一;當(dāng)高位LUT的結(jié)果在循環(huán)1和4輸出,低位LUT的結(jié)果在循環(huán)2和3輸出的時(shí)候選擇組二。累加器的寄存器在每個(gè)循環(huán)的起始都要進(jìn)行清零。

四、設(shè)計(jì)

現(xiàn)設(shè)計(jì)一個(gè)1比特輸入、14比特輸出的平方根升余弦滾降線(xiàn)性相位FIR數(shù)字濾波器,滾降系數(shù)為0.22,帶外衰減要求大于45 dB,即通帶內(nèi)(f<8.192MHz)的起伏小于0.5dB,阻帶外(f>10 MHz)的衰減大于45dB。在設(shè)計(jì)中選用了Alter公司的FPGA芯片-EP1K50QC208-3,該芯片有2 880個(gè)邏輯單元(LE),40960個(gè)片內(nèi)存儲(chǔ)器。本設(shè)計(jì)占用了387個(gè)LE和1088個(gè)片內(nèi)存儲(chǔ)器,分別占總資源的1.3%和2%。

經(jīng)過(guò)試驗(yàn),本結(jié)果已經(jīng)在FPGA中得到了實(shí)現(xiàn)。

五、結(jié) 論

從試驗(yàn)結(jié)果中可以看出,DA實(shí)現(xiàn)控制起來(lái)比較簡(jiǎn)單并且時(shí)鐘速率較低,但是因?yàn)長(zhǎng)UT的大小會(huì)隨著濾波器階數(shù)的增加呈指數(shù)增長(zhǎng),因此其門(mén)的數(shù)量也較多。在階數(shù)很大的濾波器中采用并行的FIR結(jié)構(gòu),每個(gè)并行的子濾波器以DA結(jié)構(gòu)實(shí)現(xiàn),這樣,控制起來(lái)就稍微有點(diǎn)復(fù)雜了。因此,如何去克服這方面的缺點(diǎn)還有待于繼續(xù)研究。