開關(guān)電源的效率與功耗已成為設(shè)計師關(guān)注的焦點,而多模式控制已經(jīng)成為電源控制芯片中高效率低功耗設(shè)計的主流趨勢。

所謂多模式控制就是在開關(guān)電源的工作中根據(jù)負載情況的不同采用不同的控制策略,以降低其功耗,提高效率。它是針對常用開關(guān)電源在輕載和待機條件下效率低的特點提出的,其設(shè)計思想可描述為:在重載下采用PWM 模式,以發(fā)揮其重載下效率高的優(yōu)點;在輕載下采取PFM 模式,通過降低開關(guān)頻率來降低功耗;而在極輕載條件下(待機模式下)則采取BURST模式來降低功耗。

目前,由于能源緊缺,國際國內(nèi)均對降低用電設(shè)備的輕載和待機功耗給予了極大注意。應(yīng)指出的是,傳統(tǒng)的多模式控制策略雖然改善了開關(guān)電源的輕載與待機效率,但未對控制芯片本身的靜態(tài)功耗予以足夠的重視,考慮到家電、辦公設(shè)備等設(shè)備數(shù)量巨大,倘能將控制芯片的靜態(tài)電流由毫安級降低一至兩個數(shù)量級,其節(jié)電效能就十分可觀。

文中給出一種低功耗開關(guān)電源控制芯片供電系統(tǒng)的設(shè)計并予以實現(xiàn),其特點是可以降低控制芯片在輕載與待機模式下的功耗。

針對當(dāng)前應(yīng)用廣泛的系統(tǒng)芯片的需要,分別設(shè)置了一個數(shù)字模塊供電單元和兩個模擬模塊供電單元,其中一個模擬模塊供電單元專門用于在重載條件下為控制模塊供電,而在輕載和待機模式下則被關(guān)斷,以降低芯片的靜態(tài)功耗。

1 系統(tǒng)與電路設(shè)計

1.1 系統(tǒng)構(gòu)成

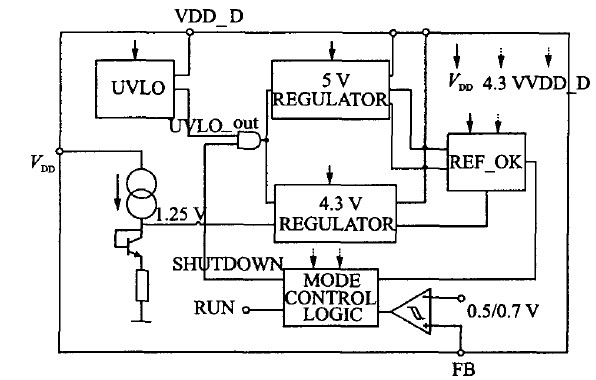

整個系統(tǒng)的構(gòu)成如圖1所示。系統(tǒng)中包括一個欠壓鎖定電路(UVLO,Under voltage lockout),用于保證電路在合適的電壓范圍內(nèi)正常工作;一個帶隙基準(zhǔn)電壓源和一個專為數(shù)字模塊供電的電壓源(記為VDD_D),分別為芯片提供基準(zhǔn)偏置和數(shù)字部分的電源。具體構(gòu)成時此兩模塊包含在UVLO模塊內(nèi)。兩個電壓調(diào)整器(REGULATOR)分別產(chǎn)生一個5 V和一個4.3 V 的穩(wěn)定電壓,其中5 V穩(wěn)定電壓源輸出記為REG,用于在重載時為控制器供電(輕載時關(guān)斷);4.3 V 穩(wěn)定電壓源輸出記為VDD_AD,用于輕載時的供電。當(dāng)然,必要時還可以利用帶隙基準(zhǔn)產(chǎn)生更多不同的電壓以滿足復(fù)雜控制模式的需要。

圖1電源系統(tǒng)框圖

此外,本設(shè)計中還設(shè)置了一個REF-OK模塊來判斷上電后電源系統(tǒng)是否已進入正常工作狀態(tài)。

1.2 欠壓鎖定電路的設(shè)計

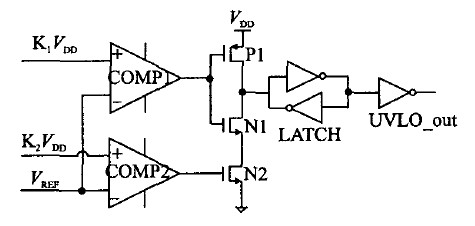

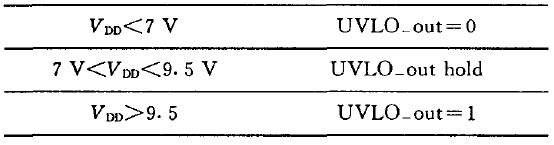

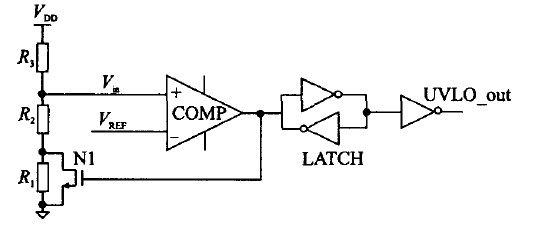

欠壓鎖定電路又稱UVLO,見圖2.圖中 VDD為芯片外部供電電源,設(shè)計值為12 V.欠壓鎖定電路的窗口設(shè)置為7~9.5 V,即上電后電壓上升到大于9.5V 時芯片開始正常工作,而當(dāng)供電電壓小于7 V時芯片停止工作。考慮到欠壓鎖定電路在電源控制芯片中的重要性,設(shè)計給出了兩種實現(xiàn)方案,并對兩種控制策略的性能進行了分析與比較。

圖2 兩個比較器實現(xiàn)的欠壓鎖定電路

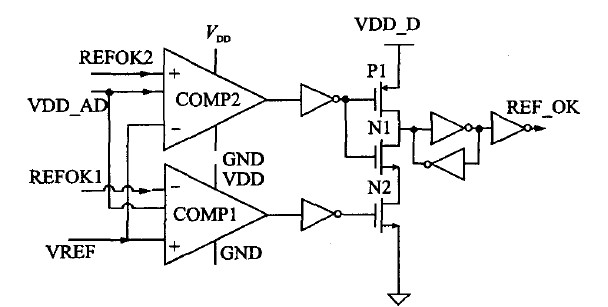

圖2給出第一種欠壓鎖定電路的原理圖,稱為U-VLO1,這是用兩個比較器實現(xiàn)的欠壓鎖定電路。VDD是外部供電電壓源,K1、K2 是小于1的常數(shù),且K1》K2,VREF為1.25 V帶隙基準(zhǔn)電壓,LATCH是由兩個反相器組成的鎖存器。圖中標(biāo)的UVLO_out代表欠壓鎖定信號,狀態(tài)設(shè)置是UVLO_out=0時有效。

電路的工作原理可簡述如下:12 V供電電壓可在VDD比較低時建立一個PTAT (ProportiONal toabsolute temperature)電流源,然后利用其建立起帶隙基準(zhǔn)電壓源;當(dāng)VDD由0上升時,帶隙基準(zhǔn)電壓r首先建立,此時兩個比較器的輸出為低電位,P1導(dǎo)通,輸出為高電位;當(dāng)K1VDD大于 r時,COMP1輸出跳變,N1管導(dǎo)通,鎖存器鎖存上一個信號,UVLO為高電位(注意其為低電位有效);當(dāng)K2VDD大于VREF 時,N2導(dǎo)通,則UVLO-out為低電位,使能其他模塊;隨著VDD減小,K2VDD首先小于VREF,N2關(guān)斷,則鎖存器鎖存信號,UVLO-out保持;當(dāng) VDD減小到K1 VDD小于VREF時COMP1跳變,P1導(dǎo)通,N1關(guān)斷,則輸出UVLO-out為高電位,關(guān)斷整個控制芯片。

表1 UVLO 的狀態(tài)對應(yīng)表

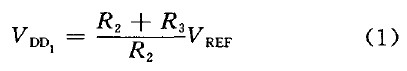

另一個方案是利用一個比較器實現(xiàn)的UVLO電路,稱UVLO2.該電路的特點是通過外部遲滯實現(xiàn)了欠壓鎖定功能,可應(yīng)用于高壓和低壓場合,如圖3.電路的工作原理如下:當(dāng)VDD由0上升到一個比較小的值時,帶隙基準(zhǔn)電壓VREF首先建立,當(dāng)VDD上升到:

時,比較器開始跳變,N1關(guān)斷,UVLO-out為0,使能整個控制芯片。當(dāng)外部電源電壓開始減小到:

時,比較器跳轉(zhuǎn),N1開通,UVLO-out開始變l.通過合理設(shè)置R1、R2、R3值就可以使VDD1=9.5 V,VDD2=7V,即VDD上升到9.5 V時UVLO輸出為零,芯片正常工作; VDD下降到7 V 時芯片停止工作。

圖3 用外部遲滯實現(xiàn)的欠壓鎖定電路

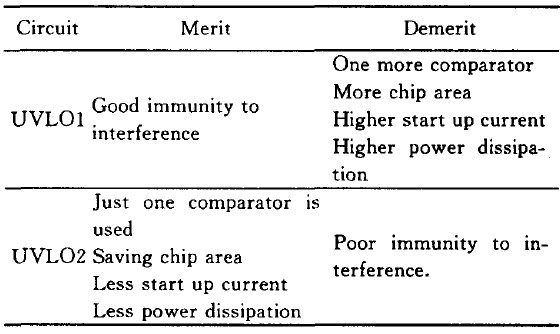

兩種方案的工作特性對比結(jié)果如表2所列。需要指出的是,若直接用門電路實現(xiàn)施密特觸發(fā),由于“的工藝離散性,將使觸發(fā)電壓難以準(zhǔn)確控制。

表2 兩種欠壓鎖定電路比較

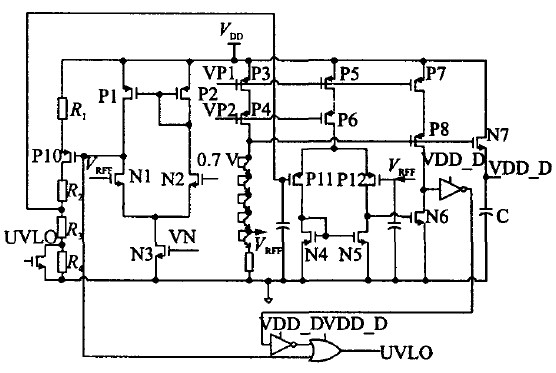

經(jīng)比較可知,UVL02結(jié)構(gòu)較為簡單,面積小,啟動電流小,有利于降低功耗。因此,本設(shè)計最終采用了UVL02方案。此外,為最大限度減小功耗,設(shè)計中將帶隙基準(zhǔn)電壓、數(shù)字電源和欠壓鎖定電路集成在一起。具體電路圖見圖4。

圖4 欠壓鎖定和數(shù)字電源的具體電路圖

圖中利用帶隙基準(zhǔn)電壓加上四個二極管連接的三極管產(chǎn)生一個大于4 V 的電壓,然后經(jīng)過M0S管產(chǎn)生一個大約2.65 V左右的電壓。這個電壓在基準(zhǔn)電壓建立后就產(chǎn)生了,主要用于為欠壓鎖定電路的數(shù)字部分供電,并且擔(dān)任了為整個系統(tǒng)的數(shù)字電路供電的任務(wù)。

1.3 5 V基準(zhǔn)電壓源(REG)

圖5為5 V穩(wěn)定電壓源(REG)的電路原理。其中P1、P2、P3、P4組成共源共柵結(jié)構(gòu),可以提高電流鏡的鏡像精度,同時提高電源抑制比。Q3、Q4、R 1、R2組成一個帶隙基準(zhǔn)電壓,這樣可以減小額外的電流支路,降低功耗。Q1、Q2組成達林頓結(jié)構(gòu),增加輸出能力。P5、P6增加匹配,減小溝道長度調(diào)制效應(yīng)。Q1、Q2、R3、R4、R5、R6、Q4、P5、P6組成一個負反饋環(huán)路,將REG電壓穩(wěn)定在5 V。圖中C具有兩種作用:1、記憶直流工作點;2、補償環(huán)路電容。

穩(wěn)壓機理如下:當(dāng)負載增加時,REG電壓下降,則Q4基極下降,集電極升高,經(jīng)過P5、P6,使得Q1、Q2基極升高,REG 電壓升高;反之亦然。

REG電壓是片上多數(shù)模塊的供電電壓,驅(qū)動能力設(shè)計為4mA。

圖5 5 V 穩(wěn)定電壓源

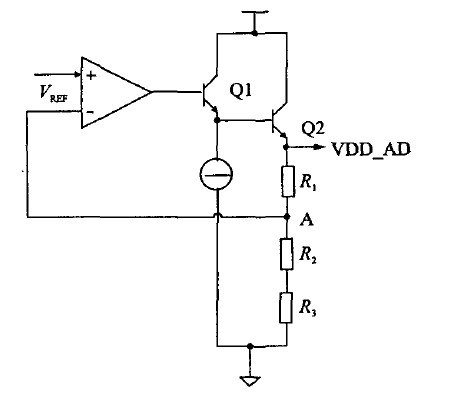

1.4 4.3 V穩(wěn)定電壓源

4.3 V 的穩(wěn)定電壓源(VDD-AD)用來在輕載時為系統(tǒng)供電,始終保持工作,在BURST模式下由它為模擬模塊供電。

圖6 4.3 V 的穩(wěn)定電壓源

是帶隙基準(zhǔn)電壓,通過一個運放、一個達林頓結(jié)構(gòu)的晶體管和一個電阻分壓網(wǎng)絡(luò)組成負反饋環(huán)路來產(chǎn)生4.3 V 的穩(wěn)定電壓。其穩(wěn)壓機理如下:當(dāng)負載增大時,VDD-AD電壓下降,此時A點電壓下降,使運放的輸出上升,則Q1、Q2基極升高,REG電壓重新升高,獲得穩(wěn)定;反之亦然。

VDD-AD是檢測模塊的供電電壓,設(shè)計驅(qū)動能力為2 mA.芯片負載減小時,關(guān)斷REG,減小了芯片的靜態(tài)功耗,這樣既能保證芯片的驅(qū)動能力,又同時降低了芯片的靜態(tài)功耗。

圖7 REF-OK 電路的設(shè)計

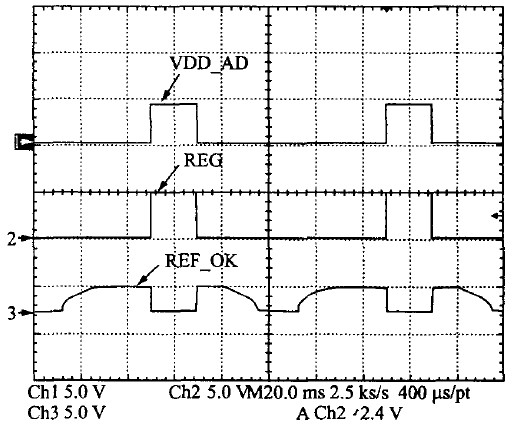

1.5 REF_OK模塊

REF_0K模塊用以標(biāo)志電源系統(tǒng)是否建立好,以控制決定供電單元是否正常開始工作。其中兩個比較參考電平REFOK1、REF0K2的關(guān)系始終保持為REFOK1《REF0K2.電路的工作原理如表3,形成的滯回窗口不僅保證了REG的精度,而且提高了整個供電單元的抗干擾性能。

表3 REF_OK 的基本功能表

1.6 模式控制邏輯

模式控制邏輯用以保證在進行模式選擇時,電源系統(tǒng)正常工作。當(dāng)FB電壓底于0.5 V時,該控制邏輯通過內(nèi)部電流滯回比較器自動選擇進入待機模式。RUN信號(其為高電位有效)用來關(guān)斷綠色多模式反激變換器中的其它控制模塊,以實現(xiàn)低待機功耗。

圖8 模式控制邏輯

2.版圖設(shè)計及測試結(jié)果

2.1 版圖設(shè)計

圖9給出了制得的多模式開關(guān)電源控制芯片的顯微照片,其中用線框標(biāo)出的部分就是所設(shè)計的供電模塊,包括:欠壓鎖定電路,數(shù)字電源,模擬電壓源(5 V穩(wěn)定電壓源,4.3 V穩(wěn)定電壓源),REF_OK等子模塊。兩個模擬電壓源因功率較大,可視為熱源,將其統(tǒng)一放置在版圖的左邊,而PTAT、帶隙基準(zhǔn)等敏感模塊則盡量遠離熱源,放置在版圖的右邊,欠壓鎖定電路也放置在版圖的右上角。

圖9 芯片的顯微照片

2.2 Regulator的測試

5 V 電壓的PSR測試波形如圖10所示。由此圖可見,其PSR可以達到-60 dB.該供電模塊在工作頻率為40~130 kHz的綠色多模式反激式控制器中的應(yīng)用表明,它對來自電源的干擾具有較好的抑制能力。

圖10 5 V電源的PSR

2.3 供電系統(tǒng)的測試

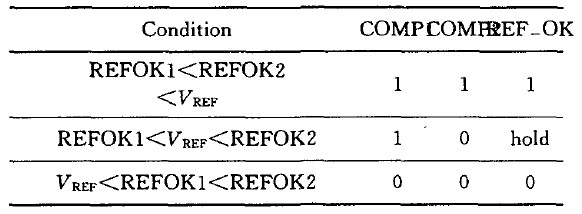

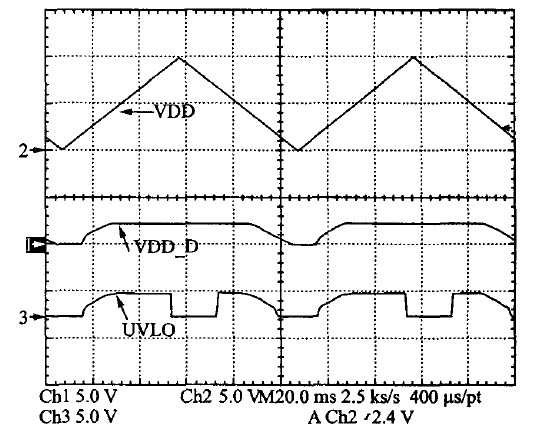

UVLO的啟動電流測量值僅為17.8 A,實現(xiàn)了系統(tǒng)的低啟動電流。系統(tǒng)上電和掉電的測試結(jié)果如圖11和圖12所示。可見系統(tǒng)在VDD的設(shè)置門限內(nèi)工作良好,REF-OK可以正確指示各個供電模塊正常工作。掉電過程正好相反。

圖11 供電模塊的上電和掉電過程(1)

圖12 供電模塊的上電和掉電過程(2)

2.4 模式控制和效率測試

系統(tǒng)的多模式控制測試結(jié)果見圖13。中載或重載下系統(tǒng)采用PWM 模式工作,許多單元的供電電源為REG=5 V.極輕載條件下則關(guān)斷5 V的供電電源,減小系統(tǒng)的待機功耗,同時也有利于減小EMI和噪聲。其過程如下:當(dāng)FB電壓低于一個閾值時,待機模式選擇,則SHUTDOWN信號變高,關(guān)斷5 V 電壓源REG模塊,同時VDD-AD繼續(xù)給芯片供電,保證在輕載時芯片的檢測能夠連續(xù)實現(xiàn)。

圖13 供電單元多模式下的節(jié)能過程

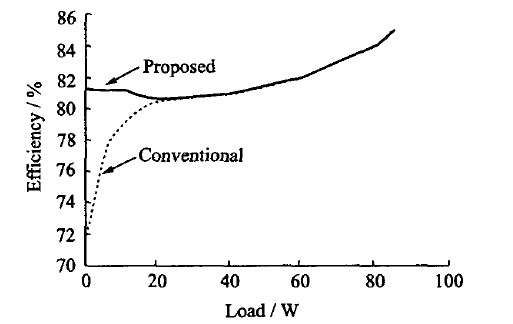

圖14給出了集成了該低功耗電源系統(tǒng)的綠色多模式反激式控制器的效率圖(工作頻率為40~130kHz),并與傳統(tǒng)的反激變換器效率進行了比較。由圖可知,采用多模式反激式控制降低了芯片的輕載功耗,提高了效率。

圖14 反激變換器效率比較

3 結(jié) 論

提出了一種開關(guān)電源控制芯片供電系統(tǒng)的設(shè)計方案,可在不同負載條件下為芯片提供合適的供電方案,保證其高效低功耗工作。設(shè)置的UVLO模塊保證了芯片在電源波動過程中的正常工作。芯片測試的結(jié)果很好地驗證了設(shè)計思想。