摘要:基于VGA接口時序,以高性能視頻D/A芯片ADV7120為核心。實現(xiàn)了基于嵌入式CPUS3C2440的VGA顯示子系統(tǒng)。系統(tǒng)一方面利用S3C24 40自帶的LCD控制器產生符合VGA顯示要求的時序邏輯,另一方面通過LCD數(shù)據(jù)線將數(shù)字RGB信號傳遞給具有8路通道的視頻D/A芯片ADV7120,產生VGA顯示需要的模擬色彩信號。通過TFTLCD掃描顯示的時序與VGA掃描顯示時序的匹配,驅動VGA顯示屏。該系統(tǒng)能夠達到正常顯示色彩信息的要求,且價格低廉,適用于對顯示效果要求不苛刻,但要求大尺寸顯示屏且對價格敏感的嵌入式應用中。

目前很多SOC廠商的微處理器芯片都集成了LCD控制器,如三星公司的S3C2410.S3C2440,Intel的Xscale系列等。大多數(shù)嵌入式系統(tǒng)也采用流行的LCD顯示技術。但是在需要大屏幕顯示、對分辨率要求不高的場合,如車間、廠房,采用大屏幕LCD則成本過高。另一方面,VGA顯示技術因為技術發(fā)展成熟,成本低廉,仍在被大量使用,直到今天它仍是所有顯示終端最為成熟的標準接口。如果讓嵌入式處理器直接支持VGA顯示器,則能很大地利用現(xiàn)有資源,節(jié)約系統(tǒng)成本。

1 基于S3C2440的VGA顯示技術分析

通過分析VGA顯示技術的時序邏輯與S3C2440內部集成LCD控制器驅動TFT LCD的時序邏輯,找出它們的共同點,分析在S3C2440上應用VGA顯示接口的可行性。

1.1 VGA顯示原理

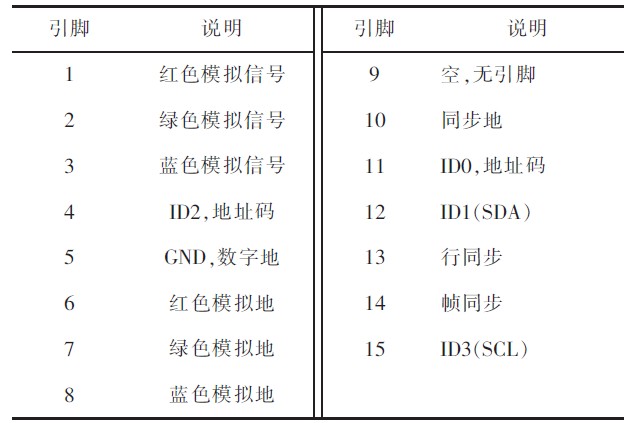

VGA(Video Graphics Arrnay)是IBM公司提出的目前仍然廣泛應用于PC的顯示接口。該接口具有分辨率高、顯示速率快、顏色豐富等優(yōu)點,在彩色顯示器領域得到了廣泛的應用。VGA接口在物理上表現(xiàn)為DB15的插座,其中VGA適配器端使用的是陰性DB15標準的接口。其引腳定義如表1所示。

表1 VGA適配器引腳定義

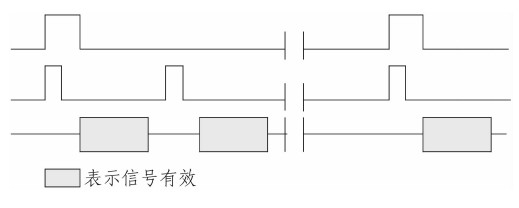

VGA接口使用模擬RGB通道,逐點、逐行掃描。其時序如圖1所示。VGA接口信號為模擬信號,其關鍵信號有5個,分別是Horizontal Sync水平同步信號(也叫行同步信號),垂直同步信號Vertical Sync(也叫場同步信號),紅色模擬信號,綠色模擬信號和籃色模擬信號。電子槍從左至右,從上而下的進行掃描,每行結束時,用行同步信號進行同步。掃描完所有的行后用場同步信號進行場同步。因電子槍偏轉需要時間,所以掃完回轉中,要對電子槍進行消隱控制,在每行結束后的回轉過程中進行行消隱,在每場結束后的回轉過程中進行場消隱。消隱過程中不發(fā)送電子束。

圖1 VGA的掃描時序

1. 2 TFT LCD顯示屏掃描時序分析

基于ARM920T內核的S3C2440芯片外圍集成了LCD控制器,LCD控制器被用來向LCD傳輸圖像數(shù)據(jù),并提供必要的控制信號,比如VFRAME、VLINE、VCLK、VM等。除此之外,LCD控制器還包括一組控制寄存器:LCDCON1寄存器、LCDCON2寄存器、LCDCON3寄存器、LCDCON4寄存器、LCD CON5寄存器。這些寄存器的設置與顯示屏信息、控制時序和數(shù)據(jù)傳輸格式等密切相關,在設計中需要根據(jù)顯示設備的具體信息正確設置這些寄存器才能使S3C2440正常控制驅動不同的顯示屏。

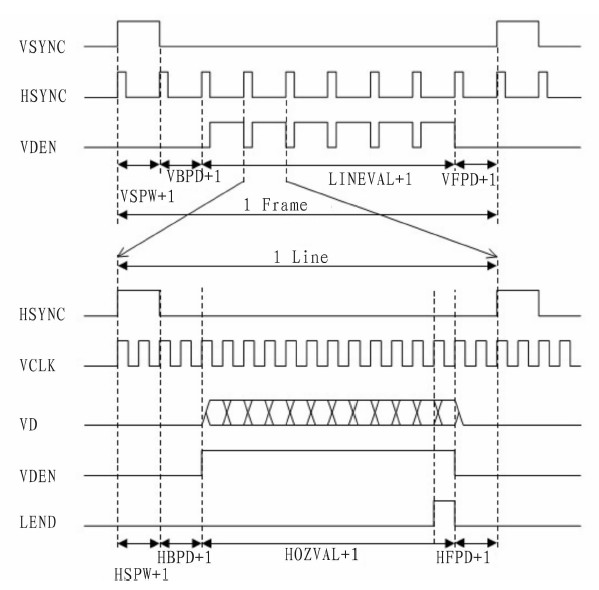

典垂的TFT液晶顯示屏的掃描對序如圖2所示。

圖2 典型TFT LCD掃描時序

其中主要包括:

1)幀(垂直)同步(VSYNC):用高電平(或低電平)表示掃描一幀的起始。

2)行(水平)同步(HSYNC):用高電平(或低電平)表示掃描一行的起始。

3)時鐘(VCLK):通過上升沿(或下降沿)把數(shù)據(jù)寫入液晶屏。

4)數(shù)據(jù)有效控制(VDEN):表示是否開啟TFT輸出。

5)數(shù)據(jù)信號(VD):表示每個點的顏色,通常有16位、18位、24位等模式。

通過對比VGA接口的時序和TFT LCD液晶顯示屏的掃描時序,可以看出它們很相似。這就為用LCD控制器驅動VGA顯示屏提供了內在的可能性。而且一旦實現(xiàn)了這種轉接方案,由于是由硬件實現(xiàn)的兩種接口的電氣轉換,不需要寫任何驅動程序,是在嵌入式系統(tǒng)平臺上擴展VGA接口的最方便的方案。比較兩種接口的特性,要實現(xiàn)從TFT時序到VGA時序的轉換,需要解決的向題有:

1)TFT液晶掃描同步信號和VGA同步信號的電平問題。

2)TFT液晶控制器的輸出是RGB數(shù)字接口,而VGA的紅綠藍通道時模擬量,兩者需要通過D/A轉換。使用D/A要考慮轉換精度、轉換速度、轉換通道數(shù)等問題。其中,為滿足真彩色(24位)的要求,8位的轉換精度就可以。基于VGA對幀頻的要求,每個點的轉換頻率必須大于27 MHz,同時,必須至少有3個通道同時轉換,以滿足紅綠藍(RGB)3個通道的輸出。

針對這種轉換的D/A通常稱為視頻D/A,本設計采用ATI公司的視頻D/A芯片ADV7120。

1.3 ADV7120簡介

ADV7120是美國ADI公司生產的高速視頻數(shù)模轉換芯片,其像素掃描時鐘頻率有30、50、80 MHz 3個等級。ADV7120在單芯片上集成了3個獨立的8位高速D/A轉換器,可以分別處理紅、綠、藍視頻數(shù)據(jù),特別適用于高分辨率模擬接口的顯示終端和要求高速D/A轉換的應用系統(tǒng)。

ADV7120的輸入及控制信號非常簡單:3組8位的數(shù)字視頻數(shù)據(jù)輸入端,分別對應RGB視頻數(shù)據(jù),數(shù)據(jù)輸入端采用標準TTL電平接口;4條視頻控制信號線包括復合同步信號SYNC、消隱信號BLANK、白電平參考信號REFWHITE和像索時鐘信號CLOCK;外接一個1.23 V數(shù)模轉換參考電壓源和1個輸出滿度調節(jié)。只有4條輸出信號線:模擬RGB信號采用高阻電流源輸出方式,可以直接驅動75 Ω同軸傳輸線;同步參考電流輸出信號Isync用來在綠視頻模擬信號中編碼視頻同步信息。

2 VGA接口電路設計

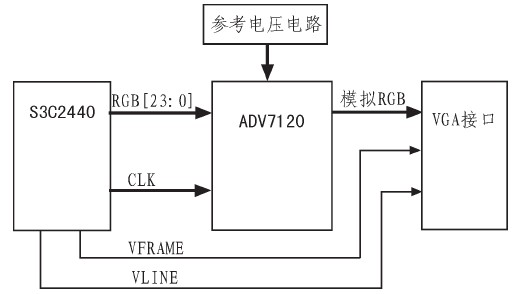

如前所述,VGA接口的時序和LCD掃描式接口的時序是一致的,利用ADV7120組成的TFT液晶時序到VGA接口的轉換模塊結構框圖如圖3所示。

圖3 VGA接口電路組成框圖

根據(jù)ADV7120的數(shù)據(jù)手冊,ADV7120對參考電平的要求度很高,不能以電阻分壓電路代替。本設計中采用了1.235 V電壓基準芯片AD589來產生參考電壓。

3 VGA顯示模式的選擇及S3C2440 LCD controller中相應控制寄存器的設置

最初VGA的顯示包含幾種模式,最初VGA的分辨率被定義為640x480,接著更高分辨率的SVGA、XVGA等標準在此基礎上被提出,接口上都兼容VGA標準,所以,習慣上把所有這種接口都稱為VGA接口。不同的顯示模式對應的VGA時序中的時間參數(shù)不同,選定一種顯示模式后,就要配置LCD控制器,使其產生的時序參數(shù)符合VGA模式的要求,這樣才能成功驅動VGA接口,否則VGA顯示端會閃爍、模糊甚至不顯示。

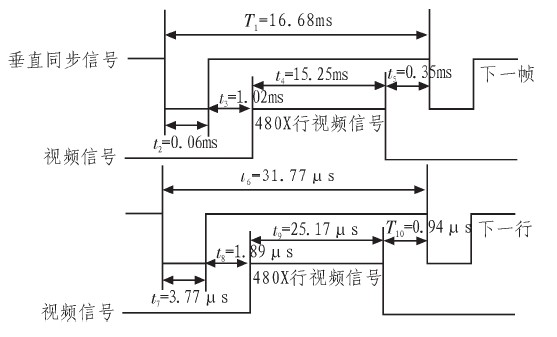

在這里選擇分辨率為640x480、刷新頻率為60 Hz、16位彩色的VGA顯示模式,并在此模式下完成對LCD控制器相關寄存器的配置。使LCD控制器輸出的時序邏輯能符合該模式下VGA顯示的要求。在該模式下VGA接口同步信號時序如圖4所示。

圖4 VGA接口同步信號時序

下面根據(jù)圖4的VGA接口同步信號時序對主要的LCD控制器中的控制寄存器進行配置:

1)LCDCON1寄存器

CLKVAL:確定VCLK頻率的參數(shù)。公式為VCLK-HCLK/[(CLKVAL+1)x2]。在本設計中S3C2440的HCLK=100 MHz,顯示屏需要VCLK=20MHz,故需設置CLKVAL=1.

BPPMODE:確定BPP(每像素位散)。選擇BPPMODE=0xC,即選擇TFT 16位模式。

2)LCDCON2寄存器

VBPD:確定幀同步信號和幀數(shù)據(jù)傳輸前的時延,是幀數(shù)據(jù)傳輸前延遲時間和行同步時鐘間隔寬度的比值,參照圖4中的時間數(shù)據(jù)可知,VBPD=t3/t6=1.02 ms/31.77 μs=32.

LINEVAL:確定顯示的垂直方向大小。公式:LINEVAL=YSIZE-1=479.

VFPD:確定幀數(shù)據(jù)傳輸完成后到下一幀同步信號到來的一段延時,是幀數(shù)據(jù)傳輸后延遲時間和行同步時鐘間隔寬度的比值,參照圖4中的時間數(shù)據(jù)可知,VFPD=t5/t6=0.35 ms/31.77μs=11.

VSPW:確定幀同步時鐘脈沖寬度,是幀同步信號時鐘寬度和行同步時鐘間隔寬度的比值。如圖4,VSPW=t2/t6=0.06 ms/31.77 μs=2.

3)LCDCON3寄存器

HBPD:確定行同步信號和行數(shù)據(jù)傳輸前的一段延時,描述行數(shù)據(jù)傳輸前延遲時間內VCLK脈沖個數(shù),如圖4,VBPD=t7xVCLK=1.89 μsx25 MHz=47.

HOZAL:確定顯示的水平方向尺寸。這里HOZAL=XSIZE-1=639.

HFPD:確定行數(shù)據(jù)傳輸完成后到下一行同步信號到來的一段延遲時間,描述行數(shù)據(jù)傳輸后延遲時間內VCLK脈沖個數(shù),如圖4,HFPD=t9xVC LK=0.94 μsx25 MHz=24.

4)LCDCON4寄存器

HSPW:確定行同步時鐘脈沖寬度。描述行同步脈沖寬度時間內VCLK脈沖個數(shù),如圖4,HSPW=3.77 μsx25 MHz=94.

5)LCDCON5寄存器

BPP24BL:確定數(shù)據(jù)存儲格式。此處設置BPP24BL=0x0,即選擇小端模式存放。

FRM565:確定16位數(shù)據(jù)輸出格式。設置FRM565=0x1,即選擇5:6:5的輸出格式。

通過如上的方式設計VGA接口電路并相應的設置LCD控制器寄存器,實現(xiàn)了LCD數(shù)字輸出與D/A轉換的無縫連接,不需要任何額外的驅動程序就可以將原來在LCD上輸出的圖像信息輸出到VGA顯示屏上。

4 測試與結論

本設計通過分析VGA接口時序與S3C2440TFT LCD接口時序的相同點,論證了用S3C2440自帶的LCD controler來驅動VGA顯示器的可行性,時序的匹配是本設計成功最關鍵的地方,在滿足接口時序要求的前提下,用高速三路8位視頻D/A芯片將LCD接口的數(shù)字RGB信號轉換成VGA接口所需要的模擬信號。實驗證明,圖像信息通過VGA轉換電路,在顯示屏上顯示良好,無明顯抖動,滿足普通的顯示要求。由于主機采用ARM嵌入式微處理器,與傳統(tǒng)X86主機相比,大大降低了整機系統(tǒng)的成本。這種廉價、簡單的顯示方案可以廣泛應用到各種對顯示效果要求不高但要求大尺寸屏幕的場合。