引言

在很多嵌入式控制系統(tǒng)中,系統(tǒng)既要完成大量的信息采集和復(fù)雜的算法,,又要實(shí)現(xiàn)精確的控制功能,。采用運(yùn)行有嵌入式Linux操作系統(tǒng)的ARM9微控制器完成信號(hào)采集及實(shí)現(xiàn)上層控制算法,并向DSP芯片發(fā)送上層算法得到控制參數(shù),,DSP芯片根據(jù)獲得的參數(shù)和下層控制算法實(shí)現(xiàn)精確,、可靠的閉環(huán)控制。

1 多機(jī)系統(tǒng)組成

該多機(jī)控制系統(tǒng)以ARM9微控制器s3c2440為核心,采用I2C總線掛載多個(gè)DSP芯片TMS320F28015作為協(xié)控制器,,構(gòu)成整個(gè)控制系統(tǒng)的核心,。

1.1 S3C2440及TMS320F28015簡(jiǎn)介

Samsung公司的處理器S3C2440是內(nèi)部集成了ARM公司ARM920T處理器內(nèi)核的32位微控制器,資源豐富,,帶獨(dú)立的16 KB的指令Cache和16 KB數(shù)據(jù)Cache,,最高主頻可達(dá)400 MHz.它擁有130個(gè)通用I/O、24個(gè)外部中斷源以及豐富的外部接口能實(shí)現(xiàn)各種功能,,包括支持多主功能的I2C總線接口,、3路URAT、2路SPI,、攝像頭接口等,。

TMS320F28015(以下簡(jiǎn)稱F28015)是TI公司的32位處理器,它具有強(qiáng)大的控制和信號(hào)處理能力,,能夠?qū)崿F(xiàn)復(fù)雜的控制算法,。片上整合了Flash存儲(chǔ)器、I2C總線模塊,、快速的A/D轉(zhuǎn)換器,、增強(qiáng)的CAN總線模塊、事件管理器,、正交編碼電路接口及多通道緩沖串口等外設(shè),此種整合能夠方便地實(shí)現(xiàn)功能的擴(kuò)展,。同時(shí),,快速的中斷響應(yīng)使它能夠保護(hù)關(guān)鍵的寄存器并快速(更小的中斷延時(shí))地響應(yīng)外部異步事件。

1.2 I2C總線接口

I2C總線是一種用于IC器件之間連接的串行總線,,采用SDA(數(shù)據(jù)線)和SCL(時(shí)鐘線)兩線連接每個(gè)帶有I2C總線接口的器件或模塊,。串行的8位雙向數(shù)據(jù)傳輸率在標(biāo)準(zhǔn)模式下可達(dá)100 kb/s,快速模式下可達(dá)400 kb/s.多個(gè)微控制器可以通過(guò)I2C總線接口非常方便地連接在一起構(gòu)成系統(tǒng),,并根據(jù)地址識(shí)別每個(gè)器件,。這種總線結(jié)構(gòu)的連線和連接引腳少,器件間總線簡(jiǎn)單,,結(jié)構(gòu)緊湊,。因此其構(gòu)成系統(tǒng)的成本較低,并且在總線上增加器件不會(huì)影響系統(tǒng)的正常工作,,所有的I2C總線器件共用一套總線,,因此其系統(tǒng)修改和可擴(kuò)展性好。

總線必須由主機(jī)(通常為微控制器)控制,,主機(jī)產(chǎn)生串行時(shí)鐘( SCL) 控制總線的數(shù)據(jù)傳輸,,并產(chǎn)生起始和停止條件。SDA 線上的數(shù)據(jù)狀態(tài)僅在SCL為低電平的期間才能改變,SCL為高電平的期間,,SDA 狀態(tài)的改變被用來(lái)表示起始和停止條件,。I2C總線起始和停止時(shí)序如圖1所示。

圖1 I2C總線起始和停止時(shí)序

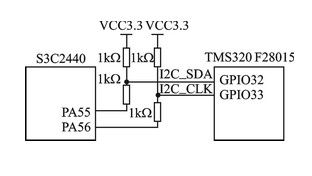

1.3 硬件電路

S3C2440和F28015自身均集成了I2C總線模塊,,支持多主設(shè)備I2C總線串行接口,,可以方便地掛接到I2C總線上。因此,,兩者之間的I2C總線接口電路的設(shè)計(jì)變得十分簡(jiǎn)單,,只要將兩者的對(duì)應(yīng)引腳I2C_CLK(對(duì)應(yīng)I2C總線中的SCL線)和I2C_SDA(對(duì)應(yīng)I2C總線中的DATA線)連接起來(lái)即可。S3C2440和TMS320F28015的硬件接口電路如圖2所示,。

圖2 S3C2440和TMS320F28015的硬件接口

電路S3C2440的PA55和PA56引腳分別對(duì)應(yīng)I2C_SDA和I2C_CLK,,而F28015的GPIO32和GPIO33也可以分別復(fù)用為I2C_SDA和I2C_CLK.考慮到阻抗不匹配等因素會(huì)影響總線數(shù)據(jù)傳輸效果,因此在將兩塊芯片的I2C_DATA和I2C_CLK引腳直連時(shí),,在直連線路上各串聯(lián)一個(gè)小電阻,。

I2C_SDA和I2C_CLK是雙向電路,必須都通過(guò)一個(gè)電流源或上拉電阻連接到正電源電壓上,。由于S3C2440和F28015的輸出高電平均為3.3 V,,所以在硬件設(shè)計(jì)時(shí)將I2C_SDA和I2C_CLK總線通過(guò)上拉電阻連接到了3.3 V的VCC電源上。

2 ARM和DSP通信軟件設(shè)計(jì)

運(yùn)行Linux操作系統(tǒng)的ARM微控制器作為主控制器,,在數(shù)據(jù)管理及多任務(wù)調(diào)度等方面有顯著優(yōu)勢(shì),,可以很好地組織外圍器件采集的數(shù)據(jù);主要實(shí)現(xiàn)對(duì)系統(tǒng)的整體控制,,并通過(guò)總線設(shè)備驅(qū)動(dòng)程序控制I2C總線模塊,,通過(guò)主機(jī)尋址實(shí)現(xiàn)向I2C總線上掛載的下層DSP的數(shù)據(jù)收發(fā)。為保證數(shù)據(jù)通信的實(shí)時(shí)性,,F(xiàn)28015通過(guò)中斷響應(yīng)的方式實(shí)現(xiàn)數(shù)據(jù)接收和發(fā)送,。

2.1 ARM9平臺(tái)的嵌入式Linux的I2C總線驅(qū)動(dòng)設(shè)計(jì)

2.1.1 I2C總線讀寫(xiě)時(shí)序

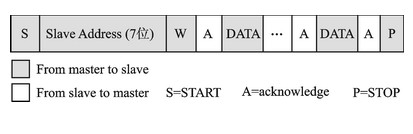

ARM9微控制器作為主機(jī)向從機(jī)DSP寫(xiě)數(shù)據(jù),首先向從機(jī)發(fā)送啟動(dòng)信號(hào),,然后發(fā)送7位從機(jī)地址和1位寫(xiě)標(biāo)志位,,再等待從機(jī)的應(yīng)答信號(hào)。在收到應(yīng)答信號(hào)后,,主機(jī)發(fā)送數(shù)據(jù)給從機(jī),,再次等待應(yīng)答信號(hào)。當(dāng)主機(jī)收到應(yīng)答信號(hào)之后再次發(fā)送數(shù)據(jù),。之后,,主機(jī)等待從機(jī)的應(yīng)答信號(hào),如此直到數(shù)據(jù)發(fā)送完成,,主機(jī)發(fā)送停止信號(hào),。I2C總線寫(xiě)數(shù)據(jù)幀格式如圖3所示,。

圖3 I2C總線寫(xiě)數(shù)據(jù)幀格式

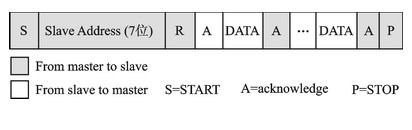

主模式下讀數(shù)據(jù),是指每次從指定的位置讀取一個(gè)或多個(gè)字節(jié)數(shù)據(jù),。主機(jī)首先向從機(jī)發(fā)送啟動(dòng)信號(hào),,然后發(fā)送 7位從機(jī)地址和1位讀標(biāo)志位,等待從機(jī)應(yīng)答,。當(dāng)收到從機(jī)的應(yīng)答信號(hào)后,,主機(jī)準(zhǔn)備接收從機(jī)發(fā)送的數(shù)據(jù),接收完成后發(fā)送一個(gè)應(yīng)答信號(hào),,如此直到數(shù)據(jù)接收完成,,主機(jī)發(fā)送一個(gè)停止信號(hào)。圖4為I2C總線讀數(shù)據(jù)幀格式,。

圖4 I2C總線讀數(shù)據(jù)幀格式

2.1.2 Linux下I2C總線驅(qū)動(dòng)程序概述

Linux系統(tǒng)的I2C總線驅(qū)動(dòng)采用體系化結(jié)構(gòu)設(shè)計(jì),,包括I2C總線適配器驅(qū)動(dòng)和I2C總線設(shè)備驅(qū)動(dòng)??偩€驅(qū)動(dòng)實(shí)現(xiàn)對(duì)I2C總線適配器(S3C2440的I2C總線模塊)的控制,,設(shè)備驅(qū)動(dòng)實(shí)現(xiàn)對(duì)具體設(shè)備(F28015的I2C總線模塊)的讀寫(xiě)控制。圖5為總體驅(qū)動(dòng)框架,,可以分為三個(gè)層次:

?、?I2C框架。內(nèi)核中i2c.h和i2ccore.c為I2C總線框架的主體,,提供了核心數(shù)據(jù)結(jié)構(gòu)的定義,、I2C總線適配器驅(qū)動(dòng)和設(shè)備驅(qū)動(dòng)的注冊(cè)、注銷管理,、I2C總線通信方法上層的,、與具體適配器無(wú)關(guān)的代碼、檢測(cè)設(shè)備地址的上層代碼等,。i2cdev.c用于創(chuàng)建I2C總線適配器的設(shè)備節(jié)點(diǎn),提供I2C總線設(shè)備訪問(wèn)方法等,。

?、?I2C總線適配器驅(qū)動(dòng)。定義描述具體I2C總線適配器的數(shù)據(jù)結(jié)構(gòu),,實(shí)現(xiàn)在具體I2C總線適配器上的I2C總線通信方法,。

③ I2C總線設(shè)備驅(qū)動(dòng),。定義描述具體設(shè)備的數(shù)據(jù)結(jié)構(gòu),,借助I2C總線框架的相關(guān)函數(shù)實(shí)現(xiàn)設(shè)備的注冊(cè),并為用戶提供上層應(yīng)用程序編程接口,。

圖5 總體驅(qū)動(dòng)框架

Linux的I2C總線驅(qū)動(dòng)框架中的主要數(shù)據(jù)結(jié)構(gòu)包括: i2c_driver,、i2c_client,、i2c_adapter和 i2c_algorithm,它們被定義在內(nèi)核中的i2c. h頭文件中,。i2c_adapter對(duì)應(yīng)于物理上的一個(gè)適配器,,而i2c_algorithm對(duì)應(yīng)一套通信方法,用來(lái)為適配器提供通信函數(shù),。i2c_algorithm中的關(guān)鍵函數(shù)master_xfer()用于產(chǎn)生I2C總線訪問(wèn)周期需要的信號(hào),,以i2c_msg(即I2C總線消息)為單位。該結(jié)構(gòu)體原型如下:

struct i2c_msg{

_ _u16 addr;/*設(shè)備地址*/

_ _u16 flags;/*標(biāo)志*/

_ _u16 len;/*消息長(zhǎng)度*/

_ _u8 *buf;/*消息數(shù)據(jù)*/

};

i2c_driver對(duì)應(yīng)一套驅(qū)動(dòng)方法,,是用于輔助作用的數(shù)據(jù)結(jié)構(gòu),。i2c_client對(duì)應(yīng)于真實(shí)的物理設(shè)備,每個(gè)I2C總線設(shè)備都需要一個(gè)i2c_client來(lái)描述,。i2c_adapter和i2c_client的關(guān)系與I2C總線硬件體系中適配器和設(shè)備關(guān)系一致,,即i2c_client依附于i2c_adapter.

圖6 設(shè)備驅(qū)動(dòng)模塊加載流程

在Linux內(nèi)核源代碼中drivers目錄下的i2c_dev.c文件,是通用的I2C總線設(shè)備驅(qū)動(dòng)文件,,為應(yīng)用程序提供open(),、write()、read ),、ioctl()和close()等操作接口來(lái)訪問(wèn)設(shè)備,。應(yīng)用層可以借用這些接口訪問(wèn)掛接在適配器上的I2C總線設(shè)備的存儲(chǔ)空間或寄存器,并控制I2C總線設(shè)備的工作方式,。

2.1.3 S3C2440的I2C總線驅(qū)動(dòng)

設(shè)備驅(qū)動(dòng)S3C2440內(nèi)部的I2C總線控制器通過(guò)4個(gè)寄存器實(shí)現(xiàn)對(duì)通信的控制,,分別是I2C控制寄存器(I2CCON)、I2C狀態(tài)寄存器(I2CSTAT),、I2C收發(fā)數(shù)據(jù)移位寄存器(I2CDS),、I2C地址寄存器(I2CADD)。

按照Linux中I2C總線框架要求,,S3C2440的I2C總線驅(qū)動(dòng)設(shè)計(jì)主要完成以下工作:設(shè)計(jì)i2c_adapter_s3c_init()模板加載函數(shù)和對(duì)應(yīng)于i2c_adapter_s3c_exit()模板卸載函數(shù),;設(shè)計(jì)i2c_adapter_s3c_xfer()模板S3C2440適配器通信方法函數(shù)。

i2c_adapter_s3c_init()通過(guò)注冊(cè)s3c2440_i2c_driver結(jié)構(gòu)體實(shí)現(xiàn)總線驅(qū)動(dòng)的平臺(tái)注冊(cè),,s3c2440_i2c_driver結(jié)構(gòu)體包含了具體適配器的probe()函數(shù),、remove()函數(shù)、resume()函數(shù)指針等信息,。代碼如下:

static int _ _init i2c_adap_s3c_init(){

int ret;

ret=platform_driver_regisiter(&s3c2440_i2c_driver),;//注冊(cè)platform_driver結(jié)構(gòu)體

if(ret==0){//注冊(cè)失敗

ret=platform_driver_regisiter(&s3c2440_i2c_driver);

if(ret)

platform_driver_unregisiter (&s3c2440_i2c_driver),;

}

return ret;

}

static struct platform_driver s3c2440_i2c_driver={

.probe=s3c24xx_i2c_probe,,

.remove=s3c24xx_i2c_remove,

.resume=s3c24xx_i2c_resume,,

.driver={

.owner=THIS MODULE,,

.name=“s3c2440i2c”,,

},

} ;

完成了S3C2440的I2C總線適配器驅(qū)動(dòng)注冊(cè)后,,就可以將具體設(shè)備驅(qū)動(dòng)注冊(cè)到該總線平臺(tái)上,,實(shí)現(xiàn)I2C總線數(shù)據(jù)通信。i2c_dev.c文件是內(nèi)核源碼提供的通用I2C總線設(shè)備驅(qū)動(dòng)文件,,針對(duì)每個(gè)I2C總線適配器生成一個(gè)主設(shè)備號(hào)為89的設(shè)備文件,,設(shè)備驅(qū)動(dòng)模塊加載流程如圖6所示。完成加載后,,驅(qū)動(dòng)提供i2cdev_read(),、i2cdev_write()、i2cdev_ioctl()函數(shù)來(lái)對(duì)應(yīng)用戶空間的read(),、write(),、ioctl()函數(shù),供用戶使用,。用戶通過(guò)這些接口函數(shù)實(shí)現(xiàn)I2C總線數(shù)據(jù)的讀寫(xiě)功能,。

2.2 DSP數(shù)據(jù)接收中斷程序設(shè)計(jì)

圖7 I2C總線中斷服務(wù)程序流程

通過(guò)配置F28015的I2C模塊寄存器,設(shè)置I2C模塊為從工作方式,,同時(shí)利用I2C總線中斷響應(yīng)程序?qū)崿F(xiàn)對(duì)總線上數(shù)據(jù)的接收和發(fā)送,,進(jìn)而完成數(shù)據(jù)通信。F28015產(chǎn)生了I2C總線中斷后,,就執(zhí)行中斷服務(wù)程序,,圖7為I2C總線中斷服務(wù)程序流程。

中斷服務(wù)程序通過(guò)查詢狀態(tài)寄存器(I2CSTR)標(biāo)志位,,得出中斷類型碼,,然后調(diào)用相應(yīng)的子程序,完成數(shù)據(jù)接收發(fā)送,。代碼如下:

interrupt void i2c_int1a_isr(void) {//I2CA的中斷響應(yīng)函數(shù)

Uint16 IntSource;// 讀取中斷碼

IntSource=I2caRegs.I2CISRC.bit.INTCODE & 0x7;//I2CA中斷源,,讀后3位

switch(IntSource){//依中斷源而確定相關(guān)接收和發(fā)送策略

case I2C_NO_ISRC://=0

case I2C_ARB_ISRC://=1

case I2C_NACK_ISRC: //=2

case I2C_ARDY_ISRC: //=3

case I2C_SCD_ISRC://=6

case I2C_AAS_ISRC://=7

break;

case I2C_RX_ISRC://=4,接收數(shù)據(jù)已準(zhǔn)備好

DataReceive(),;//調(diào)用數(shù)據(jù)接收子函數(shù)接收數(shù)據(jù)

break;

case I2C_TX_ISRC://=5,,發(fā)送數(shù)據(jù)已準(zhǔn)備好

DataTransmit();//調(diào)用數(shù)據(jù)發(fā)送子函數(shù)接收數(shù)據(jù)

break;

default:

asm(“ESTOP0”),; //無(wú)效數(shù)據(jù),,則停止

}

PieCtrlRegs.PIEACK.all=PIEACK_GROUP8;

}

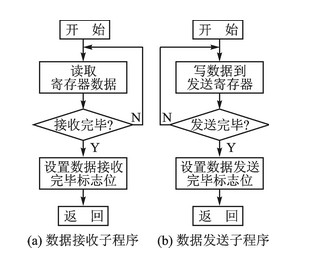

F28015中的數(shù)據(jù)接收子程序和數(shù)據(jù)發(fā)送子程序是在I2C總線的中斷服務(wù)程序中根據(jù)不同的狀態(tài)碼進(jìn)行調(diào)用,,它們是整個(gè)通信程序的核心部分,。數(shù)據(jù)接收子程序和數(shù)據(jù)發(fā)送子程序的流程如圖8所示。

圖8 數(shù)據(jù)接收和發(fā)送子程序

3 測(cè)試結(jié)果

通過(guò)NFS文件系統(tǒng)將編譯成模塊的I2C的總線驅(qū)動(dòng)和設(shè)備驅(qū)動(dòng)加載到運(yùn)行Linux操作系統(tǒng)的S3C2440平臺(tái)上(先加載總線驅(qū)動(dòng)),,再將F28015的測(cè)試程序燒寫(xiě)到RAM中,。運(yùn)行F28015等待I2C總線上的數(shù)據(jù),,再執(zhí)行Linux系統(tǒng)中的I2C總線測(cè)試程序。測(cè)試結(jié)果顯示,,芯片通過(guò)I2C總線接口完成了數(shù)據(jù)通信,,具有良好的實(shí)時(shí)性和可靠性。

4 結(jié)論

該設(shè)計(jì)利用I2C總線實(shí)現(xiàn)了ARM9微控制器與DSP芯片間實(shí)時(shí)可靠的數(shù)據(jù)通信,。ARM9微控制器結(jié)合Linux操作系統(tǒng)作為上層控制核心,,DSP芯片實(shí)現(xiàn)下層控制算法,可充分發(fā)揮ARM9微控制器在數(shù)據(jù)采集和任務(wù)管理等方面的優(yōu)勢(shì)以及DSP芯片在算法實(shí)現(xiàn)和底層控制的長(zhǎng)處,。