說(shuō)明:

Kernel版本:4.14

ARM64處理器

Linux PCI驅(qū)動(dòng)框架分析(一)

1. 概述

從本文開(kāi)始,將會(huì)針對(duì)PCIe專(zhuān)題來(lái)展開(kāi),涉及的內(nèi)容包括:

PCI/PCIe總線(xiàn)硬件;

Linux PCI驅(qū)動(dòng)核心框架;

Linux PCI Host控制器驅(qū)動(dòng);

不排除會(huì)包含PCIe外設(shè)驅(qū)動(dòng)模塊,一切隨緣。

作為專(zhuān)題的第一篇,當(dāng)然會(huì)先從硬件總線(xiàn)入手。進(jìn)入主題前,先講點(diǎn)背景知識(shí)。在PC時(shí)代,隨著處理器的發(fā)展,經(jīng)歷了幾代I/O總線(xiàn)的發(fā)展,解決的問(wèn)題都是CPU主頻提升與外部設(shè)備訪(fǎng)問(wèn)速度的問(wèn)題:

第一代總線(xiàn)包含ISA、EISA、VESA和Micro Channel等;

第二代總線(xiàn)包含PCI、AGP、PCI-X等;

第三代總線(xiàn)包含PCIe、mPCIe、m.2等;

PCIe(PCI Express)是目前PC和嵌入式系統(tǒng)中最常用的高速總線(xiàn),PCIe在PCI的基礎(chǔ)上發(fā)展而來(lái),在軟件上PCIe與PCI是后向兼容的,PCI的系統(tǒng)軟件可以用在PCIe系統(tǒng)中。

本文會(huì)分兩部分展開(kāi),先介紹PCI總線(xiàn),然后再介紹PCIe總線(xiàn),方便在理解上的過(guò)渡,開(kāi)始旅程吧。

2. PCI Local Bus

2.1 PCI總線(xiàn)組成

PCI總線(xiàn)(Peripheral Component Interconnect,外部設(shè)備互聯(lián)),由Intel公司提出,其主要功能是連接外部設(shè)備;

PCI Local Bus,PCI局部總線(xiàn),局部總線(xiàn)技術(shù)是PC體系結(jié)構(gòu)發(fā)展的一次變革,是在ISA總線(xiàn)和CPU總線(xiàn)之間增加的一級(jí)總線(xiàn)或管理層,可將一些高速外設(shè),如圖形卡、硬盤(pán)控制器等從ISA總線(xiàn)上卸下,而通過(guò)局部總線(xiàn)直接掛接在CPU總線(xiàn)上,使之與高速CPU總線(xiàn)相匹配。PCI總線(xiàn),指的就是PCI Local Bus。

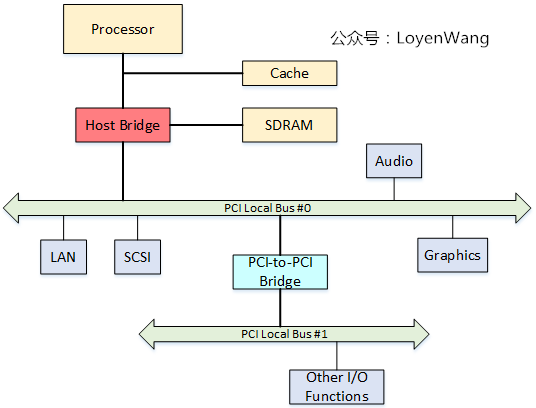

先來(lái)看一下PCI Local Bus的系統(tǒng)架構(gòu)圖:

從圖中看,與PCI總線(xiàn)相關(guān)的模塊包括:

Host Bridge,比如PC中常見(jiàn)的North Bridge(北橋)。圖中處理器、Cache、內(nèi)存子系統(tǒng)通過(guò)Host Bridge連接到PCI上,Host Bridge管理PCI總線(xiàn)域,是聯(lián)系處理器和PCI設(shè)備的橋梁,完成處理器與PCI設(shè)備間的數(shù)據(jù)交換。其中數(shù)據(jù)交換,包含處理器訪(fǎng)問(wèn)PCI設(shè)備的地址空間和PCI設(shè)備使用DMA機(jī)制訪(fǎng)問(wèn)主存儲(chǔ)器,在PCI設(shè)備用DMA訪(fǎng)問(wèn)存儲(chǔ)器時(shí),會(huì)存在Cache一致性問(wèn)題,這個(gè)也是Host Bridge設(shè)計(jì)時(shí)需要考慮的;此外,Host Bridge還可選的支持仲裁機(jī)制,熱插拔等;

PCI Local Bus;PCI總線(xiàn),由Host Bridge或者PCI-to-PCI Bridge管理,用來(lái)連接各類(lèi)設(shè)備,比如聲卡、網(wǎng)卡、IDE接口等。可以通過(guò)PCI-to-PCI Bridge來(lái)擴(kuò)展PCI總線(xiàn),并構(gòu)成多級(jí)總線(xiàn)的總線(xiàn)樹(shù),比如圖中的PCI Local Bus #0和PCI Local Bus #1兩條PCI總線(xiàn)就構(gòu)成一顆總線(xiàn)樹(shù),同屬一個(gè)總線(xiàn)域;

PCI-To-PCI Bridge;PCI橋,用于擴(kuò)展PCI總線(xiàn),使采用PCI總線(xiàn)進(jìn)行大規(guī)模系統(tǒng)互聯(lián)成為可能,管理下游總線(xiàn),并轉(zhuǎn)發(fā)上下游總線(xiàn)之間的事務(wù);

PCI Device;PCI總線(xiàn)中有三類(lèi)設(shè)備:PCI從設(shè)備,PCI主設(shè)備,橋設(shè)備。PCI從設(shè)備:被動(dòng)接收來(lái)自Host Bridge或者其他PCI設(shè)備的讀寫(xiě)請(qǐng)求;PCI主設(shè)備:可以通過(guò)總線(xiàn)仲裁獲得PCI總線(xiàn)的使用權(quán),主動(dòng)向其他PCI設(shè)備或主存儲(chǔ)器發(fā)起讀寫(xiě)請(qǐng)求;橋設(shè)備:管理下游的PCI總線(xiàn),并轉(zhuǎn)發(fā)上下游總線(xiàn)之間的總線(xiàn)事務(wù),包括PCI橋、PCI-to-ISA橋、PCI-to-Cardbus橋等。

2.2 PCI總線(xiàn)信號(hào)定義

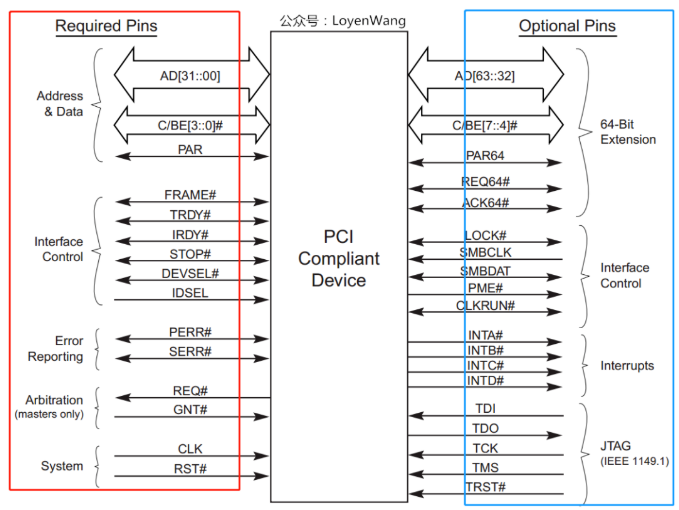

PCI總線(xiàn)是一條共享總線(xiàn),可以?huà)旖佣鄠€(gè)PCI設(shè)備,PCI設(shè)備通過(guò)一系列信號(hào)與PCI總線(xiàn)相連,包括:地址/數(shù)據(jù)信號(hào)、接口控制信號(hào)、仲裁信號(hào)、中斷信號(hào)等。如下圖:

左側(cè)紅色框里表示的是PCI總線(xiàn)必需的信號(hào),而右側(cè)藍(lán)色框里表示的是可選的信號(hào);

AD[31:00]:地址與數(shù)據(jù)信號(hào)復(fù)用,在傳送時(shí)第一個(gè)時(shí)鐘周期傳送地址,下一個(gè)時(shí)鐘周期傳送數(shù)據(jù);

C/BE[3:0]#:PCI總線(xiàn)命令與字節(jié)使能信號(hào)復(fù)用,在地址周期中表示的是PCI總線(xiàn)命令,在數(shù)據(jù)周期中用于字節(jié)選擇,可以進(jìn)行單字節(jié)、字、雙字訪(fǎng)問(wèn);

PAR:奇偶校驗(yàn)信號(hào),確保AD[31:00]和C/BE[3:0]#傳遞的正確性;

Interface Control:接口控制信號(hào),主要作用是保證數(shù)據(jù)的正常傳遞,并根據(jù)PCI主從設(shè)備的狀態(tài),暫停、終止或者正常完成總線(xiàn)事務(wù):

FRAME#:表示PCI總線(xiàn)事務(wù)的開(kāi)始與結(jié)束;

IRDY#:信號(hào)由PCI主設(shè)備驅(qū)動(dòng),信號(hào)有效時(shí)表示PCI主設(shè)備數(shù)據(jù)已經(jīng)ready;

TRDY#:信號(hào)由目標(biāo)設(shè)備驅(qū)動(dòng),信號(hào)有效時(shí)表示目標(biāo)設(shè)備數(shù)據(jù)已經(jīng)ready;

STOP#:目標(biāo)設(shè)備請(qǐng)求主設(shè)備停止當(dāng)前總線(xiàn)事務(wù);

DEVSEL#:PCI總線(xiàn)的目標(biāo)設(shè)備已經(jīng)準(zhǔn)備好;

IDSEL:PCI總線(xiàn)在配置讀寫(xiě)總線(xiàn)事務(wù)時(shí),使用該信號(hào)選擇PCI目標(biāo)設(shè)備;

Arbitration:仲裁信號(hào),由REQ#和GNT#組成,與PCI總線(xiàn)的仲裁器直接相連,只有PCI主設(shè)備需要使用該組信號(hào),每條PCI總線(xiàn)上都有一個(gè)總線(xiàn)仲裁器;

Error Reporting:錯(cuò)誤信號(hào),包括PERR#奇偶校驗(yàn)錯(cuò)誤和SERR系統(tǒng)錯(cuò)誤;

System:系統(tǒng)信號(hào),包括時(shí)鐘信號(hào)和復(fù)位信號(hào);

看一下C/BE[3:0]都有哪些命令吧:

2.3 PCI事務(wù)模型

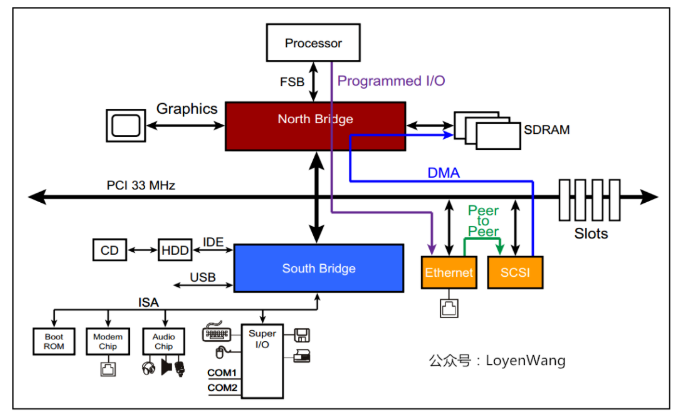

PCI使用三種模型用于數(shù)據(jù)的傳輸:

Programmed I/O:通過(guò)IO讀寫(xiě)訪(fǎng)問(wèn)PCI設(shè)備空間;

DMA:PIO的方式比較低效,DMA的方式可以直接去訪(fǎng)問(wèn)主存儲(chǔ)器而無(wú)需CPU干預(yù),效率更高;

Peer-to-peer:兩臺(tái)PCI設(shè)備之間直接傳送數(shù)據(jù);

2.4 PCI總線(xiàn)地址空間映射

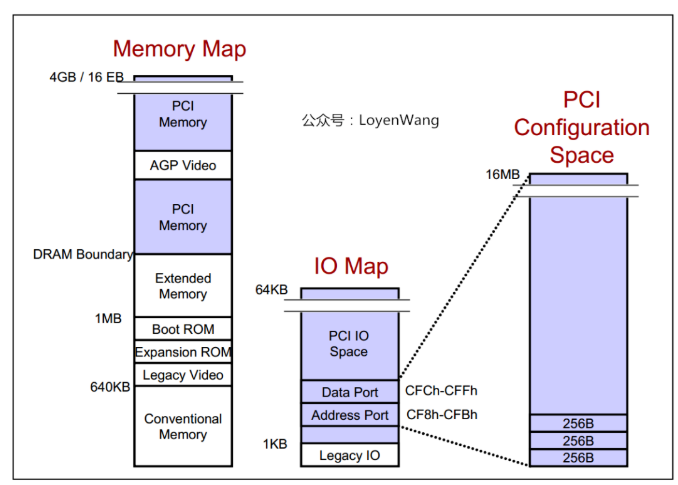

PCI體系架構(gòu)支持三種地址空間:

memory空間:針對(duì)32bit尋址,支持4G的地址空間,針對(duì)64bit尋址,支持16EB的地址空間;

I/O空間PCI最大支持4G的IO空間,但受限于x86處理器的IO空間(16bits帶寬),很多平臺(tái)將PCI的IO地址空間限定在64KB;

配置空間x86 CPU可以直接訪(fǎng)問(wèn)memory空間和I/O空間,而配置空間則不能直接訪(fǎng)問(wèn);每個(gè)PCI功能最多可以有256字節(jié)的配置空間;PCI總線(xiàn)在進(jìn)行配置的時(shí)候,采用ID譯碼方式,使用設(shè)備的ID號(hào),包括Bus Number,Device Number,F(xiàn)unction Number和Register Number,每個(gè)系統(tǒng)支持256條總線(xiàn),每條總線(xiàn)支持32個(gè)設(shè)備,每個(gè)設(shè)備支持8個(gè)功能,由于每個(gè)功能最多有256字節(jié)的配置空間,因此總的配置空間大小為:256B * 8 * 32 * 256 = 16M;

有必要再進(jìn)一步介紹一下配置空間:x86 CPU無(wú)法直接訪(fǎng)問(wèn)配置空間,通過(guò)IO映射的數(shù)據(jù)端口和地址端口間接訪(fǎng)問(wèn)PCI的配置空間,其中地址端口映射到0CF8h - 0CFBh,數(shù)據(jù)端口映射到0CFCh - 0CFFh;

圖為配置地址寄存器構(gòu)成,PCI的配置過(guò)程分為兩步:

CPU寫(xiě)CF8h端口,其中寫(xiě)的內(nèi)容如圖所示,BUS,Device,F(xiàn)unction能標(biāo)識(shí)出特定的設(shè)備功能,Doubleword來(lái)指定配置空間的具體某個(gè)寄存器;

CPU可以IO讀寫(xiě)CFCh端口,用于讀取步驟1中的指定寄存器內(nèi)容,或者寫(xiě)入指定寄存器內(nèi)容。這個(gè)過(guò)程有點(diǎn)類(lèi)似于通過(guò)I2C去配置外接芯片;

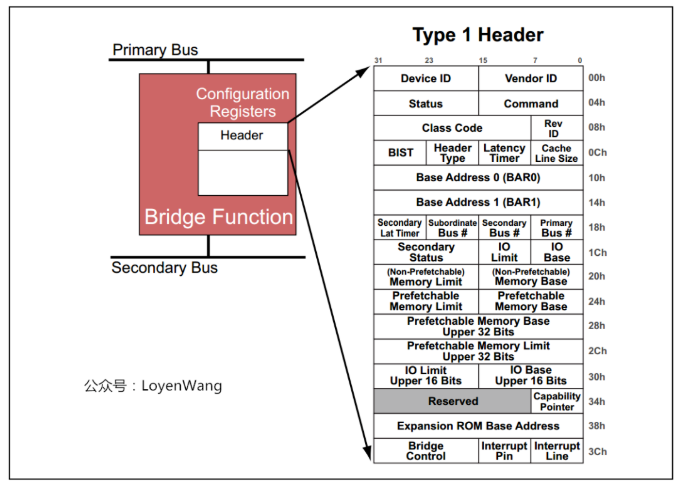

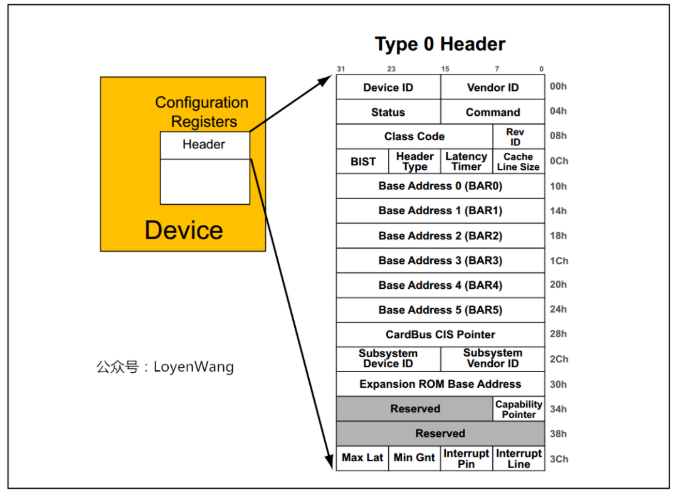

那具體的配置空間寄存器都是什么樣的呢?每個(gè)功能256Byte,前邊64Byte是Header,剩余的192Byte支持可選功能。有種類(lèi)型的PCI功能:Bridge和Device,兩者的Header都不一樣。

Bridge

Device

配置空間中有個(gè)寄存器字段需要說(shuō)明一下:

Base Address Register,也就是BAR空間,當(dāng)PCI設(shè)備的配置空間被初始化后,該設(shè)備在PCI總線(xiàn)上就會(huì)擁有一個(gè)獨(dú)立的PCI總線(xiàn)地址空間,這個(gè)空間就是BAR空間,BAR空間可以存放IO地址空間,也可以存放存儲(chǔ)器地址空間。

PCI總線(xiàn)取得了很大的成功,但隨著CPU的主頻不斷提高,PCI總線(xiàn)的帶寬也捉襟見(jiàn)肘。此外,它本身存在一些架構(gòu)上的缺陷,面臨一系列挑戰(zhàn),包括帶寬、流量控制、數(shù)據(jù)傳送質(zhì)量等;

PCIe應(yīng)運(yùn)而生,能有效解決這些問(wèn)題,所以PCIe才是我們的主角;

3. PCI Express

3.1 PCIe體系結(jié)構(gòu)

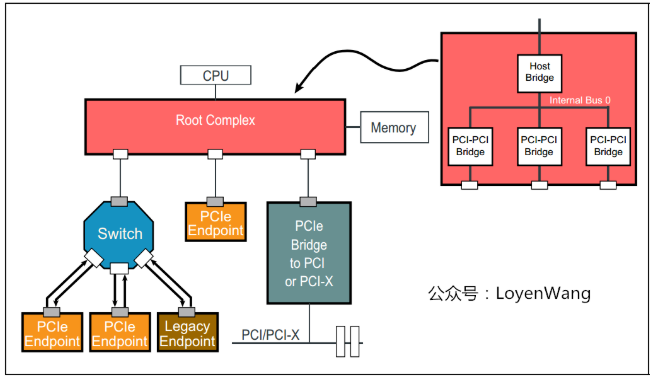

先看一下PCIe架構(gòu)的組成圖:

Root Complex:CPU和PCIe總線(xiàn)之間的接口可能會(huì)包含幾個(gè)模塊(處理器接口、DRAM接口等),甚至可能還會(huì)包含芯片,這個(gè)集合就稱(chēng)為Root Complex,它作為PCIe架構(gòu)的根,代表CPU與系統(tǒng)其它部分進(jìn)行交互。廣義來(lái)說(shuō),Root Complex可以認(rèn)為是CPU和PCIe拓?fù)渲g的接口,Root Complex會(huì)將CPU的request轉(zhuǎn)換成PCIe的4種不同的請(qǐng)求(Configuration、Memory、I/O、Message);

Switch:從圖中可以看出,Swtich提供扇出能力,讓更多的PCIe設(shè)備連接在PCIe端口上;

Bridge:橋接設(shè)備,用于去連接其他的總線(xiàn),比如PCI總線(xiàn)或PCI-X總線(xiàn),甚至另外的PCIe總線(xiàn);

PCIe Endpoint:PCIe設(shè)備;

圖中白色的小方塊代表Downstream端口,灰色的小方塊代表Upstream端口;

前文提到過(guò),PCIe在軟件上保持了后向兼容性,那么在PCIe的設(shè)計(jì)上,需要考慮在PCI總線(xiàn)上的軟件視角,比如Root Complex的實(shí)現(xiàn)可能就如下圖所示,從而看起來(lái)與PCI總線(xiàn)相差無(wú)異:

Root Complex通常會(huì)實(shí)現(xiàn)一個(gè)內(nèi)部總線(xiàn)結(jié)構(gòu)和多個(gè)橋,從而扇出到多個(gè)端口上;

Root Complex的內(nèi)部實(shí)現(xiàn)不需要遵循標(biāo)準(zhǔn),因此都是廠(chǎng)家specific的;

而Switch的實(shí)現(xiàn)可能如下圖所示:

Switch就是一個(gè)擴(kuò)展設(shè)備,所以看起來(lái)像是各種橋的連接路由;

3.2 PCIe數(shù)據(jù)傳輸

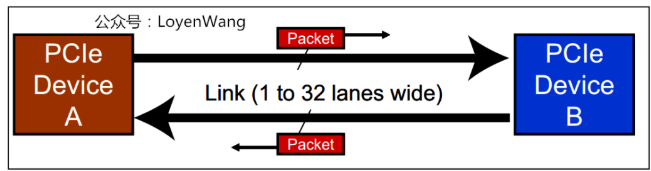

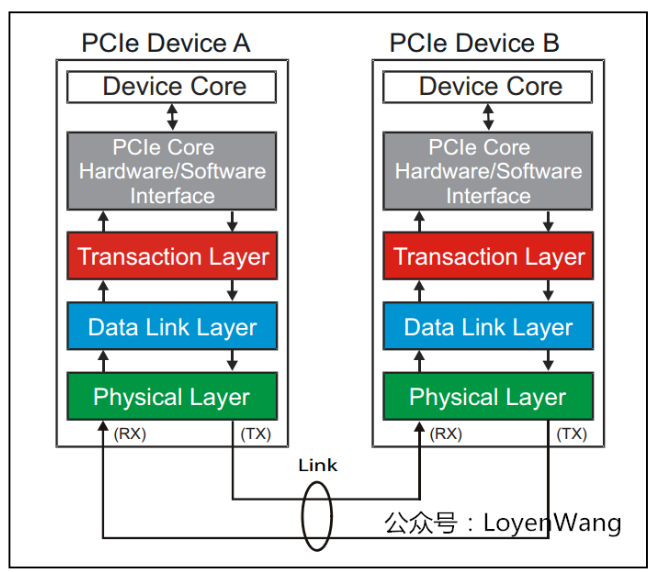

與PCI總線(xiàn)不同(PCI設(shè)備共享總線(xiàn)),PCIe總線(xiàn)使用端到端的連接方式,互為接收端和發(fā)送端,全雙工,基于數(shù)據(jù)包的傳輸;

物理底層采用差分信號(hào)(PCI鏈路采用并行總線(xiàn),而PCIe鏈路采用串行總線(xiàn)),一條Lane中有兩組差分信號(hào),共四根信號(hào)線(xiàn),而PCIe Link可以由多條Lane組成,可以支持1、2、4、8、12、16、32條;

PCIe規(guī)范定義了分層的架構(gòu)設(shè)計(jì),包含三層:

Transaction層

負(fù)責(zé)TLP包(Transaction Layer Packet)的封裝與解封裝,此外還負(fù)責(zé)QoS,流控、排序等功能;

Data Link層

負(fù)責(zé)DLLP包(Data Link Layer Packet)的封裝與解封裝,此外還負(fù)責(zé)鏈接錯(cuò)誤檢測(cè)和校正,使用Ack/Nak協(xié)議來(lái)確保傳輸可靠;

Physical層

負(fù)責(zé)Ordered-Set包的封裝與解封裝,物理層處理TLPs、DLLPs、Ordered-Set三種類(lèi)型的包傳輸;

數(shù)據(jù)包的封裝與解封裝,與網(wǎng)絡(luò)包的創(chuàng)建與解析很類(lèi)似,如下圖:

封裝的時(shí)候,在Payload數(shù)據(jù)前添加各種包頭,解析時(shí)是一個(gè)逆向的過(guò)程;

來(lái)一個(gè)更詳細(xì)的PCIe分層圖:

3.3 PCIe設(shè)備的配置空間

為了兼容PCI軟件,PCIe保留了256Byte的配置空間,如下圖:

此外,在這個(gè)基礎(chǔ)上將配置空間擴(kuò)展到了4KB,還進(jìn)行了功能的擴(kuò)展,比如Capability、Power Management、MSI中斷等:

擴(kuò)展后的區(qū)域?qū)⑹褂肕MIO的方式進(jìn)行訪(fǎng)問(wèn);

草草收?qǐng)霭桑瑢?duì)PCI和PCIe有一些輪廓上的認(rèn)知了,可以開(kāi)始Source Code的軟件分析了,欲知詳情、下回分解!

Linux PCI驅(qū)動(dòng)框架分析(二)

1. 概述

本文將分析Linux PCI子系統(tǒng)的框架,主要圍繞Linux PCI子系統(tǒng)的初始化以及枚舉過(guò)程分析;

如果對(duì)具體的硬件缺乏了解,建議先閱讀上篇文章《Linux PCI驅(qū)動(dòng)框架分析(一)》;

話(huà)不多說(shuō),直接開(kāi)始。

2. 數(shù)據(jù)結(jié)構(gòu)

PCI體系結(jié)構(gòu)的拓?fù)潢P(guān)系如圖所示,而圖中的不同數(shù)據(jù)結(jié)構(gòu)就是用于來(lái)描述對(duì)應(yīng)的模塊;

Host Bridge連接CPU和PCI系統(tǒng),由struct pci_host_bridge描述;

struct pci_dev描述PCI設(shè)備,以及PCI-to-PCI橋設(shè)備;

struct pci_bus用于描述PCI總線(xiàn),struct pci_slot用于描述總線(xiàn)上的物理插槽;

來(lái)一張更詳細(xì)的結(jié)構(gòu)體組織圖:

總體來(lái)看,數(shù)據(jù)結(jié)構(gòu)對(duì)硬件模塊進(jìn)行了抽象,數(shù)據(jù)結(jié)構(gòu)之間也能很便捷的構(gòu)建一個(gè)類(lèi)似PCI子系統(tǒng)物理拓?fù)涞年P(guān)系圖;

頂層的結(jié)構(gòu)為pci_host_bridge,這個(gè)結(jié)構(gòu)一般由Host驅(qū)動(dòng)負(fù)責(zé)來(lái)初始化創(chuàng)建;

pci_host_bridge指向root bus,也就是編號(hào)為0的總線(xiàn),在該總線(xiàn)下,可以?huà)旖痈鞣N外設(shè)或物理slot,也可以通過(guò)PCI橋去擴(kuò)展總線(xiàn);

3. 流程分析

3.1 設(shè)備驅(qū)動(dòng)模型

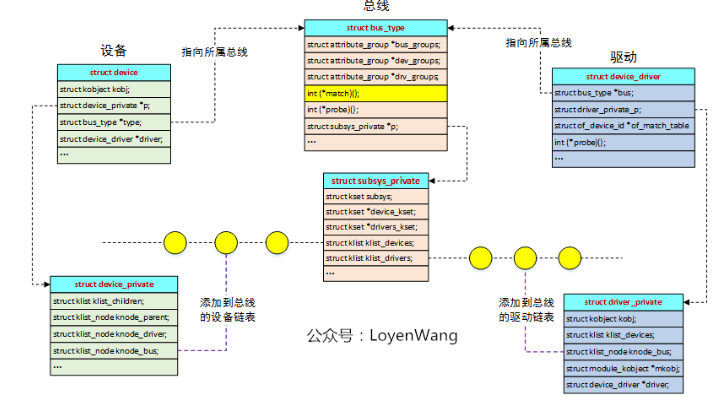

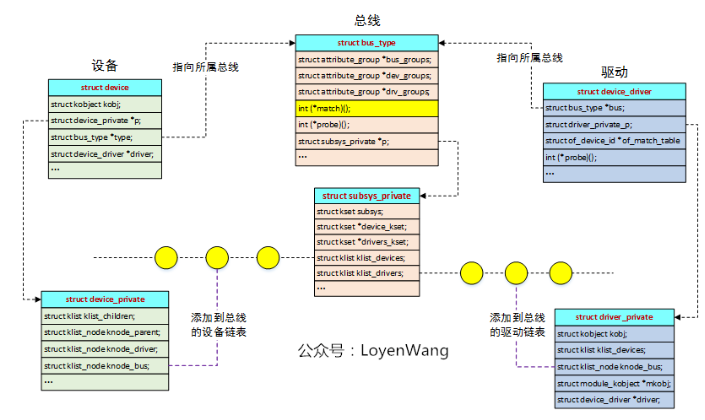

Linux PCI驅(qū)動(dòng)框架,基于Linux設(shè)備驅(qū)動(dòng)模型,因此有必要先簡(jiǎn)要介紹一下,實(shí)際上Linux設(shè)備驅(qū)動(dòng)模型也是一個(gè)大的topic,先挖個(gè)坑,有空再來(lái)填。來(lái)張圖吧:

簡(jiǎn)單來(lái)說(shuō),Linux內(nèi)核建立了一個(gè)統(tǒng)一的設(shè)備模型,分別采用總線(xiàn)、設(shè)備、驅(qū)動(dòng)三者進(jìn)行抽象,其中設(shè)備與驅(qū)動(dòng)都掛在總線(xiàn)上,當(dāng)有新的設(shè)備注冊(cè)或者新的驅(qū)動(dòng)注冊(cè)時(shí),總線(xiàn)會(huì)去進(jìn)行匹配操作(match函數(shù)),當(dāng)發(fā)現(xiàn)驅(qū)動(dòng)與設(shè)備能進(jìn)行匹配時(shí),就會(huì)執(zhí)行probe函數(shù)的操作;

從數(shù)據(jù)結(jié)構(gòu)中可以看出,bus_type會(huì)維護(hù)兩個(gè)鏈表,分別用于掛接向其注冊(cè)的設(shè)備和驅(qū)動(dòng),而match函數(shù)就負(fù)責(zé)匹配檢測(cè);

各類(lèi)驅(qū)動(dòng)框架也都是基于圖中的機(jī)制來(lái)實(shí)現(xiàn),在這之上進(jìn)行封裝,比如I2C總線(xiàn)框架等;

設(shè)備驅(qū)動(dòng)模型中,包含了很多kset/kobject等內(nèi)容,建議去看看之前的文章《linux設(shè)備模型之kset/kobj/ktype分析》

好了,點(diǎn)到為止,感覺(jué)要跑題了,強(qiáng)行拉回來(lái)。

3.2 初始化

既然說(shuō)到了設(shè)備驅(qū)動(dòng)模型,那么首先我們要做的事情,就是先在內(nèi)核里邊創(chuàng)建一個(gè)PCI總線(xiàn),用于掛接PCI設(shè)備和PCI驅(qū)動(dòng),我們的實(shí)現(xiàn)來(lái)到了pci_driver_init()函數(shù):

內(nèi)核在PCI框架初始化時(shí)會(huì)調(diào)用pci_driver_init()來(lái)創(chuàng)建一個(gè)PCI總線(xiàn)結(jié)構(gòu)(全局變量pci_bus_type),這里描述的PCI總線(xiàn)結(jié)構(gòu),是指驅(qū)動(dòng)匹配模型中的概念,PCI的設(shè)備和驅(qū)動(dòng)都會(huì)掛在該P(yáng)CI總線(xiàn)上;

從pci_bus_type的函數(shù)操作接口也能看出來(lái),pci_bus_match用來(lái)檢查設(shè)備與驅(qū)動(dòng)是否匹配,一旦匹配了就會(huì)調(diào)用pci_device_probe函數(shù),下邊針對(duì)這兩個(gè)函數(shù)稍加介紹;

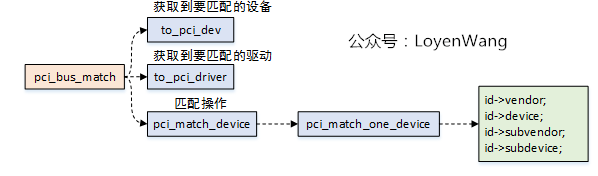

3.2.1 pci_bus_match

設(shè)備或者驅(qū)動(dòng)注冊(cè)后,觸發(fā)pci_bus_match函數(shù)的調(diào)用,實(shí)際會(huì)去比對(duì)vendor和device等信息,這個(gè)都是廠(chǎng)家固化的,在驅(qū)動(dòng)中設(shè)置成PCI_ANY_ID就能支持所有設(shè)備;

一旦匹配成功后,就會(huì)去觸發(fā)pci_device_probe的執(zhí)行;

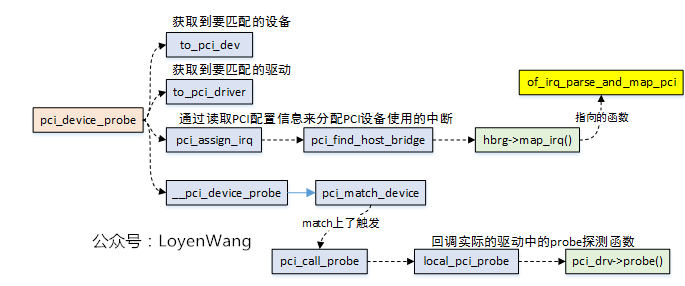

3.2.2 pci_device_probe

實(shí)際的過(guò)程也是比較簡(jiǎn)單,無(wú)非就是進(jìn)行匹配,一旦匹配上了,直接調(diào)用驅(qū)動(dòng)程序的probe函數(shù),寫(xiě)過(guò)驅(qū)動(dòng)的同學(xué)應(yīng)該就比較清楚后邊的流程了;

3.3 枚舉

我們還是順著設(shè)備驅(qū)動(dòng)匹配的思路繼續(xù)開(kāi)展;

3.2節(jié)描述的是總線(xiàn)的創(chuàng)建,那么本節(jié)中的枚舉,顯然就是設(shè)備的創(chuàng)建了;

所謂設(shè)備的創(chuàng)建,就是在Linux內(nèi)核中維護(hù)一些數(shù)據(jù)結(jié)構(gòu)來(lái)對(duì)硬件設(shè)備進(jìn)行描述,而硬件的描述又跟上文中的數(shù)據(jù)結(jié)構(gòu)能對(duì)應(yīng)上;

枚舉的入口函數(shù):pci_host_probe

設(shè)備的掃描從pci_scan_root_bus_bridge開(kāi)始,首先需要先向系統(tǒng)注冊(cè)一個(gè)host bridge,在注冊(cè)的過(guò)程中需要?jiǎng)?chuàng)建一個(gè)root bus,也就是bus 0,在pci_register_host_bridge函數(shù)中,主要是一系列的初始化和注冊(cè)工作,此外還為總線(xiàn)分配資源,包括地址空間等;

pci_scan_child_bus開(kāi)始,從bus 0向下掃描并添加設(shè)備,這個(gè)過(guò)程由pci_scan_child_bus_extend來(lái)完成;

從pci_scan_child_bus_extend的流程可以看出,主要有兩大塊:

PCI設(shè)備掃描,從循環(huán)也能看出來(lái),每條總線(xiàn)支持32個(gè)設(shè)備,每個(gè)設(shè)備支持8個(gè)功能,掃描完設(shè)備后將設(shè)備注冊(cè)進(jìn)系統(tǒng),pci_scan_device的過(guò)程中會(huì)去讀取PCI設(shè)備的配置空間,獲取到BAR的相關(guān)信息,細(xì)節(jié)不表了;

PCI橋設(shè)備掃描,PCI橋是用于連接上一級(jí)PCI總線(xiàn)和下一級(jí)PCI總線(xiàn)的,當(dāng)發(fā)現(xiàn)有下一級(jí)總線(xiàn)時(shí),創(chuàng)建子結(jié)構(gòu),并再次調(diào)用pci_scan_child_bus_extend的函數(shù)來(lái)掃描下一級(jí)的總線(xiàn),從這個(gè)過(guò)程看,就是一個(gè)遞歸過(guò)程。

從設(shè)備的掃描過(guò)程看,這是一個(gè)典型的DFS(Depth First Search)過(guò)程,熟悉數(shù)據(jù)結(jié)構(gòu)與算法的同學(xué)應(yīng)該清楚,這就類(lèi)似典型的走迷宮的過(guò)程;

如果你對(duì)上述的流程還不清楚,再來(lái)一張圖:

圖中的數(shù)字代表的就是掃描的過(guò)程,當(dāng)遍歷到PCI橋設(shè)備的時(shí)候,會(huì)一直窮究到底,然后再返回來(lái);

當(dāng)枚舉過(guò)程結(jié)束后,系統(tǒng)中就已經(jīng)維護(hù)了PCI設(shè)備的各類(lèi)信息了,在設(shè)備驅(qū)動(dòng)匹配模型中,總線(xiàn)和設(shè)備都已經(jīng)具備了,剩下的就是寫(xiě)個(gè)驅(qū)動(dòng)了;

暫且寫(xiě)這么多,細(xì)節(jié)方面不再贅述了,把握大體的框架即可,無(wú)法扼住PCI的咽喉,那就扼住它的骨架吧。

Linux PCI驅(qū)動(dòng)框架分析(三)

1. 概述

先回顧一下PCIe的架構(gòu)圖:

本文將講PCIe Host的驅(qū)動(dòng),對(duì)應(yīng)為Root Complex部分,相當(dāng)于PCI的Host Bridge部分;

本文會(huì)選擇Xilinx的nwl-pcie來(lái)進(jìn)行分析;

驅(qū)動(dòng)的編寫(xiě)整體偏簡(jiǎn)單,往現(xiàn)有的框架上套就可以了,因此不會(huì)花太多筆墨,點(diǎn)到為止;

2. 流程分析

但凡涉及到驅(qū)動(dòng)的分析,都離不開(kāi)驅(qū)動(dòng)模型的介紹,驅(qū)動(dòng)模型的實(shí)現(xiàn)讓具體的驅(qū)動(dòng)開(kāi)發(fā)變得更容易;

所以,還是回顧一下上篇文章提到的驅(qū)動(dòng)模型:Linux內(nèi)核建立了一個(gè)統(tǒng)一的設(shè)備模型,分別采用總線(xiàn)、設(shè)備、驅(qū)動(dòng)三者進(jìn)行抽象,其中設(shè)備與驅(qū)動(dòng)都掛在總線(xiàn)上,當(dāng)有新的設(shè)備注冊(cè)或者新的驅(qū)動(dòng)注冊(cè)時(shí),總線(xiàn)會(huì)去進(jìn)行匹配操作(match函數(shù)),當(dāng)發(fā)現(xiàn)驅(qū)動(dòng)與設(shè)備能進(jìn)行匹配時(shí),就會(huì)執(zhí)行probe函數(shù)的操作;

《Linux PCI驅(qū)動(dòng)框架分析(二)》中提到過(guò)PCI設(shè)備、PCI總線(xiàn)和PCI驅(qū)動(dòng)的創(chuàng)建,PCI設(shè)備和PCI驅(qū)動(dòng)掛接在PCI總線(xiàn)上,這個(gè)理解很直觀(guān)。針對(duì)PCIe的控制器來(lái)說(shuō),同樣遵循設(shè)備、總線(xiàn)、驅(qū)動(dòng)的匹配模型,不過(guò)這里的總線(xiàn)是由虛擬總線(xiàn)platform總線(xiàn)來(lái)替代,相應(yīng)的設(shè)備和驅(qū)動(dòng)分別為platform_device和platform_driver;

那么問(wèn)題來(lái)了,platform_device是在什么時(shí)候創(chuàng)建的呢?那就不得不提到Device Tree設(shè)備樹(shù)了。

2.1 Device Tree

設(shè)備樹(shù)用于描述硬件的信息,包含節(jié)點(diǎn)各類(lèi)屬性,在dts文件中定義,最終會(huì)被編譯成dtb文件加載到內(nèi)存中;

內(nèi)核會(huì)在啟動(dòng)過(guò)程中去解析dtb文件,解析成device_node描述的Device Tree;

根據(jù)device_node節(jié)點(diǎn),創(chuàng)建platform_device結(jié)構(gòu),并最終注冊(cè)進(jìn)系統(tǒng),這個(gè)也就是PCIe Host設(shè)備的創(chuàng)建過(guò)程;

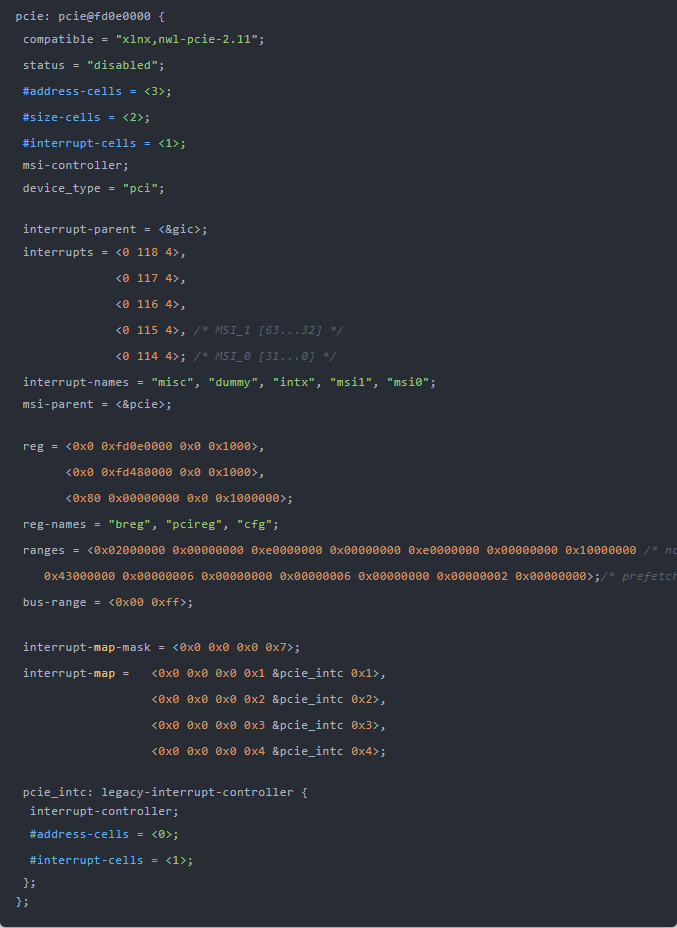

我們看看PCIe Host的設(shè)備樹(shù)內(nèi)容:

關(guān)鍵字段描述如下:

compatible:用于匹配PCIe Host驅(qū)動(dòng);

msi-controller:表示是一個(gè)MSI(Message Signaled Interrupt)控制器節(jié)點(diǎn),這里需要注意的是,有的SoC中斷控制器使用的是GICv2版本,而GICv2并不支持MSI,所以會(huì)導(dǎo)致該功能的缺失;

device-type:必須是"pci";

interrupts:包含NWL PCIe控制器的中斷號(hào);

interrupts-name:msi1, msi0用于MSI中斷,intx用于舊式中斷,與interrupts中的中斷號(hào)對(duì)應(yīng);

reg:包含用于訪(fǎng)問(wèn)PCIe控制器操作的寄存器物理地址和大小;

reg-name:分別表示Bridge registers,PCIe Controller registers, Configuration space region,與reg中的值對(duì)應(yīng);

ranges:PCIe地址空間轉(zhuǎn)換到CPU的地址空間中的范圍;

bus-range:PCIe總線(xiàn)的起始范圍;

interrupt-map-mask和interrupt-map:標(biāo)準(zhǔn)PCI屬性,用于定義PCI接口到中斷號(hào)的映射;

legacy-interrupt-controller:舊式的中斷控制器;

2.2 probe流程

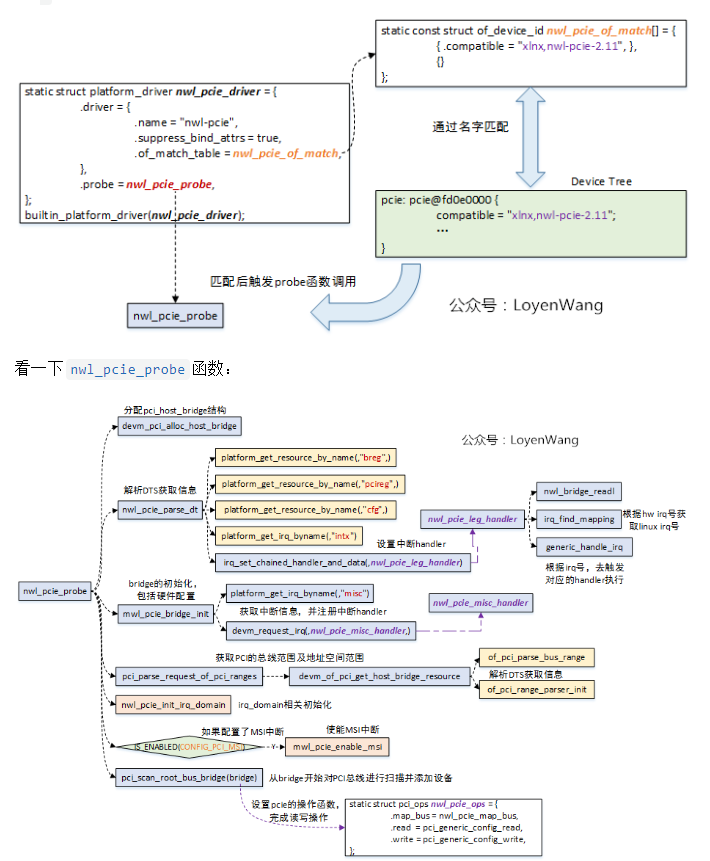

系統(tǒng)會(huì)根據(jù)dtb文件創(chuàng)建對(duì)應(yīng)的platform_device并進(jìn)行注冊(cè);

當(dāng)驅(qū)動(dòng)與設(shè)備通過(guò)compatible字段匹配上后,會(huì)調(diào)用probe函數(shù),也就是nwl_pcie_probe;

通常probe函數(shù)都是進(jìn)行一些初始化操作和注冊(cè)操作:

初始化包括:數(shù)據(jù)結(jié)構(gòu)的初始化以及設(shè)備的初始化等,設(shè)備的初始化則需要獲取硬件的信息(比如寄存器基地址,長(zhǎng)度,中斷號(hào)等),這些信息都從DTS而來(lái);

注冊(cè)操作主要是包含中斷處理函數(shù)的注冊(cè),以及通常的設(shè)備文件注冊(cè)等;

針對(duì)PCI控制器的驅(qū)動(dòng),核心的流程是需要分配并初始化一個(gè)pci_host_bridge結(jié)構(gòu),最終通過(guò)這個(gè)bridge去枚舉PCI總線(xiàn)上的所有設(shè)備;

devm_pci_alloc_host_bridge:分配并初始化一個(gè)基礎(chǔ)的pci_hsot_bridge結(jié)構(gòu);

nwl_pcie_parse_dt:獲取DTS中的寄存器信息及中斷信息,并通過(guò)irq_set_chained_handler_and_data設(shè)置intx中斷號(hào)對(duì)應(yīng)的中斷處理函數(shù),該處理函數(shù)用于中斷的級(jí)聯(lián);

nwl_pcie_bridge_init:硬件的Controller一堆設(shè)置,這部分需要去查閱Spec,了解硬件工作的細(xì)節(jié)。此外,通過(guò)devm_request_irq注冊(cè)misc中斷號(hào)對(duì)應(yīng)的中斷處理函數(shù),該處理函數(shù)用于控制器自身狀態(tài)的處理;

pci_parse_request_of_pci_ranges:用于解析PCI總線(xiàn)的總線(xiàn)范圍和總線(xiàn)上的地址范圍,也就是CPU能看到的地址區(qū)域;

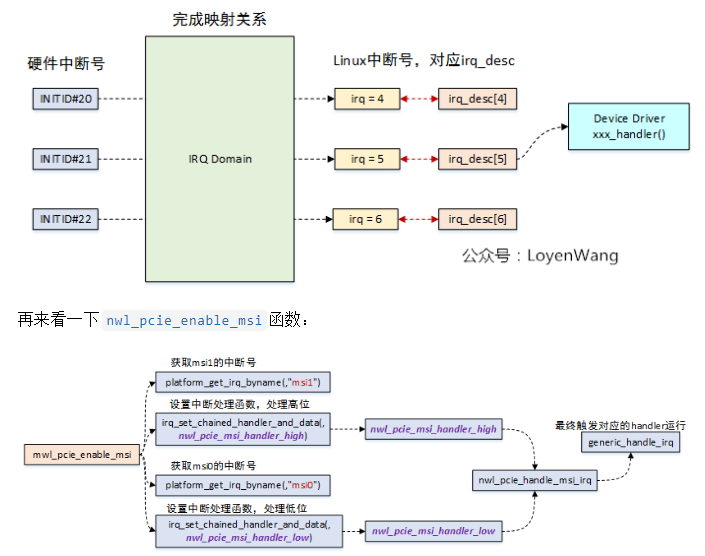

nwl_pcie_init_irq_domain和mwl_pcie_enable_msi與中斷級(jí)聯(lián)相關(guān),下個(gè)小節(jié)介紹;

pci_scan_root_bus_bridge:對(duì)總線(xiàn)上的設(shè)備進(jìn)行掃描枚舉,這個(gè)流程在Linux PCI驅(qū)動(dòng)框架分析(二)中分析過(guò)。brdige結(jié)構(gòu)體中的pci_ops字段,用于指向PCI的讀寫(xiě)操作函數(shù)集,當(dāng)具體掃描到設(shè)備要讀寫(xiě)配置空間時(shí),調(diào)用的就是這個(gè)函數(shù),由具體的Controller驅(qū)動(dòng)實(shí)現(xiàn);

2.3 中斷處理

PCIe控制器,通過(guò)PCIe總線(xiàn)連接各種設(shè)備,因此它本身充當(dāng)一個(gè)中斷控制器,級(jí)聯(lián)到上一層的中斷控制器(比如GIC),如下圖:

PCIe總線(xiàn)支持兩種中斷的處理方式:

Legacy Interrupt:總線(xiàn)提供INTA#, INTB#, INTC#, INTD#四根中斷信號(hào),PCI設(shè)備借助這四根信號(hào)使用電平觸發(fā)方式提交中斷請(qǐng)求;

MSI(Message Signaled Interrupt) Interrupt:基于消息機(jī)制的中斷,也就是往一個(gè)指定地址寫(xiě)入特定消息,從而觸發(fā)一個(gè)中斷;

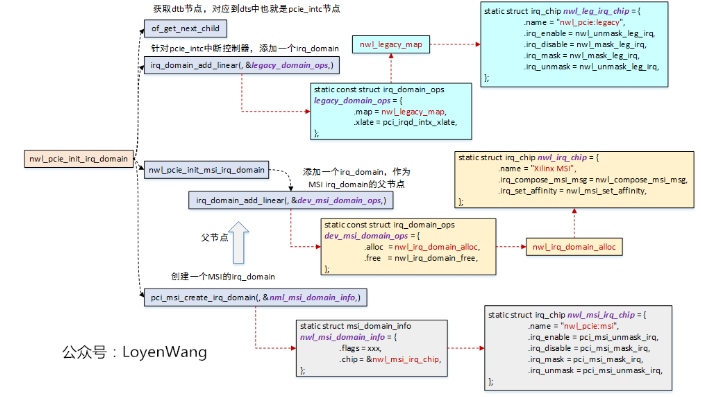

針對(duì)兩種處理方式,NWL PCIe驅(qū)動(dòng)中,實(shí)現(xiàn)了兩個(gè)irq_chip,也就是兩種方式的中斷控制器:

irq_domain對(duì)應(yīng)一個(gè)中斷控制器(irq_chip),irq_domain負(fù)責(zé)將硬件中斷號(hào)映射到虛擬中斷號(hào)上;

來(lái)一張舊圖吧,具體文章可以去參考中斷子系統(tǒng)相關(guān)文章;

在該函數(shù)中主要完成的工作就是設(shè)置級(jí)聯(lián)的中斷處理函數(shù),級(jí)聯(lián)的中斷處理函數(shù)中最終會(huì)去調(diào)用具體的設(shè)備的中斷處理函數(shù);

所以,稍微匯總一下,作為兩種不同的中斷處理方式,套路都是一樣的,都是創(chuàng)建irq_chip中斷控制器,為該中斷控制器添加irq_domain,具體設(shè)備的中斷響應(yīng)流程如下:

設(shè)備連接在PCI總線(xiàn)上,觸發(fā)中斷時(shí),通過(guò)PCIe控制器充當(dāng)?shù)闹袛嗫刂破髀酚傻缴弦患?jí)控制器,最終路由到CPU;

CPU在處理PCIe控制器的中斷時(shí),調(diào)用它的中斷處理函數(shù),也就是上文中提到過(guò)的nwl_pcie_leg_handler,nwl_pcie_msi_handler_high,和nwl_pcie_leg_handler_low;

在級(jí)聯(lián)的中斷處理函數(shù)中,調(diào)用chained_irq_enter進(jìn)入中斷級(jí)聯(lián)處理;

調(diào)用irq_find_mapping找到具體的PCIe設(shè)備的中斷號(hào);

調(diào)用generic_handle_irq觸發(fā)具體的PCIe設(shè)備的中斷處理函數(shù)執(zhí)行;

調(diào)用chained_irq_exit退出中斷級(jí)聯(lián)的處理;

2.4 總結(jié)

PCIe控制器驅(qū)動(dòng),各家的IP實(shí)現(xiàn)不一樣,驅(qū)動(dòng)的差異可能會(huì)很大,單獨(dú)分析一個(gè)驅(qū)動(dòng)畢竟只是個(gè)例,應(yīng)該去掌握背后的通用框架;

各類(lèi)驅(qū)動(dòng),大體都是硬件初始化配置,資源申請(qǐng)注冊(cè),核心是處理與硬件的交互(一般就是中斷的處理),如果需要用戶(hù)來(lái)交互的,則還需要注冊(cè)設(shè)備文件,實(shí)現(xiàn)一堆file_operation操作函數(shù)集;

好吧,我個(gè)人不太喜歡分析某個(gè)驅(qū)動(dòng),草草收?qǐng)隽耍?/p>