概述

Super-junction類型的高壓功率MOSFET具有更低的導(dǎo)通電阻,,因此在通信電源,服務(wù)器電源,,電源適配器以及臺(tái)式電腦電源和照明整流器等應(yīng)用中得到廣泛的使用,。Alpha MOS就是基于Super-junction技術(shù)開發(fā)的高壓功率MOSFET,,其采用8英寸晶圓,明顯提升了器件性能和可靠性,。

本文主要針對(duì)Alpha MOS在主動(dòng)功率因素校正電路(PFC)中的設(shè)計(jì)要點(diǎn)和注意事項(xiàng)給出建議和解決方案,。

1.Alpha MOS的工作特性

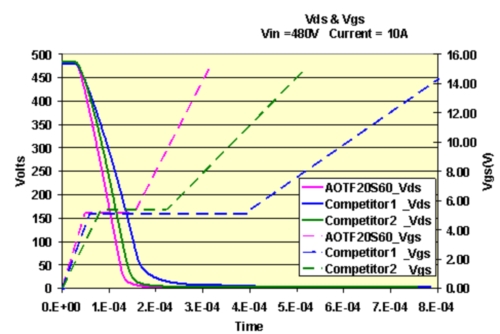

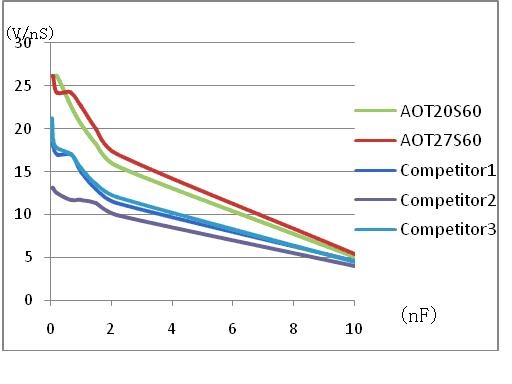

Alpha MOS的導(dǎo)通電阻x芯片面積(RdsA)性能指標(biāo)比AOS平面工藝MOSFET高3.5倍,導(dǎo)通電阻x米勒電容(RdsxQgd)性能比平面工藝MOSFET高5.7倍,。Alpha MOS是目前super-junction產(chǎn)品中同等級(jí)下FOM性能最高的,,比同等級(jí)排名第二的高速開關(guān)型super-junction 產(chǎn)品高出45%(圖1)。

圖1:RdsxQgd和FOM(RdsxQg)的性能對(duì)比

由于Alpha MOS 具有開關(guān)速度快,,結(jié)電容小的特點(diǎn),,對(duì)減少開關(guān)損耗,提高效率有很大幫助,。但是在設(shè)計(jì)中需要更謹(jǐn)慎小心,。與傳統(tǒng)的MOSFET相比,Alpha MOS需要更仔細(xì)的設(shè)計(jì)驅(qū)動(dòng)電路和PCB布線,,在并聯(lián)應(yīng)用中也需要格外注意開關(guān)噪聲對(duì)驅(qū)動(dòng)信號(hào)的影響,。

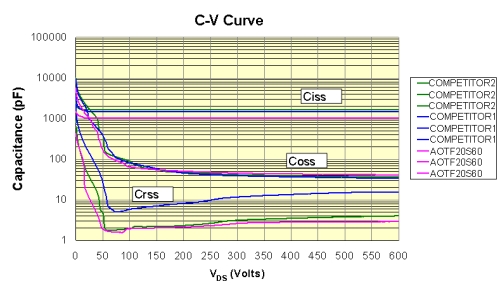

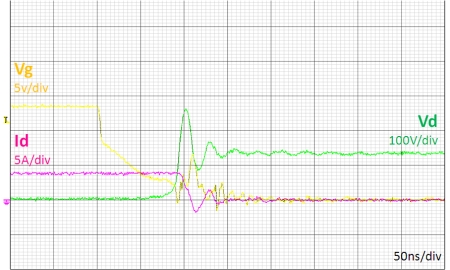

Super-junction類型的MOSFET由于其特有的空間電荷結(jié)構(gòu),開關(guān)速度比傳統(tǒng)MOSFET快的多,。圖2-圖5是600V/20A等級(jí)super-junction 產(chǎn)品的開關(guān)特性對(duì)比。competitor1為電源類產(chǎn)品應(yīng)用最廣泛的一種super-junction型 MOSFET,,competitor2則是另一種高速開關(guān)型的super-junction MOSFET,。

圖2:門極驅(qū)動(dòng)電荷對(duì)比

圖3:漏極電流與門極驅(qū)動(dòng)關(guān)系對(duì)比

圖4:漏極電壓與門極驅(qū)動(dòng)關(guān)系對(duì)比

圖5:結(jié)電容與漏極電壓關(guān)系對(duì)比

從對(duì)比中可以看出Alpha MOS主要的優(yōu)勢(shì)在結(jié)電容,同等級(jí)的MOSFET結(jié)電容越小,,在同樣驅(qū)動(dòng)條件下開關(guān)速度就越快,,在硬開關(guān)電路中,這是一個(gè)很大的優(yōu)勢(shì),。但是過(guò)快的開關(guān)速度會(huì)產(chǎn)生很高的dv/dt和di/dt,,這對(duì)于MOS的工作可靠性是有害的,同時(shí)也是電源系統(tǒng)中噪聲的來(lái)源,。

Alpha MOS的Qg很小,,對(duì)于減少驅(qū)動(dòng)損耗是個(gè)優(yōu)點(diǎn),。在實(shí)際應(yīng)用中,Qg或者Ciss小的MOSFET,,它的驅(qū)動(dòng)信號(hào)更容易受主功率回路的干擾,,特別在高壓應(yīng)用中這個(gè)問(wèn)題十分突出。如果對(duì)開關(guān)速度不加限制,,過(guò)高的dv/dt 很容易耦合到驅(qū)動(dòng)回路中,,造成驅(qū)動(dòng)信號(hào)紊亂,甚至導(dǎo)致MOS燒毀,。

在大功率應(yīng)用中,,MOS的并聯(lián)往往是常用的手段。但是對(duì)于像Alpha MOS這樣的高速開關(guān)器件,,并聯(lián)需要格外注意,。開關(guān)速度越快的MOS,并聯(lián)時(shí)越容易導(dǎo)致工作不平衡,,驅(qū)動(dòng)參數(shù)選擇不當(dāng)甚至?xí)?dǎo)致額外的干擾,。

可以看出,Alpha MOS雖然性能優(yōu)異但是對(duì)設(shè)計(jì)使用的要求也比較高,。它并非如傳統(tǒng)的開關(guān)器件可以“拿來(lái)就用”,。選擇合適的拓?fù)洌屑?xì)調(diào)節(jié)驅(qū)動(dòng)參數(shù),,合理規(guī)劃PCB布局,,都有助于增加電路的穩(wěn)定性,避免不必要的重復(fù)勞動(dòng),。

2.Alpha MOS驅(qū)動(dòng)電路設(shè)計(jì)

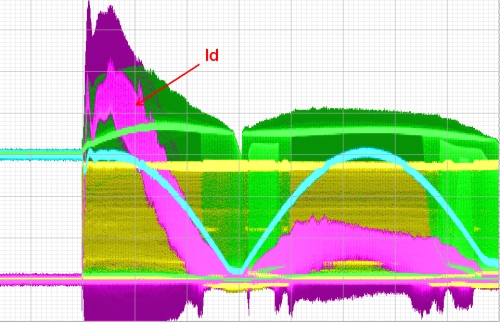

PFC是電源拓?fù)渲袑?duì)MOS要求比較高的拓?fù)渲?,這是因?yàn)椋海?)PFC有比較寬的輸入電壓范圍。現(xiàn)代電源大都要求在90-264V的全范圍交流電壓下工作,,這意味著MOS既要有足夠的耐壓等級(jí)又要能承受較大電流,;(2)PFC的控制環(huán)路速度比較慢,為了平滑100Hz/120Hz的交流整流紋波,,PFC反應(yīng)時(shí)間必須達(dá)到數(shù)十ms,。如果控制電路和IC沒(méi)有專門進(jìn)行優(yōu)化,啟動(dòng)過(guò)程往往會(huì)產(chǎn)生很大的沖擊電流,,沖擊電流可達(dá)正常工作時(shí)的5-10倍,;(3)在缺乏欠壓保護(hù)的PFC中,當(dāng)交流電壓降到低于90V很多時(shí),,電路仍有可能繼續(xù)工作,,這也會(huì)產(chǎn)生很高的開關(guān)峰值電流,導(dǎo)致干擾和應(yīng)力超出正常范圍,。圖6為典型的PFC電路,,圖7為PFC啟動(dòng)時(shí),,MOSFET漏極的沖擊電流示意圖。

圖6:典型的PFC電路

圖7:PFC啟動(dòng),,MOSFET漏極的沖擊電流

MOSFET的驅(qū)動(dòng)電路已經(jīng)有很多成熟的方案。在實(shí)際應(yīng)用中,,出于成本考慮,,很多驅(qū)動(dòng)電路都采用比較簡(jiǎn)單的芯片直驅(qū)方案。但是在大功率和性能要求比較高的應(yīng)用中,,驅(qū)動(dòng)電路的設(shè)計(jì)對(duì)MOSFET的可靠性和系統(tǒng)的性能仍有很大影響,。

圖8:MOSFET兩種基本驅(qū)動(dòng)電路結(jié)構(gòu)

在圖8中是最常見的MOSFET驅(qū)動(dòng)電路,R1,,R2是Rg,,左圖R1+R2是驅(qū)動(dòng)電壓上升時(shí)的充電電阻,R1單獨(dú)作為放電電阻,,右圖R2單獨(dú)作為充電電阻,,R1和R2并聯(lián)作為放電電阻。R3是驅(qū)動(dòng)自放電電阻,。C1和C2分別是外加的Cds和Cgs電容,。

(1)dv/dt的控制策略和注意事項(xiàng)

影響dv/dt的因素有MOS自身特性、開關(guān)時(shí)的電流峰值,,以及驅(qū)動(dòng)電路的Rg等,。由于Alpha MOS的Ciss特別小,適當(dāng)?shù)脑龃驝gs也是有效改善dv/dt的方法,。

雖然MOSFET本身可承受的dv/dt和di/dt很高,,但是根據(jù)經(jīng)驗(yàn)數(shù)據(jù)表明,通過(guò)改變Rg和Cgs,,控制dv/dt不超過(guò)20V/ns,,對(duì)應(yīng)的di/dt不超過(guò)200A/ns,在實(shí)際電路中能有較好的工作狀態(tài),。在效率允許的情況下,,dv/dt小于10V/ns,di/dt小于100A/ns更有利于可靠性,,如圖9和圖10所示。

PFC應(yīng)用中存在寬輸入電壓范圍,,輸入電壓跳變,,以及響應(yīng)時(shí)間慢等特點(diǎn),容易出現(xiàn)比較大的沖擊電流,。在這種應(yīng)用中需要特別注意控制峰值電流,,同樣的驅(qū)動(dòng)參數(shù)下,,峰值電流越大,開關(guān)的dv/dt和di/dt越大,。要根據(jù)實(shí)際應(yīng)用中的最大峰值電流來(lái)調(diào)整驅(qū)動(dòng)參數(shù),。在設(shè)計(jì)中,要監(jiān)測(cè)最大沖擊電流下的開關(guān)波形,,以確定是否需要調(diào)整驅(qū)動(dòng)參數(shù),,使MOSFET工作在較好的狀態(tài)。

通過(guò)漏源極增加額外的電容也可以比較容易地減小dv/dt,。在正激有源拑位,,橋式軟開關(guān),諧振類電路中,,合適的漏源極電容有助于開關(guān)狀態(tài)的優(yōu)化,。而在PFC和反激類電路中則需要小心處理,要和效率進(jìn)行適當(dāng)?shù)钠胶?。在效率允許的范圍內(nèi),,通過(guò)增大漏源極電容還可以有效地減少EMI。

圖9:MOSFET關(guān)斷dv/dt與放電電阻關(guān)系

圖10:MOSFET關(guān)斷dv/dt與Cgs關(guān)系

(2)減少通過(guò)Cgd耦合對(duì)驅(qū)動(dòng)的干擾

由于Alpha MOS的高速開關(guān)特性,,以及極低的Ciss和Crss,,Alpha MOS更容易受layout不良而導(dǎo)致驅(qū)動(dòng)受到干擾。這種干擾往往是由于高頻高壓的走線和驅(qū)動(dòng)走線靠的太近,。使得漏極的高dv/dt信號(hào)通過(guò)耦合放大的Cgd進(jìn)入驅(qū)動(dòng)信號(hào),。如圖11和圖12所示。

圖11:PFC MOSFET驅(qū)動(dòng)被干擾

圖12:PFC MOSFET驅(qū)動(dòng)正常

(3)驅(qū)動(dòng)端加磁珠

驅(qū)動(dòng)端加磁珠是種簡(jiǎn)單合理的方法,,可以抑制驅(qū)動(dòng)端受干擾產(chǎn)生的尖刺,。建議將磁珠放置在盡可能靠近MOS驅(qū)動(dòng)端的位置。TO220等插件封裝可以采用套管式磁珠,,貼片封裝的MOS可以采用類似貼片電阻大小的SMD磁珠,。選取磁珠需要查閱其數(shù)據(jù)手冊(cè),確??梢酝ㄟ^(guò)至少3A的電流,,其峰值抑制頻率應(yīng)在30-100MHz。通常情況下磁珠并不會(huì)對(duì)驅(qū)動(dòng)波形產(chǎn)生影響,,當(dāng)MOS上流過(guò)很大電流導(dǎo)致干擾突然增大時(shí),,磁珠才起作用。

(4)合理放置驅(qū)動(dòng)元器件的位置

對(duì)于有圖騰柱驅(qū)動(dòng)或者三極管輔助放電的驅(qū)動(dòng)電路,,起到輔助和增強(qiáng)作用的電路元件要盡可能靠近MOS,。特別是地線,要直接單點(diǎn)與MOS的源級(jí)連接,,一定要盡量避免在驅(qū)動(dòng)的地線回路上有主功率部分的電流通過(guò),,否則,,主功率回路中的大電流會(huì)耦合到驅(qū)動(dòng)回路中,造成驅(qū)動(dòng)的誤開通和誤關(guān)斷,??刂菩酒尿?qū)動(dòng)信號(hào)則要遠(yuǎn)離高壓高頻走線。由于芯片的地線往往遠(yuǎn)離MOS的源級(jí),,因此只有在小功率的應(yīng)用中采用芯片直接驅(qū)動(dòng),。較大功率或干擾信號(hào)強(qiáng)的應(yīng)用還是建議帶有驅(qū)動(dòng)增強(qiáng)的輔助驅(qū)動(dòng)電路。

3 Alpha MOS的并聯(lián)及PCB設(shè)計(jì)

對(duì)于MOS并聯(lián)的情況,,首先驅(qū)動(dòng)電路要盡可能隔離,。嚴(yán)禁直接將并聯(lián)MOS的驅(qū)動(dòng)端連在一起。由于MOS的漏極電感,,結(jié)電容以及門檻電壓等可能有差異,,直接將門極相連會(huì)使門極驅(qū)動(dòng)在開關(guān)過(guò)程產(chǎn)生振蕩,如圖13所示,,振蕩將在低電抗回路中發(fā)生,,嚴(yán)重時(shí)會(huì)導(dǎo)致MOS損壞。驅(qū)動(dòng)電阻增大可以對(duì)并聯(lián)振蕩起到衰減作用,,最好嚴(yán)格地隔離并聯(lián)驅(qū)動(dòng),。

圖13:直接并聯(lián)的驅(qū)動(dòng)干擾模型

圖14所示為常見的并聯(lián)方式,并聯(lián)的MOS分別通過(guò)驅(qū)動(dòng)電阻與圖騰柱電路相連,。但這種隔離還不夠徹底,,徹底隔離的方式如圖15電路所示,兩個(gè)MOS分別經(jīng)過(guò)各自獨(dú)立的驅(qū)動(dòng)電路驅(qū)動(dòng),,只在信號(hào)輸出端相連,。不管采用哪種驅(qū)動(dòng)方式,為了提高可靠性,,增大驅(qū)動(dòng)電阻,,降低dv/dt(比單管更低)都是必要的。

需要說(shuō)明的是,,在并聯(lián)應(yīng)用中,,驅(qū)動(dòng)受干擾的問(wèn)題要優(yōu)先于并聯(lián)的不平衡問(wèn)題。一般的電路中很難保證并聯(lián)的絕對(duì)平衡,。如果驅(qū)動(dòng)電路和PCB布局不能兼顧的情況下,,可以適當(dāng)犧牲一些平衡性,但驅(qū)動(dòng)的干擾必須被消除,。具體應(yīng)用中需要仔細(xì)權(quán)衡,。

圖14:常用并聯(lián)驅(qū)動(dòng)電路

圖15:完全隔離并聯(lián)驅(qū)動(dòng)電路

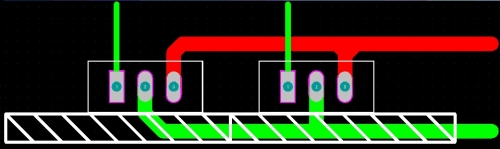

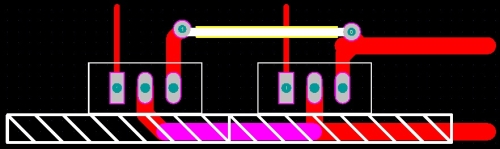

并聯(lián)中PCB布局和走線十分重要,越是高速開關(guān)的MOS,對(duì)并聯(lián)均衡的要求就越高,。不均衡的并聯(lián),不但會(huì)導(dǎo)致單個(gè)MOS承受過(guò)高的電流沖擊和dv/dt(注意到dv/dt與電流成正比)還會(huì)在電流重分配的過(guò)程中產(chǎn)生振蕩,,干擾驅(qū)動(dòng)和其他信號(hào),。下面是一些MOSFET并聯(lián)的例子,綠色為正面走線,,紅色為背面走線,。

圖16和圖17是最佳的并聯(lián)走線方式,并聯(lián)的MOS各自漏極和源級(jí)的走線長(zhǎng)度相同,,驅(qū)動(dòng)走線與主功率走線在不同方向,。實(shí)際應(yīng)用中可以增大走線面積以取得更好的效果。

圖16:并聯(lián)MOS散熱片獨(dú)立

圖17:并聯(lián)MOS散熱片共用(背靠背)

圖18的MOS布局方式在一些中小功率應(yīng)用中比較常見,,采用這種走線方式可以取得均衡的效果,,但是實(shí)際應(yīng)用要注意減少走線長(zhǎng)度以減小走線電感。

圖18:并聯(lián)MOS散熱片共用(并排)

圖19是一種不良走線方式,,左邊的MOS上串聯(lián)了一段走線電阻和電感,,這可能導(dǎo)致右邊MOS的工作電流更大,dv/dt和di/dt也更大

圖19:并聯(lián)MOS散熱片共用(并排),,不良走線

在一些中小功率的實(shí)際應(yīng)用中,PCB是單面板,,常常采用圖20的方式并聯(lián),。雖然這種方式仍然不能實(shí)現(xiàn)走線電感的均衡,但是通過(guò)走線露銅涂錫,,減少了電阻的不平衡,。

圖20:并聯(lián)MOS散熱片共用(并排),,單面板小功率

圖16和圖17的布局方式不是很容易實(shí)現(xiàn),,圖21是單面板PCB,并聯(lián)MOS在散熱片拐角處放置,,通過(guò)增加走線面積和露銅等方式,,可以在一定程度上減少不均衡問(wèn)題。

圖21:并聯(lián)MOS散熱片直角布局,,單面板

總結(jié)

Alpha MOS是AOS新一代高壓MOSFET產(chǎn)品,它具有導(dǎo)通電阻小,,開關(guān)速度快,,結(jié)電容小的特點(diǎn)。Alpha MOS在PFC的應(yīng)用需要特別謹(jǐn)慎,盡量通過(guò)增大Rg,,增加Cgs等方法控制dv/dt小于20V/ns,,并控制啟動(dòng)過(guò)程抑制沖擊電流。由于Alpha MOS的高速開關(guān)特性,,需要注意驅(qū)動(dòng)電路設(shè)計(jì)和PCB版布局,,盡量減少干擾,在并聯(lián)應(yīng)用中也需要采用獨(dú)立的驅(qū)動(dòng)電路和合理的PCB走線,。