隨著水下武器和水下航行器等水下目標的快速發(fā)展,對其進行定位和跟蹤從而檢驗其性能的試驗具有非常重要的意義,這也是水下目標試驗場的重要工作內容。水下試驗場的定位系統根據被測目標是否加裝合作聲信標,可以分為主動和被動兩種方式。主動定位方式需要在水下目標上加裝聲信標,定位系統整個試驗系統的同步時序控制下,通過接收及處理水下目標聲信標發(fā)射的已知脈沖信號來實現目標的定位及跟蹤;被動方式則僅通過接收及處理水下目標運動產生的輻射噪聲,實現水下目標的定位及跟蹤。對于水下目標定位系統的信號處理模塊而言,兩種定位方式的差異在于因系統的接收信號頻率及信號體制不同而導致的系統硬件規(guī)模和處理性能不同。

1 系統的硬件設計

對于主動定位系統.水下目標的合作聲信標發(fā)射的信號頻率可達100kHz,因此為了滿足工程應用所需的測量精度,信號處理模塊的采樣頻率應不小于500 kHz。但是由于主動定位系統是在統一的同步時序下工作的,因此每個處理模塊只要獲得接收信號相對同步信號的時延即可,也就是說,每個處理模塊只需進行一路接收信號與不同發(fā)射信號的時延估計。

而對于被動定位系統,目標輻射噪聲的頻率范圍主要位于100 Hz~2kHz,因此信號處理模塊的采樣頻率不小于10 kHz就可以滿足要求。但是由于被動定位系統沒有統一的同步時序,因此只能通過估計不同接收信號的相對時延來進行目標的方位估計,也就是說,每個處理模塊所需進行處理的接收信號不小于2個通道。

深入分析主/被動定位方法的信號體制及相應的處理方法可知,主動定位系統所需的信號處理模塊的硬件規(guī)模和性能要求較高,因此信號處理模塊的硬件設計以主動定位系統的性能指標為主、兼顧被動定位系統的指標要求。

1.1 模塊的硬件功能及組成

本文設計的數字信號處理模塊的主要技術指標包括:

1)輸入模擬信號:通道數為3路,信號幅度為-10~10 V,頻率為100Hz~30kHz;

2)通訊接口:RS422口及RS232接口各1個,自定義的通用IO口16位;

3)輸出模擬信號:通道數為2路,信號幅度為-10~10 V;

4)LCD顯示屏:彩色觸摸屏;

5)運算能力:實時進行水下目標定位。

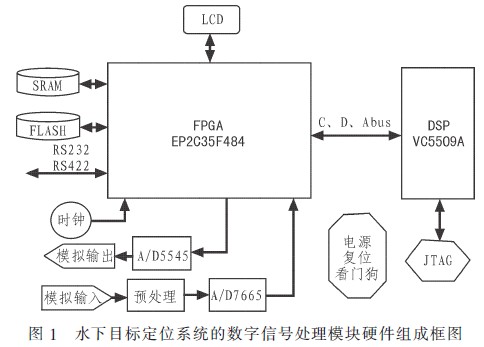

根據水下定位系統的功能需求和上述的指標要求,采用基于DSP+FPGA的硬件架構進行數字信號處理模塊的設計,如圖1所示。其中FPGA實現系統的時序控制、各種接口轉換、數字信號預處理(如FIR濾波、FFT運算),而DSP實現系統的副本相關或互相關、包絡檢波等信號處理任務;這樣既充分利用了FPGA的高度并行性和實時性,又充分使用了DSP的信號處理能力,使系統結構靈活、通用性強、運算能力強度,具有較好的工程應用參考價值。

1.2 硬件系統的主要器件選型

1.2.1 信號處理器

數字信號處理(Digital Signal Processing,DSP)的主要任務是完成水下目標的方位估計。因此選擇DSP時首先考慮它的運算能力,在滿足運算速度要求的前提下,要求DSP的功耗小、外圍電路設計簡單,軟件開發(fā)容易。目前可供選擇的DSP很多,包括TI公司的C2000系列、C5000系列、C6000系列,AD公司的BlackFin系列、SHARC系列、TigerSHARC系列等等,每款DSP都有其不同的特點。

針對本文設計的定位系統,綜合考慮各因素,選用TI公司的TMS320VC5509A作為系統的DSP。TMS320VC5509A是一款16位定點DSP,其片內的128 Kx16 bit SRAM空間可滿足算法的存儲空間需求;內核200MHz的時鐘頻率可滿足系統的實時性要求;4個外部存儲器片選信號便于通過FPGA,實現DSP與其他在板外設的數據交流和通信;5個外部中斷輸入可滿足外部設備對DSP的突發(fā)請求。

1.2.2 FPGA

現場可編程門陣列(Field Programmable Gate Array,FPGA)的功能是實現系統的時序控制,并完成外部設備與DSP的接口轉換,同時為了提高系統的實時性,實現定位系統的數字信號預處理,因此本文的FPGA選擇主要考慮FPGA的片內存儲器容量、乘法器數量、宏單元數量、性價比及開發(fā)的方便性等。目前可供選用的FPGA很多,根據定位系統的具體需求和研發(fā)人員的開發(fā)經驗,選用Altera公司的EP2C35F484作為系統的FPGA,用于實現其相應的功能。EP2C35F484內部具有33216個邏輯單元(LEs),能夠滿足系統的各種時序控制;483 840 bits的RAM容量可以為DSP提供足夠大的輸入輸出緩存,配合35個的乘法器,可以方便地實現數字信號預處理;4個PLL可以很方便地為系統產生不同的時鐘信號或時序;322個用戶I/O引腳數配合豐富的Les便于實現各種輸入輸出接口轉換。

1.2.3 模數及數模轉換器

模數及數模轉換器的選擇需同時考慮轉換頻率和分辨率。因此根據系統對輸入模擬信號的精度要求,選擇分辨率為16位的AD7665作為系統的模數(A/D)轉換器。AD7665的最高采樣頻率可達570 kS/s,而且其允許的輸范圍為±10 V。滿足系統的動態(tài)范圍;其數字輸出可采用串行或并行接口方式,便于與DSP或FPGA接口。

根據系統對輸出模擬信號的精度要求,選用18位的AD5545作為系統的數模轉換器(D/A)。AD5545是電流型輸出型的雙路D/A轉換器。由于AD5545采用串行接口方式接收控制器的數據,因此AD5545的幾何尺寸極小,便于高度集成。

1. 2. 4 存儲器

作為一個可以獨立運行的系統,總需要一定容量的非易失性存儲器,用于存儲系統的指令代碼和缺省的系統參數,因此本模塊采用閃存(FLASH存儲器)AMD29LV256M進行系統的非易失存儲器設計。AM29LV256M的容量為256 MBit,可以方便地構成16 Mx16-Bit或者32 Mx8-Bit的存儲器,滿足代碼的固化需求。另外由于采用LCD液晶屏作為系統的顯示器,而現有的LCD顯示器沒有顯示緩存,同時為了增加系統的通用性和靈活性,便于進行大數據量的數據處理,系統需設計大容量的靜態(tài)存儲器(SRAM)。本模塊選用CY7C1061AV33進行系統的外部存儲器擴展。CY 7C1061AV33容量1 M×16-Bit,訪問速度快。

1.3 系統的硬件電路設計

為了便于擴展,本模塊的設計分3大部分進行:模塊的供電、DSP最小系統以及以FPGA為核心的各種接口。

模塊的供電采用LM2676-ADJ、TPS79501、LT1584CT3.3,將輸入的12 V轉換成DSP和FPGA所需要的5、3.3、1.6、1.2 V,并通過控制電源芯片的使能靖實現DSP的上電順序。

DSP最小系統設計主要包括復位電路、時鐘電路、調試接口等,其中復位電路采用Max706結合相應的外部器件實現上電復位、手動復位、看門狗復位、DSP內核電源電壓過低復位、通過上位機復位等;時鐘電路的設計結合DSP或者FPGA的片內PLL、采用高精度、高穩(wěn)定度的外部有源晶振實現,并盡量降低外部晶振的頻率,模塊中的晶振頻率為20MHz。而調試接口的設計由于需要經常插拔調試接口,因此主要考慮抗靜電因素,通過在每根信號線上并聯瞬態(tài)電壓抑制器(TVS)實現;另外,為了進行較遠距離的調試,進行了調試接口的再驅動及緩沖。

以FPGA為核心的各種接口設計包括存儲器接口、外部中斷接口、AD接口、DA接口、串行接口、LCD顯示器接口等。為了便于擴展,DSP的EMIF信號線全部接到FPGA,并將FLASH存儲器(AM29LV256M)和SRAM存儲器(CY7C1061AV33)先通過FPGA再接到DSP的EMIF空間。也就是說,外部設備包括存儲器可方便地映射到DSP不同的存儲器空間。DSP的EMIF空間的缺省的配置為:CEO用于訪問FPGA的片內SRAM(作用輸入及輸出緩沖的存儲器):CE1用于訪問DSP的上電程序加載空間,與FLASH存儲器連接;CE2用于訪問SRAM空間。外部中斷接口用于將可選的多個外部中斷源有選擇的接到DSP的中斷輸入;缺省的配置為:INT0用于響應外部的同步,INT1用于RS422通信中斷,INT2用于RS232通信中斷;INT3、INT4為用戶備用中斷。AD接口首先將串行的采樣數據轉換成并行的數據并存放于FPGA的片內緩存或者直接將并行的采樣數據存放于FPGA的片內緩存,用于FPGA的數據預處理(如FIR、FFT等),然后再將預處理的結果送到輸出緩存。DA接口則在DSP的控制下、將DA輸出緩存中的并行數據轉換成AD5545所需要的串行接口數據,實現DA變換。串行接口則按照不同接口的收發(fā)協議,組織及收發(fā)數據,實現與不同設備的通信。LCD顯示接口實際上是一個連續(xù)讀寫顯存的接口,因此在FPGA內部設計了一個專門的讀寫顯存控制器(簡稱LCD控制器),可以獨立進行顯示、控制LC D;但是為了便于DSP及時更新顯示內容,在DSP和LCD控制器之間設計了一套仲裁電路,解決它們在讀寫顯存時的沖突。

2 應用程序設計

時延估計是聲源定位算法的關鍵內容。為了進行時延估計,首先基陣接收目標信號模擬信號,再經過采集、依據不同方法進行處理,得到目標信號到達各個陣元的相對時延。一種廣義互相關時延估計法(GCC)的流程圖如圖2所示。其中濾波在FPGA內部采用FIR實現,而FFT則可以由FPGA實現。也可由DSP實現。

3 實驗

輸入信號為兩路CW信號,信號頻率10kHz,脈寬1ms,兩路時延0.2 ms,信噪比為-3 dB,A/D的采樣頻率為300 kHz,則信號脈寬有300個點,估計時延峰值應該在偏離中心60點處。按照圖2的流程進行處理,采樣寬度為512個點,廣義互相關時延估計效果如圖3所示。由圖3可知,相關峰位于第455采樣點處,即時延估計為0.19 ms,與給定的時延基本一致。

4 結論

本文研究的信號處理模塊設計靈活性好、擴展性強,適合水下目標主被動定位系統的數據采集及處理,也可用于信號處理領域進行實時信號處理。本文所設計的以FPGA為核心的信號處理模塊具有較好的工程應用參考價值。