空間,!有待探索的最后一片疆域,將高性能RF信號鏈集成至更小空間的解決方案是行業(yè)需求也是未來趨勢。

日趨小巧緊湊的設(shè)備

在實驗室里有一臺Rohde & Schwarz FSIQ頻譜分析儀,,它的一側(cè)貼著一個標簽:“兩人抬”,。 如果我們讓時間快進十年,,可能只需要一只手就能拎起一臺先進的頻譜分析儀。 這雖然有點夸張,,但保守地說,肯定不需要“兩人抬”,。整個行業(yè)似乎都在重復這一幕,,設(shè)備變得越來越小,、越來越緊密,,或者保持尺寸不變的同時增加更多功能,。這增大了設(shè)備設(shè)計的難度,。 更嚴峻的問題是,,冷卻風扇卻在設(shè)備中用得越來越少,,這就帶來了降低設(shè)備功耗和自熱的壓力,。如圖1所示,,包括現(xiàn)代通信設(shè)備在內(nèi)的設(shè)備越來越小巧緊湊,。

圖1 小巧緊湊的設(shè)備

考慮無線收發(fā)器的設(shè)計方法時,必須盡早決定是否以分立方式構(gòu)建電路,。要實現(xiàn)藍牙,、Zigbee或GPS等常用無線電標準,,采用分立方案意義不大,。 同樣的道理,,高度集成的芯片組除了它的本來的應用外,,幾乎沒有其他用處,。一般從空間角度考慮,,高度集成的芯片組較佳,,但往往靈活性不足,,而且性能低于采用分立器件實現(xiàn)的電路,。這自然引出下面的問題:是否有一個兩全其美的解決方案,?也就是說,,它既有一定的集成度,,可以節(jié)省空間,同時能為設(shè)計人員提供適當?shù)撵`活性,。

必須考慮RF信號鏈中典型器件的相對尺寸。現(xiàn)代有源器件,,例如IQ調(diào)制器,、IQ解調(diào)器和混頻器等,,通常采用MLF封裝,典型尺寸為16mm2~36mm2,。VCO和SAW濾波器相對較大,。100mm2的VCO并不罕見,SAW濾波器的表面面積常常達到35mm2,。

LO合成技術(shù)的演變

基于PLL的頻率合成器有兩個主要器件:鎖相環(huán)(PLL)和壓控振蕩器(VCO),。由于分立VCO的尺寸相對較大,因此IC設(shè)計界非常希望將VCO集成到PLL中,。

雖然將VCO集成到IC芯片并不是特別困難,,但要集成高質(zhì)量VCO并非易事,。 所謂高質(zhì)量,是指信號的相位噪聲或頻譜純度,。較低的VCO相位噪聲可以改善接收機靈敏度以及發(fā)射和接收信號的誤差矢量幅度,。

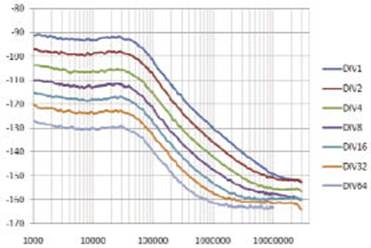

圖2所示比較多款集成到IC中的VCO相位噪聲性能。1MHz偏移時-135dBc/Hz的相位噪聲可以與分立VCO的性能相媲美,。

圖2 多款集成到IC中的VCO相位噪聲性能

ADF4350和ADF4351,,這些是集成VCO的PLL系列器件,。 除了相位噪聲非常低以外,這些器件中的VCO庫具有完整的倍頻程范圍,。將寬VCO頻率范圍與一組分頻器結(jié)合,,便可獲得137.5 MHz~4.4 GHz的連續(xù)工作范圍,。 對于ADF4351,,器件中還有額外的分頻器,,因此其最低工作頻率為35 MHz。

ADF4351 PLL的閉環(huán)相位噪聲性能如圖3所示,,VCO工作頻率為4.4GHz,。 閉環(huán)相位噪聲由上方的深藍色曲線表示。隨著分頻器相繼開啟,,輸出頻率不斷降低,;頻率每降低一半,相位噪聲性能提高6 dB,。

圖3 ADF4351 PLL的閉環(huán)相位噪聲性能

VCO庫提供一個倍頻程的調(diào)諧范圍,,利用分頻器陣列實現(xiàn)4.4GHz~35MHz的工作范圍。器件尺寸5mm×5mm,,主要外部元件包括電源去耦電容和環(huán)路濾波器,。

VCO和分頻器庫均集成于片上,剩余的外部器件只有電源去耦電容和外部環(huán)路濾波器,。因此,,集成VCO將能節(jié)省相當大的空間。

接收信號鏈的演變

接收機架構(gòu)如何演變,,以及對這些電路的尺寸有何影響呢,?回顧幾年前,,我們發(fā)現(xiàn),那時的典型分集接收機已經(jīng)具有一定的集成度,。但在混頻器的RF側(cè),,LNA和可變衰減器全部是分立器件?;祛l器的LO則利用外部VCO實現(xiàn),。

現(xiàn)在我們展望幾年后的情況,對于大多數(shù)應用,,帶分立VCO的PLL可以由單個集成器件所取代,。此外,混頻器RF側(cè)的集成度更高,。后置LNA放大器與可變衰減器集成在一起,。 這可以稱作水平集成,即信號鏈中的相鄰器件合并到一個封裝中,。但是,,可以注意到,前端LNA仍是一個獨立器件,。這是因為,,設(shè)計LNA的PHEMPT工藝并不是特別有利于與數(shù)字步進衰減器集成。

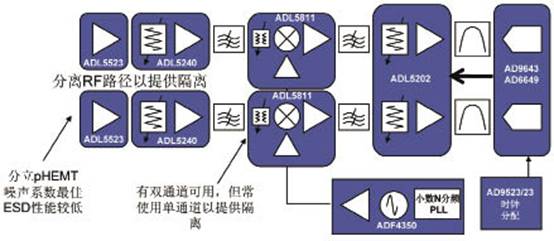

當我們集成分集接收機中的器件時,,還有一個選項可以考慮,,即所謂“垂直集成”。 如圖4所示,,我們選擇了雙通道ADC和雙通道ADC驅(qū)動器,,但使用兩個獨立的混頻器。

圖4 中頻采樣信號鏈的演變

垂直集成時必須考慮的一個重要因素是器件之間的寄生耦合或泄漏,。比如,,一個雙通道混頻器的輸入至輸入泄漏,值得注意的是泄漏水平隨輸入頻率提高而提高,。這是非常典型的現(xiàn)象,因為寄生耦合路徑的阻抗隨頻率提高而降低,。所以,,混頻器的RF側(cè)通常不采用垂直集成方式。就混頻器而言,,一般都會提供單通道和雙通道版本,,設(shè)計人員可以決定所需的集成度。

近年來,,業(yè)界熱衷于用直接變頻或零中頻接收機來取代常用的中頻采樣架構(gòu),,如圖5所示,。 零中頻接收機利用IQ解調(diào)器,將RF信號一步下變頻至基帶,。這種架構(gòu)最吸引人之處在于,,它無需前端鏡像濾波器以及尺寸相對較大、損耗較高的IF SAW濾波器,。這種方法具有空間優(yōu)勢,,但對頻率非常敏感。由于無需擔心IF和頻率規(guī)劃,,因此接收機的頻率范圍僅受PLL,、IQ解調(diào)器和前端LNA的工作范圍的限制。寬帶IQ解調(diào)器和PLL的選擇范圍廣,,所以這種方法非常適合可再配置的無線電應用,。

圖5 直接變頻接收架構(gòu)

采用直接變頻具有潛在的空間優(yōu)勢。在分集中頻采樣接收機和分集零中頻接收機的布局中值得注意的是,,空間使用率與外部無源組件密切相關(guān),,與其他方面的關(guān)系則不大。中頻采樣接收機具有一個長而窄的結(jié)構(gòu),,這是因為它需要兩個濾波器級,,一個是SAW濾波器,另一個是ADC之前的抗混疊濾波器,。因此,,零中頻接收機只需一個濾波器,而中頻采樣接收機則需要兩個濾波器,。

從性能和功耗兩方面比較這兩種架構(gòu),,在ADIsimRF中,對一個典型中頻采樣接收機所做的信號鏈分析,,在此增益設(shè)置下,,輸入IP3和噪聲系數(shù)分別為27.8 dBm和4.7 dB,功耗為2.2 W,。

如果在ADIsimRF中仿真一個等效的零中頻接收機,,輸入IP3大致相同,但噪聲系數(shù)為2.1 dB,,相對較低,。這主要是因為零中頻架構(gòu)中不存在高損耗SAW濾波器。功耗為3.17 W,,相對較高,。可以把這歸因于需要兩個ADC和兩個基帶放大器來驅(qū)動它,相比之下,,中頻采樣接收機中只需要一個,。雖然中頻采樣ADC的功耗通常高于基帶采樣ADC,但由于需要兩個基帶ADC和兩個ADC驅(qū)動器,,因此功耗優(yōu)勢不復存在,。

然而,這里有一個因素未被考慮,,那就是中頻采樣接收機所需的數(shù)字下變頻電路的功耗,。這一因素可能會使兩種方法的功耗大致相當。

若試圖去除中頻采樣接收機中的某些可集成器件,。這里,,有源混頻器集成了小數(shù)N分頻PLL和窄帶VCO。除了驅(qū)動混頻器以外,,LO還能供外部使用,。也可以由外部LO源驅(qū)動。

零中頻接收機無需IF SAW濾波器來抑制不良的帶內(nèi)和帶外信號,。在零中頻接收機中,,消除所有不良信號的任務落在ADC之前的抗混疊濾波器肩上。ADRF6561這款器件提供50dB的可變增益,,以及以1dB步進變化的1MHz~30MHz可編程濾波器帶寬,,所有這些特性都在一個5mm×5mm LFCSP封裝內(nèi)實現(xiàn)。

發(fā)射信號鏈的演變

零中頻發(fā)射機的功能框圖如圖6所示,。對于500MHz~6GHz范圍的無線電頻率,,使用IQ調(diào)制器直接跳變到RF已非常流行。發(fā)射端采用零中頻比接收端更普遍,,接收端仍以使用IQ解調(diào)器的中頻采樣或中頻到基帶轉(zhuǎn)換為主,。

本例中,發(fā)射機還包括一個回送電路,,它監(jiān)控功率放大器的失真,,并向基帶中運行的數(shù)字預失真算法提供反饋。這種配置不是真正的零中頻,,而是所謂的復中頻,,DAC輸出為112 MHz。因此,,可以使用單個LO來驅(qū)動IQ調(diào)制器和回送混頻器,。 如果使用集成PLL和VCO的IQ調(diào)制器,可以再進一步,,除了用于IQ調(diào)制器以外,,還可以從芯片中引出LO信號以驅(qū)動DPD混頻器,。

總結(jié)

首先,,針對存在專用芯片組的常用無線標準,,設(shè)計分立電路毫無疑問是不可取的。采用分立器件進行設(shè)計時,,我們擁有相當大的靈活性,,但要付出功耗更高的代價。使用直接變頻發(fā)射機和接收機可以節(jié)省空間,,但與傳統(tǒng)收發(fā)器相比,,功耗節(jié)省可能不大。

雙通道器件確實可以節(jié)省空間,,但須確保通道間泄漏在合理范圍內(nèi),。如果一個集成VCO的PLL可提供合理水平的相位噪聲,那么這將是分立RF電路設(shè)計中最能節(jié)省空間的地方之一,。

問答選編

問:ADI公司的RF信號鏈解決方案具體包括哪些內(nèi)容,?

答:包括框架構(gòu)建、各組件選型,、鏈路參數(shù)設(shè)計等,。

問: RF信號鏈與以往的產(chǎn)品差別是什么呢?

答:考慮無線收發(fā)器的設(shè)計方法時,,我們必須盡早決定是否以分立方式構(gòu)建電路,。 要實現(xiàn)藍牙、Zigbee或GPS等常用無線電標準,,采用分立方案意義不大,。 同樣的道理,高度集成的芯片組除了它的本來的應用外,,幾乎沒有其他用處,。一般從空間角度考慮,高度集成的芯片組較佳,,但往往靈活性不足,,而且性能低于采用分立器件實現(xiàn)的電路。這自然引出下面的問題:是否有一個兩全其美的解決方案,?也就是說,,它既有一定的集成度,可以節(jié)省空間,,同時能為設(shè)計人員提供適當?shù)撵`活性,。

問:抗干擾問題怎么解決?在集成度較高的方案中,,集成VCO的好處是什么,?

答:對于集成度較高的方案而言,很多接口都是內(nèi)部實現(xiàn)的??梢允∪チ送獠拷涌陔娐?,自然外圍電路就少了很多,集成VCO,,可以讓客戶的設(shè)計省去了外圍的的VCO電路等,。

問:在小芯片上實現(xiàn)高集成是否會導致各單元電路間的相互干擾?

答:電路干擾是肯定存在的,,但是ADI的完整的芯片集成設(shè)計技術(shù)可以更好的降低干擾,,使集成IC的性能可以滿足系統(tǒng)性能的指標要求。

問:為了節(jié)約成本和降低體積,,兼容各項3G標準,,有一種新的可調(diào)諧技術(shù),ADI公司在現(xiàn)有的產(chǎn)品是否有這方面的產(chǎn)品,?

答:ADI寬帶的PLL產(chǎn)品ADF4350可以支持軟件調(diào)整頻率,,ADI的寬帶調(diào)制器ADL5375和DVGA ADL5240/3可以支持寬帶工作,ADI的寬帶調(diào)諧混頻器ADL5811/2 可以支持軟件調(diào)整頻率和端口匹配,。

問:請問高性能RF信號鏈的主要特性有哪些,?

答:主要特性為更好的動態(tài)范圍,噪聲性能和諧波及雜散的抑制特性,,以及靈活的接口和應用性,。目前,ADI新的產(chǎn)品基本采用差分信號,,這樣很好的滿足了這些需求,。

問:巴倫接口是指什么?

答:巴倫是BALUN的音譯,,其含義是指平衡——不平衡變換器,。巴倫實現(xiàn)的接口間轉(zhuǎn)換,及單端信號轉(zhuǎn)換為差分信號,,或?qū)⒉罘中盘栟D(zhuǎn)換為單端信號,。

問:本振的性能怎樣?能否滿足RF信號鏈要求,?

答:是可以滿足RF信號鏈的需求的,。ADF4360是集成VCO的整數(shù)N分頻鎖相環(huán)產(chǎn)品,ADF4350是集成VCO的寬帶小數(shù)N分頻鎖相環(huán)產(chǎn)品,,其頻率范圍從137MHz~4.4GHz,。即將推出的還有ADF4351,將擁有更好的相噪性能和更寬的頻率輸出范圍,。

問:RF解決方案在PCB設(shè)計時需要注意什么,?

答:主要注意傳輸線特征阻抗的匹配,,接地,電源去耦等因素,。

問:在RF設(shè)計中,,EMI方面主要考慮的是什么?

答: EMI設(shè)計是復雜系統(tǒng)問題,,主要是良好接地和屏蔽,在本內(nèi)傳輸信號盡量功率小,,例如我們現(xiàn)在的調(diào)制器和混頻器的本振需求功率很小,,就可以使得本振傳輸功率變小,EMI風險就會降低等,。

問:集成的RF IC運用于無線基站設(shè)備產(chǎn)品的距離受哪些因素影響,?

答:對于無線信號傳輸距離,主要受到發(fā)射機發(fā)射功率,、接收機接收靈敏度,、射頻工作頻段、調(diào)制方式,、編解碼方式等因素影響,。

問:ADI高性能RF信號鏈對電源有特殊要求嗎?

答:射頻器件大都屬于敏感器件,,因此為了擁有更好的性能,,建議使用電源紋波小的電源,并注意電源去耦,。在大功率器件使用中,,要注意電源的驅(qū)動能力。

問:RF系統(tǒng)設(shè)計中如何綜合考慮ADC動態(tài)范圍,、噪聲等因素,?

答: ADI的網(wǎng)站上提供了一些列ADC設(shè)計指導的文檔,可計算出ADC等效的噪聲系數(shù)和IIP3特性,,從而可以結(jié)合信號鏈一起進行計算,。ADC的動態(tài)一般我們器件手冊上都會有標注,系統(tǒng)的動態(tài)一般等于ADC的動態(tài)加上前面AGC的動態(tài),,這是系統(tǒng)選擇AGC和ADC的一個依據(jù),。

問:ADI的RF方案在節(jié)能方面有什么優(yōu)勢?

答:ADI產(chǎn)品在保證性能的前提下,,保證了較低的功耗,,且器件大都具有Power-Down功能,以保證更低的功耗,。

問:請問注入鎖定是什么,?

答:注入鎖定是一種加快鎖定的方式,,就是在PLL負反饋穩(wěn)定前,采用人為加一個電壓使得VCO的頻率預先到一個頻率,,這樣就使得鎖定時間更短,。