文獻(xiàn)標(biāo)識(shí)碼: A

文章編號(hào): 0258-7998(2012)02-0131-03

ARM是目前全球最大的嵌入式芯片技術(shù)的IP提供商,其所擁有的IP已經(jīng)成為眾多芯片設(shè)計(jì)公司采納的一種技術(shù)標(biāo)準(zhǔn)和開發(fā)平臺(tái)。所以基于ARM 內(nèi)核的SoC已經(jīng)成為嵌入式處理器的開發(fā)重點(diǎn),可通過ARM實(shí)現(xiàn)LCD控制器來完成對(duì)嵌入式LCD屏的控制。如果利用TFT屏支持顯示,其圖像分辨率存在局限性,因此通過搭建一個(gè)FPGA平臺(tái)實(shí)現(xiàn)圖像縮放器功能外接LCD顯示器,完成ARM信號(hào)的擴(kuò)展顯示。同時(shí)FPGA也能完成對(duì)ARM平臺(tái)產(chǎn)生的圖像信號(hào)進(jìn)行驗(yàn)證和仿真,以測(cè)試其功能和時(shí)序的正確性。XGA顯示器因其顯示量大,輸出形式多樣等特點(diǎn)已經(jīng)成為目前大多數(shù)設(shè)計(jì)中的常用輸出設(shè)備,因此本文針對(duì)ARM產(chǎn)生的VGA信號(hào)通過插值算法對(duì)其擴(kuò)展為XGA標(biāo)準(zhǔn)信號(hào)。

1 VESA標(biāo)準(zhǔn)中的VGA與XGA時(shí)序

視頻電子標(biāo)準(zhǔn)協(xié)會(huì)(VESA)是非盈利國際組織,主要制定個(gè)人電腦、工作站以及消費(fèi)電子類產(chǎn)品在視頻接口標(biāo)準(zhǔn),因此本文所設(shè)計(jì)的VGA與XGA的時(shí)序均按照VESA標(biāo)準(zhǔn)設(shè)計(jì)。

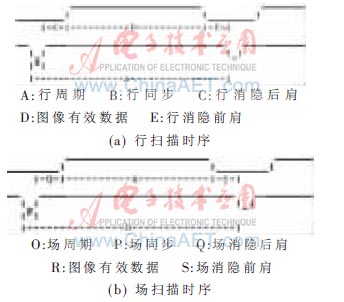

顯示器通常采用逐行掃描的方式,每一幀圖像按順序一行接著一行連續(xù)掃描而成,掃描的過程中由水平同步信號(hào)HSYNC和垂直同步信號(hào)VSYNC來控制掃描。行掃描和場(chǎng)掃描的時(shí)序圖如圖1所示,其行掃描和場(chǎng)掃描的時(shí)序要求如表1、表2所示。

圖1 行掃描時(shí)序和場(chǎng)掃描時(shí)序

2 系統(tǒng)整體設(shè)計(jì)

2.1系統(tǒng)框圖

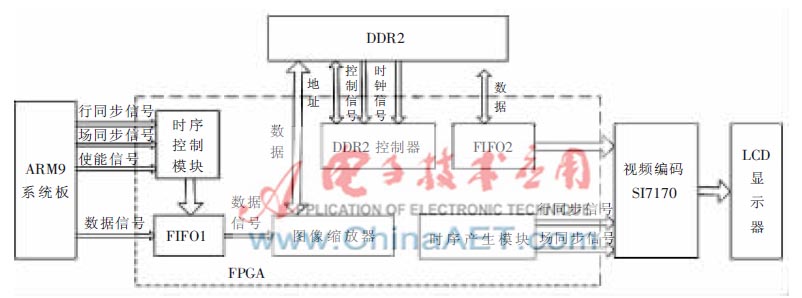

系統(tǒng)設(shè)計(jì)的數(shù)據(jù)源是來自ARM9系統(tǒng)板的視頻信號(hào),其格式為VESA標(biāo)準(zhǔn)的VGA信號(hào)。數(shù)據(jù)源進(jìn)入FPGA后先進(jìn)行圖像縮放的處理,把輸入的有效像素?cái)?shù)據(jù)利用算法對(duì)其進(jìn)行處理,期間的處理數(shù)據(jù)利用FIFO與DDR2進(jìn)行緩存,然后把處理后的圖像數(shù)據(jù)按照XGA時(shí)序送入視頻編碼芯片,最后送入顯示器顯示。其中FPGA內(nèi)部設(shè)計(jì)分為時(shí)序控制模塊、時(shí)序產(chǎn)生模塊、FIFO模塊、圖像縮放器模塊以及DDR2 SDRAM控制器模塊,如圖2所示。

圖2 系統(tǒng)原理框圖

2.2 硬件實(shí)現(xiàn)

FPGA采用Altera的EP3C16F484C6芯片,該芯片具有15 408個(gè)邏輯單元,504 KB內(nèi)存,56個(gè)乘法器和4個(gè)PLL鎖相環(huán)內(nèi)核,最大支持346個(gè)I/O端口,系統(tǒng)時(shí)鐘最高為250 MHz。FPGA開發(fā)板采用了專門的視頻解碼編碼芯片,Silicon Image的視頻編碼芯片SI7170支持VGA到UVGA的格式標(biāo)準(zhǔn),同時(shí)也支持HDTV格式的編碼。DDR2 SDRAM采用三星的K4T51163QC芯片, 其頻率支持267 MHz,本文選取為200 MHz。芯片容量為32 MB×16,實(shí)際上只要SDRAM滿足存儲(chǔ)2幀圖像的容量即可滿足本文設(shè)計(jì)要求[1]。完成轉(zhuǎn)換后的XGA信號(hào)所需的輸出時(shí)鐘為65 MHz,可由FPGA內(nèi)部鎖相環(huán)產(chǎn)生。

3 FPGA內(nèi)部模塊工作原理

3.1輸入時(shí)序控制模塊與輸出時(shí)序控制模塊

輸入時(shí)序控制模塊是根據(jù)輸入視頻信號(hào)的同步信號(hào)和時(shí)序要求,確保有效的圖像數(shù)據(jù)能夠順利寫入FIFO進(jìn)行緩存。例如當(dāng)模塊接收到場(chǎng)同步信號(hào)時(shí),F(xiàn)IFO進(jìn)入即將寫入的狀態(tài),當(dāng)模塊接收到使能信號(hào)時(shí), FIFO開始寫入數(shù)據(jù),這樣能確保寫入FIFO的數(shù)據(jù)是從完整1幀圖像的起始開始寫入。

輸出時(shí)序控制模塊的功能是產(chǎn)生輸出圖像所必需的同步信號(hào)、場(chǎng)同步信號(hào)和行同步信號(hào),以保證輸出圖像的數(shù)據(jù)與時(shí)序一致,從而使圖像可以正確地顯示在顯示器上。

輸入輸出時(shí)序控制模塊,按照計(jì)數(shù)器的方法進(jìn)行設(shè)計(jì)[2]。例如VGA信號(hào)的1幀圖像的總像素要求為800×525,其中有效像素為640×480。對(duì)于行掃描來說可設(shè)置1~96像素時(shí)鐘計(jì)數(shù)為行同步信號(hào),97~144像素時(shí)鐘計(jì)數(shù)為行消隱后肩,145~784像素時(shí)鐘計(jì)數(shù)為圖像有效像素顯示,685~800像素時(shí)鐘計(jì)數(shù)為行消隱前肩。完成一行后,計(jì)數(shù)器置0,等待新的行同步信號(hào)到來再重新計(jì)數(shù)。在圖像有效像素時(shí)鐘內(nèi),讓寫入FIFO使能信號(hào)處于有效狀態(tài),而其余時(shí)間使能信號(hào)處于無效狀態(tài),這樣可保證有效圖像數(shù)據(jù)能準(zhǔn)確寫入FIFO進(jìn)行緩存,并等待下一步的處理。

3.2 圖像縮放器模塊

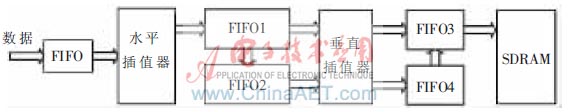

如圖3所示,圖像縮放器模塊主要完成對(duì)輸入圖像數(shù)據(jù)源進(jìn)行分辨率的縮放。根據(jù)設(shè)計(jì),輸入的圖像數(shù)據(jù)為VGA 640×480格式,輸出的圖像數(shù)據(jù)為XGA 1024×768格式。由于輸入圖像數(shù)據(jù)與輸出圖像數(shù)據(jù)在完整1幀中的每一行像素點(diǎn)和每一列的數(shù)量上之比都為5:8,因此可考慮對(duì)輸入的VGA信號(hào)作5:8的放大。先對(duì)數(shù)據(jù)在水平方向上進(jìn)行插值放大,然后再進(jìn)行垂直方向上的放大,設(shè)計(jì)中水平方向和垂直方向的插值放大均使用分級(jí)雙線性插值算法。

圖3 圖像縮放器模塊框圖

3.2.1分級(jí)雙線性插值 [3]

在雙線性插值算法中,插值點(diǎn)的值根據(jù)其相鄰的4個(gè)已知點(diǎn)計(jì)算得出,如圖4所示。

圖4 雙線性插值算法原理圖

已知a、b、c、d為輸入圖像內(nèi)的相鄰的4個(gè)點(diǎn),其灰度值表示為f(x)。待插像素f點(diǎn)映射到原圖像后的坐標(biāo)值小數(shù)部分為[m,n]。計(jì)算f點(diǎn)灰度值的過程如式(1)~式(3)所示:

f[g]=f[a]+m(f(b)-f(a)) (1)

f[h]=f[c]+m(f(d)-f(c)) (2)

f[f]=f[g]+m(f(h)-f(g))

=(1-m)(1-n)f(a)+m(1-n)f(b)+(1-m)nf(c)+mnf(d) (3)

分級(jí)雙線性插值使用的4個(gè)源圖像像素點(diǎn)都是待插值點(diǎn)的直接鄰點(diǎn)。插值的計(jì)算過程如下:

g(x)=(f(a)(m×N)+f(b)×(1-m)N)/N

其中,m與1-m分別是a點(diǎn)與b點(diǎn)的權(quán)值。因?yàn)槭亲?:8的轉(zhuǎn)換,這里取C=N=8, 將原來為5個(gè)像素點(diǎn)的長(zhǎng)度區(qū)間劃分為8個(gè)區(qū)間,每個(gè)區(qū)間都有m×N與(1-m)N這一對(duì)權(quán)值組成的整數(shù)對(duì)。每個(gè)區(qū)間內(nèi)部的待插值點(diǎn)都與該區(qū)間左邊界取同樣的值。8個(gè)區(qū)間的權(quán)值對(duì)應(yīng)于(8,0)、(7,1)、(6,2)、(5,3)(4,4)、(3,5)、(2,6)和(1,7)。在確定好了點(diǎn)位置后,以查找表的方式寫入權(quán)值與位置之間的關(guān)系,最后可根據(jù)內(nèi)插點(diǎn)與臨近點(diǎn)的相對(duì)位置查找對(duì)應(yīng)系數(shù),并通過計(jì)算得出各像素點(diǎn)的灰階值。

3.2.2具體插值過程

3.2.2.1水平插值

將雙線性插值分解為水平和垂直方向進(jìn)行,由于是把原圖像作5:8的放大,所以根據(jù)分級(jí)雙線性插值,把原水平方向的5個(gè)像素點(diǎn)采用分8級(jí)雙線性插值送入水平插值器。水平插值器由計(jì)數(shù)器與使能信號(hào)同時(shí)控制,每間隔5個(gè)時(shí)鐘,水平插值器使能端置于計(jì)算插值狀態(tài),把進(jìn)入的5個(gè)值進(jìn)行一次插值變成新的8個(gè)像素點(diǎn),之后再間隔5個(gè)時(shí)鐘,將新的值進(jìn)入插值器進(jìn)行插值,直到把1行640個(gè)像素點(diǎn)插值為1行1 024個(gè)像素點(diǎn)。

3.2.2.2 垂直插值

垂直插值器完成垂直方向5:8的轉(zhuǎn)換,即5行數(shù)據(jù)變?yōu)?行數(shù)據(jù)的轉(zhuǎn)換,插值過程是按垂直方向?qū)υ瓉淼?行數(shù)據(jù)采用分8級(jí)雙線性插值,變換為新的8行數(shù)據(jù)。

完成水平插值的數(shù)據(jù)流水線型通過FIFO1與FIFO2模塊,期間將FIFO1與FIFO2的值送入垂直插值器進(jìn)行插值,完成垂直插值后的數(shù)據(jù)送入FIFO3與FIFO4模塊,輸出順序排列在先的送入FIFO3,而另外一行數(shù)據(jù)進(jìn)入FIFO4。FIFO3與FIFO4之間的數(shù)據(jù)也是流水線型進(jìn)入到DDR2 SDRAM模塊中,整個(gè)過程通過使用狀態(tài)機(jī)對(duì)垂直插值進(jìn)行控制,使經(jīng)過垂直插值后的數(shù)據(jù)能以正確的順序完成插值,并且送入DDR2 SDRAM模塊。把對(duì)原5行數(shù)據(jù)經(jīng)過水平和垂直插值變?yōu)?行數(shù)據(jù)的時(shí)間作為一個(gè)周期,直到完成整1幀VGA格式圖像到1幀XGA圖像的放大。

3.3 DDR2 SDRAM控制器模塊

控制器模塊的具體作用為:當(dāng)SCALER完成圖像數(shù)據(jù)處理后,把圖像數(shù)據(jù)送進(jìn)DDR2中儲(chǔ)存,在確保DDR2中存儲(chǔ)有2幀完整圖像時(shí),DDR2的讀出端才開始讀取,從第一幀圖像地址讀取圖像數(shù)據(jù),然后據(jù)根據(jù)時(shí)序控制從DDR2輸出。當(dāng)讀完第一幀后,繼續(xù)讀取第二幀,此時(shí)第三幀繼續(xù)寫入原第一幀地址,之后的讀取寫入都按此過程進(jìn)行。

由于DDR2 SDRAM不能同時(shí)寫入和讀出,所以需要DDR2 SDRAM控制器加以控制。可根據(jù)連接到DDR2 SDRAM模塊寫入端和讀出端的FIFO內(nèi)部已存數(shù)據(jù)數(shù)量進(jìn)行讀寫控制。寫入端前的FIFO即為圖3的FIFO3。連接到DDR2讀出端的FIFO為圖3的FIFO2,它與輸出時(shí)序控制模塊共同完成最終所需XGA圖像的輸出。DDR2 SDRAM每次操作指令時(shí),以1行數(shù)據(jù)為單位,即接受1次讀命令,則讀出1行數(shù)據(jù);同樣,接受1次寫入命令,則寫入1行數(shù)據(jù),此1行數(shù)據(jù)同時(shí)為XGA格式的1行(1 024個(gè)像素點(diǎn)數(shù)據(jù))。

4 仿真與功能實(shí)現(xiàn)

在設(shè)計(jì)中,采用Verilog語言對(duì)各邏輯模塊進(jìn)行編寫設(shè)計(jì),在開發(fā)環(huán)境Quartus II 9.1和Modelsim-altera 6.5b下完成對(duì)各模塊的時(shí)序的仿真和功能的設(shè)計(jì)和驗(yàn)證,如圖5所示為數(shù)據(jù)進(jìn)入水平插值器后的仿真結(jié)果,水平插值把原5像素插為新8像素的仿真,其中pix為待插值的5個(gè)像素,data為插值后的8個(gè)新像素。

圖5 水平插值5像素插成8像素Modelsim仿真圖

經(jīng)過對(duì)各模塊設(shè)計(jì)的仿真,并且對(duì)各模塊功能驗(yàn)證正確后,進(jìn)行系統(tǒng)整體的仿真驗(yàn)證,最終將處理完成圖像數(shù)據(jù)送到LCD上進(jìn)行顯示,經(jīng)過放大后的示例如圖6 所示。仿真驗(yàn)證表明,得到的圖像時(shí)序和數(shù)據(jù)與要求的時(shí)序一致,對(duì)于圖像數(shù)據(jù)來說雖然雙線性會(huì)對(duì)屏幕邊緣存在高頻分量的損失[4],使輪廓稍有模糊,但是從圖像上對(duì)人眼觀看的影響很小。

圖6 經(jīng)過放大的ARM圖像信號(hào)在LCD上的顯示(XGA格式)

介紹了VESA標(biāo)準(zhǔn)中的VGA與XGA時(shí)序,通過FPGA平臺(tái)設(shè)計(jì)圖像縮放器,完成控制信號(hào)、時(shí)序信號(hào)和數(shù)據(jù)信號(hào)的同時(shí)輸入和控制,同時(shí)使用插值算法對(duì)分辨率進(jìn)行放大,達(dá)到了對(duì)ARM圖像信號(hào)的擴(kuò)展顯示。如要實(shí)現(xiàn)更多格式之間的轉(zhuǎn)換,可在程序?qū)懭敫鞣N圖像格式縮放之間的算法,如VGA、XGA、SVGA等格式。在程序中利用狀態(tài)機(jī)實(shí)現(xiàn)不同格式之間的轉(zhuǎn)換和時(shí)序的控制,加強(qiáng)縮放的范圍,擴(kuò)展其運(yùn)用。

參考文獻(xiàn)

[1] 張旭,王彬.一種基于FPGA的實(shí)時(shí)圖像轉(zhuǎn)換控制器的設(shè)計(jì)[J].電子技術(shù)應(yīng)用,2007,33(10):66-68.

[2] 陳偉,盧貴主,鄭靈翔. 基于雙線性算法的定標(biāo)器及其FPGA實(shí)現(xiàn)[J].電子技術(shù)應(yīng)用,2008,34(4):40-43.

[3] 朱艷亮. 實(shí)時(shí)視頻縮放算法研究及FPGA的實(shí)現(xiàn)[D].長(zhǎng)沙:中南大學(xué),2009.

[4] 孫紅進(jìn).FPGA實(shí)現(xiàn)的視頻圖像縮放顯示[J]. 液晶與顯示, 2010,25(1):130-133.