電路功能與優(yōu)勢(shì)

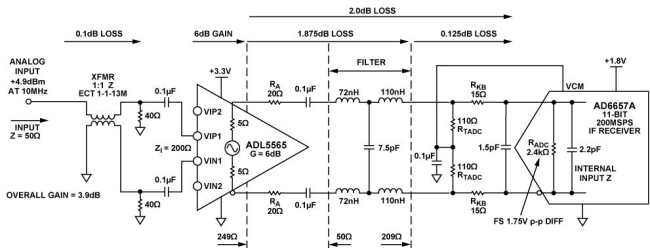

圖1所示電路是基于超高動(dòng)態(tài)范圍差分放大器驅(qū)動(dòng)器ADL5565和11位、200 MSPS四通道中頻接收機(jī)AD6657A的65 MHz帶寬接收機(jī)前端。

四階巴特沃茲抗混疊濾波器基于放大器和中頻接收機(jī)的性能和接口要求而優(yōu)化。由濾波器網(wǎng)絡(luò)和其他阻性元件引起的總插入損耗僅為2.0 dB。總體電路帶寬為65 MHz,低通濾波器在190 MHz下具有1 dB帶寬,在210 MHz下具有3 dB帶寬。通帶平坦度為1dB。

該電路專(zhuān)為處理以140 MHz為中心、采樣速率為184.32 MSPS的65 MHz帶寬中頻信號(hào)而優(yōu)化。在65 MHz頻段內(nèi)采用140 MHz模擬輸入測(cè)得的SNR和SFDR分別為70.1 dBFS和80.9 dBc。

圖1:四通道中頻接收機(jī)前端的單通道(原理示意圖:未顯示所有連接和去耦)增益、損耗和信號(hào)電平10 MHz下測(cè)得值

電路描述

圖1所示電路接受單端輸入并使用寬帶寬(3 GHz) M/A-COM ECT1-1-13M 1:1變壓器將其轉(zhuǎn)換為差分信號(hào)。 ADL5565 6.0 GHz差分放大器采用6 dB增益工作時(shí)具有200 Ω的差分輸入阻抗,采用12 dB增益工作時(shí)為100 Ω,采用15.5 dB增益工作時(shí)為67 Ω。

ADL5565是 AD6657A的理想驅(qū)動(dòng)器,通過(guò)低通濾波器可在ADC中實(shí)現(xiàn)全差分架構(gòu),提供良好的高頻共模抑制,同時(shí)將二階失真產(chǎn)物降至最低。 ADL5565根據(jù)輸入連接提供6 dB、12 dB和15.5 dB的增益。此電路中,使用6 dB增益補(bǔ)償濾波器網(wǎng)絡(luò)和變壓器(約2.1 dB)的插入損耗,從而提供4.0 dB的總信號(hào)增益。增益還有助于將放大器的噪聲影響降至最低。

AD6657A是一款四通道中頻接收機(jī),其中將每個(gè)ADC輸出從內(nèi)部連接到數(shù)字噪聲整形再量化器(NSR)模塊。集成NSR電路能夠提高奈奎斯特帶寬內(nèi)較小頻段的信噪比(SNR)性能。

可以對(duì)NSR模塊進(jìn)行編程,以提供采樣速率22%、33%或36%的帶寬。對(duì)于本電路筆記內(nèi)采用的數(shù)據(jù),采樣速率為184.32 MSPS,且以下NSR設(shè)置適用:

NSR帶寬 = 36%

調(diào)諧字(TW) = 12

左頻帶邊緣 = 11.06 MHz(輸入 = 173.26 MHz)

中心頻率 = 44.24 MHz(輸入 = 140.08 MHz)

右頻帶邊緣 = 77.41 MHz(輸入 = 106.91 MHz)

NSR模塊的詳細(xì)工作原理請(qǐng)參見(jiàn) AD6657A數(shù)據(jù)手冊(cè)。

抗混疊濾波器是采用標(biāo)準(zhǔn)濾波器設(shè)計(jì)程序(本例中是Agilent ADS)設(shè)計(jì)的四階巴特沃茲低通濾波器。選擇巴特沃茲濾波器是因?yàn)樗哂衅教鬼憫?yīng)。四階濾波器產(chǎn)生1.03的交流噪聲帶寬比。

為了實(shí)現(xiàn)最佳性能,ADL5565應(yīng)載入至少200 Ω的凈差分負(fù)載。20 Ω串聯(lián)電阻將濾波器電容與放大器輸出隔離開(kāi),當(dāng)加入下游阻抗時(shí)可產(chǎn)生249 Ω的凈負(fù)載阻抗。

15 Ω電阻與ADC輸入串聯(lián),將內(nèi)部開(kāi)關(guān)瞬變與濾波器和放大器隔離開(kāi)。110 Ω電阻與ADC并聯(lián),用于降低ADC的輸入阻抗,使性能更具可預(yù)測(cè)性。

AD6657A的差分輸入阻抗與2.2 pF并聯(lián),約為2.4 kΩ。對(duì)于該類(lèi)型的開(kāi)關(guān)電容輸入ADC,實(shí)部與虛部與輸入頻率成函數(shù)關(guān)系;詳細(xì)分析請(qǐng)參見(jiàn)應(yīng)用筆記AN-742。

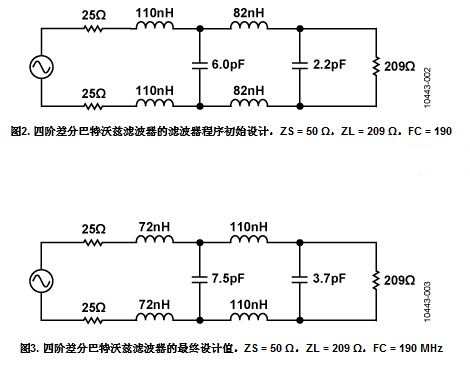

四階巴特沃茲濾波器采用50 Ω的源阻抗、209 Ω的負(fù)載阻抗和190 MHz的3 dB帶寬設(shè)計(jì)而成。濾波器的最終電路值如圖1所示。從濾波器程序生成的值如圖2所示。為濾波器無(wú)源元件選擇的值是最接近程序生成值的標(biāo)準(zhǔn)值。ADC的內(nèi)部2.2 pF電容用作濾波器設(shè)計(jì)的最終分流電容。

從本設(shè)計(jì)可以看出,最佳性能的獲得有時(shí)可以是迭代過(guò)程。濾波器程序設(shè)計(jì)值非常接近最終值,但由于存在一些板寄生電容,濾波器最終值略有不同。圖3顯示了濾波器的最終設(shè)計(jì)值。

圖

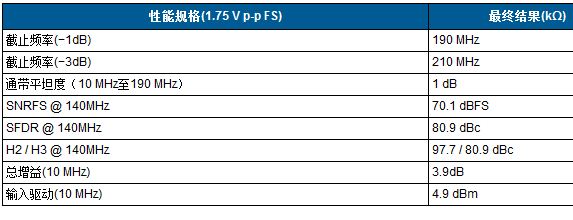

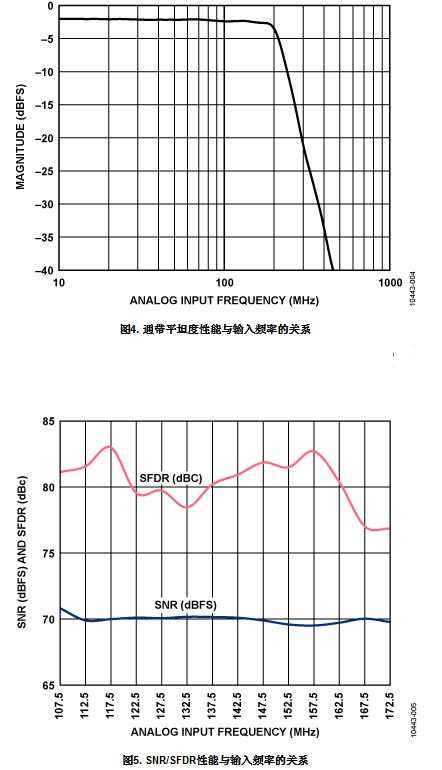

表1總結(jié)了系統(tǒng)的測(cè)量性能,其中3 dB帶寬為210 MHz。網(wǎng)絡(luò)的總插入損耗約為2 dB。圖4所示為最終濾波器電路的帶寬響應(yīng),圖5所示為SNR和SFDR性能。

表1. 電路的測(cè)定性能

圖

濾波器和接口設(shè)計(jì)程序

本節(jié)介紹放大器/ADC與濾波器接口設(shè)計(jì)的常用方法。為了實(shí)現(xiàn)最佳性能(帶寬、SNR、SFDR等),放大器和ADC應(yīng)對(duì)一般電路形成某些設(shè)計(jì)限制:

放大器應(yīng)參考數(shù)據(jù)手冊(cè)推薦的正確直流負(fù)載,以獲得最佳性能。

放大器與濾波器的負(fù)載間必須使用正確數(shù)量的串聯(lián)電阻。這是為了防止通帶內(nèi)的不良信號(hào)尖峰。

ADC的輸入應(yīng)通過(guò)外部并聯(lián)電阻降低,并使用正確串聯(lián)電阻將ADC與濾波器隔離開(kāi)。此串聯(lián)電阻也會(huì)減少信號(hào)尖峰。

此設(shè)計(jì)方法傾向于利用大多數(shù)高速ADC的相對(duì)較高輸入阻抗和驅(qū)動(dòng)源的相對(duì)較低阻抗,將濾波器的插入損耗降至最低。

電路優(yōu)化技術(shù)和權(quán)衡

本接口電路內(nèi)的參數(shù)具有高互動(dòng)性;因此優(yōu)化電路的所有關(guān)鍵規(guī)格(帶寬、帶寬平坦度、SNR、SFDR、增益等)幾乎不可能。不過(guò),通過(guò)變更RA和RKB,可以最大程度地減少通常發(fā)生于帶寬響應(yīng)內(nèi)的信號(hào)尖峰。

ADC輸入端的串聯(lián)電阻(RKB)應(yīng)選擇為盡量減少任何殘余電荷注入(從ADC內(nèi)部采樣電容)造成的失真。增加此電阻也傾向減少帶內(nèi)的信號(hào)尖峰。

不過(guò),增加RKB會(huì)增加信號(hào)衰減,因此放大器必須驅(qū)動(dòng)更大信號(hào)才能填充ADC的輸入范圍。

優(yōu)化通帶平坦度的另一方法是略微變更濾波器分流電容。

ADC輸入端接電阻(2RTADC)通常應(yīng)選擇為使凈ADC輸入阻抗介于200 Ω和400 Ω之間。降低該電阻可減少ADC輸入電容的效應(yīng)并穩(wěn)定濾波器設(shè)計(jì),但會(huì)增加電路的插入損耗。提高該值也會(huì)減少信號(hào)尖峰。

上述因素的權(quán)衡可能有些困難。本設(shè)計(jì)中,每個(gè)參數(shù)權(quán)重相等;因此所選值代表了所有設(shè)計(jì)特征的接口性能。某些設(shè)計(jì)中,可根據(jù)系統(tǒng)要求選擇不同值,以?xún)?yōu)化SFDR、SNR或輸入驅(qū)動(dòng)電平。

本設(shè)計(jì)中的SFDR性能取決于兩個(gè)因素:放大器和ADC接口元件值,如圖1所示。表1和圖5所示的最終SFDR性能數(shù)字是在優(yōu)化濾波器設(shè)計(jì)后獲得的,考慮了用于濾波器設(shè)計(jì)的板寄生電容和非理想元件。

該特定設(shè)計(jì)中可以權(quán)衡的另一因素是ADC滿(mǎn)量程設(shè)置。對(duì)于采用本設(shè)計(jì)獲得的數(shù)據(jù),滿(mǎn)量程ADC差分輸入電壓設(shè)置為1.75 V p-p,它可以?xún)?yōu)化SFDR。將滿(mǎn)量程輸入范圍更改為2.0 V p-p可稍稍改善SNR,但SFDR性能會(huì)略微降低。沿相反方向?qū)M(mǎn)量程輸入范圍更改為1.5 V p-p可稍稍改善SFDR,但SNR性能會(huì)略微降低。

請(qǐng)注意,本設(shè)計(jì)中的信號(hào)與0.1 μF電容進(jìn)行交流耦合,以阻擋放大器、其端接電阻和ADC輸入之間的共模電壓。

無(wú)源元件和PCB寄生考慮因素

該電路或任何高速電路的性能都高度依賴(lài)于適當(dāng)?shù)腜CB布局,包括但不限于電源旁路、受控阻抗線路(如需要)、元件布局、信號(hào)布線以及電源層和接地層。高速ADC和放大器PCB布局的詳情請(qǐng)參見(jiàn)教程MT-031和MT-101。

低寄生表面貼裝電容、電感和電阻應(yīng)用于濾波器內(nèi)的無(wú)源元件。所選電感來(lái)自Coilcraft 0603CS系列。濾波器所用表面貼裝電容的穩(wěn)定性和精度是5%、C0G、0402型。

常見(jiàn)變化

針對(duì)需要更少帶寬和更低功耗的應(yīng)用,可使用ADL5562差分放大器。 ADL5562的帶寬為3.3 GHz。如需更低的功耗和帶寬,還可使用 ADA4950-1。該器件的帶寬為1 GHz,僅使用10 mA的電流。

電路評(píng)估與測(cè)試

此電路使用經(jīng)過(guò)修改的EVAL-CN0259-HSCZ電路板和HSC-ADC-EVALCZ FPGA數(shù)據(jù)采集板。這兩片板具有對(duì)接高速連接器,可以快速完成設(shè)置并評(píng)估電路性能。經(jīng)過(guò)修改的AD6657AEBZ板包含依照本筆記所述進(jìn)行評(píng)估的電路,HSC-ADC-EVALCZ數(shù)據(jù)采集板配合Visual Analog評(píng)估軟件和SPI控制器軟件使用,以正確控制ADC并采集數(shù)據(jù)。