1.引言

隨著嵌入式相關(guān)技術(shù)的迅速發(fā)展,嵌入式系統(tǒng)的功能越來越強大,應(yīng)用接口更加豐富,根據(jù)實際應(yīng)用的需要設(shè)計出特定的嵌入式最小系統(tǒng)和應(yīng)用系統(tǒng),是嵌入式系統(tǒng)設(shè)計的關(guān)鍵。目前在嵌入式系統(tǒng)開發(fā)的過程中,開發(fā)者往往把大量精力投入到嵌入式微處理器MPU(Micro Processing Unit)與眾多外設(shè)的連接方式以及應(yīng)用代碼的開發(fā)之中,而忽視了對嵌入式系統(tǒng)最基本、最核心部分的研究。

當(dāng)前在嵌入式領(lǐng)域中,ARM(Advanced RISC Machines)處理器被廣泛應(yīng)用于各種嵌入式設(shè)備中。由于ARM嵌入式體系結(jié)構(gòu)類似并且具有通用的外圍電路,同時ARM內(nèi)核的嵌入式最小系統(tǒng)的設(shè)計原則及方法基本相同,這使得對嵌入式最小系統(tǒng)的研究在整個系統(tǒng)的開發(fā)中具有著至關(guān)重要的意義。本文以基于ARM的嵌入式最小系統(tǒng)為平臺,從硬件和軟件兩方面對嵌入式最小系統(tǒng)的架構(gòu)進行了研究,硬件方面主要介紹了ARM處理器與典型外部存儲器的接口技術(shù),軟件方面重點就嵌入式最小系統(tǒng)的啟動架構(gòu)做了詳細分析。

2. 嵌入式最小系統(tǒng)

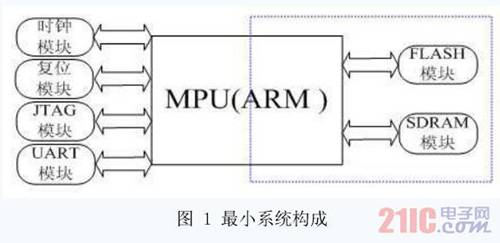

嵌入式最小系統(tǒng)即是在盡可能減少上層應(yīng)用的情況下,能夠使系統(tǒng)運行的最小化模塊配置。對于一個典型的嵌入式最小系統(tǒng),以ARM處理器為例,其構(gòu)成模塊及其各部分功能如圖1所示,其中ARM微處理器、FLASH和SDRAM模塊是嵌入式最小系統(tǒng)的核心部分。

時鐘模塊——通常經(jīng)ARM內(nèi)部鎖相環(huán)進行相應(yīng)的倍頻,以提供系統(tǒng)各模塊運行所需的時鐘頻率輸入

Flash存儲模塊——存放啟動代碼、操作系統(tǒng)和用戶應(yīng)用程序代碼

SDRAM模塊——為系統(tǒng)運行提供動態(tài)存儲空間,是系統(tǒng)代碼運行的主要區(qū)域

JTAG模塊——實現(xiàn)對程序代碼的下載和調(diào)試

UART模塊——實現(xiàn)對調(diào)試信息的終端顯示

復(fù)位模塊——實現(xiàn)對系統(tǒng)的復(fù)位

3. 外存儲器接口技術(shù)

ARM處理器與外部存儲器(Flash和SDRAM)的接口技術(shù)是嵌入式最小系統(tǒng)硬件設(shè)計的關(guān)鍵。根據(jù)需要選擇合理的接口方式,可以有效的提升嵌入式系統(tǒng)的整體性能。

3.1常用外存儲器簡介

(1)Nor Flash與Nand Flash

Nor Flash也稱為線性Flash,可靠性高、隨機讀取速度快,具有芯片內(nèi)執(zhí)行(XIP, eXecute In Place)的特點,這樣應(yīng)用程序可以直接在Flash閃存內(nèi)運行,不必再把代碼讀到系統(tǒng)RAM中。常用在擦除和編程操作較少而直接執(zhí)行代碼的場合。

Nand Flash則是高數(shù)據(jù)存儲密度的理想解決方案,一般用于數(shù)據(jù)存儲和文件存儲,以塊為單位進行擦除,具有擦除速度快的優(yōu)點。

(2)同步動態(tài)存儲器SDRAM

SDRAM(Synchronous Dynamic Random Access Memory)是在早期DRAM的基礎(chǔ)上改進而來的,它是同步內(nèi)存,并在接口信號中引入了CLK信號,所有數(shù)據(jù)、地址和控制信號都是和CLK上升沿對齊的。此外SDRAM還在內(nèi)部引入了一個命令控制器,處理器訪問SDRAM都是通過向命令控制器發(fā)送命令來實現(xiàn)的。

3.2 ARM處理器與Flash接口技術(shù)

3.2.1ARM處理器與Nor Flash接口技術(shù)

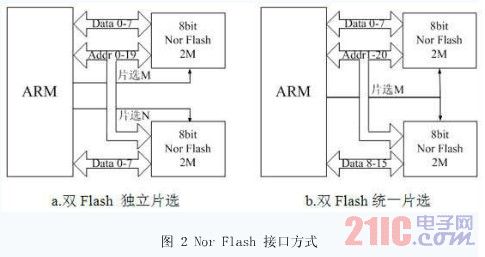

Nor Flash 帶有SRAM接口,有足夠的地址引腳,可以很容易的對存儲器內(nèi)部的存儲單元進行直接尋址。在實際的系統(tǒng)中,可以根據(jù)需要選擇ARM處理器與Nor Flash的連接方式。圖2給出了嵌入式最小系統(tǒng)在包含兩塊Nor Flash的情況下,ARM處理器與Nor Flash兩種不同的連接方式。

1)雙Flash獨立片選

該方式是把兩個Nor Flash芯片各自作為一個獨立的單元進行處理。根據(jù)不同的應(yīng)用需要,可以在一塊Flash中存放啟動代碼,而在另一塊Flash中建立文件系統(tǒng),存放應(yīng)用代碼。該方式操作方便,易于管理。

(2)雙Flash統(tǒng)一片選

該方式是把兩個Nor Flash芯片合為一個單元進行處理,ARM處理器將它們作為一個并行的處理單元來訪問,本例是將兩個8bit的Nor Flash芯片SST39VF1601用作一個16bit單元來進行處理。對于N(N>2)塊Flash的連接方式可以此作為參考。

3.2.2ARM處理器與Nand Flash接口技術(shù)

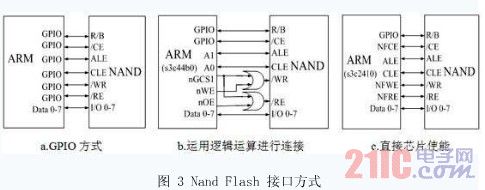

Nand Flash接口信號比較少,地址,數(shù)據(jù)和命令總線復(fù)用。Nand Flash的接口本質(zhì)上是一個I/O接口,系統(tǒng)對Nand Flash進行數(shù)據(jù)訪問的時候,需要先向Nand Flash發(fā)出相關(guān)命令和參數(shù),然后再進行相應(yīng)的數(shù)據(jù)操作。ARM處理器與Nand Flash的連接主要有三種方式,如圖3所示:

運用GPIO管腳方式去控制Nand Flash的各個信號,在速度要求相對較低的時候,能夠較充分的發(fā)揮NAND設(shè)備的性能。它在滿足NAND設(shè)備時域需求方面將會有很大的便利,使得ARM處理器可以很容易的去控制NAND設(shè)備。該方式需要處理器提供充足的GPIO。

(2)運用邏輯運算方式進行連接

在該方式下,處理器的讀和寫使能信號通過與片選信號CS進行邏輯運算后去驅(qū)動NAND設(shè)備對應(yīng)的讀和寫信號。圖3中b例為SamSung公司ARM7TDMI系列處理器S3C44B0與Nand Flash K9F2808U0C的連接方式。

(3)直接芯片使能

有些ARM處理器如S3C2410內(nèi)部提供對NAND設(shè)備的相應(yīng)控制寄存器,通過控制寄存器可以實現(xiàn)ARM處理器對NAND設(shè)備相應(yīng)信號的驅(qū)動。該方式使得ARM處理器與NAND設(shè)備的連接變得簡單規(guī)范,圖3中c例給出了ARM處理器S3C2410與Nand Flash K9F2808U0C的連接方式。

3.3 ARM處理器與SDRAM接口技術(shù)

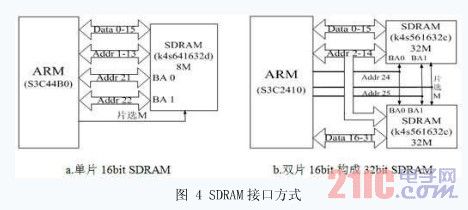

嵌入式最小系統(tǒng)的外部動態(tài)存儲器模塊一般采用SDRAM。現(xiàn)在的大多數(shù)ARM處理器內(nèi)部都集成有SDRAM控制器,通過它可以很容易的訪問SDRAM內(nèi)部的每一個字節(jié)。在實際開發(fā)中可以根據(jù)需要選用一片或多片SDRAM。圖4中給出了兩種常用的接口方式。

(1)單片SDRAM

圖4 中a例為 ARM處理器S3C44B0與一個16bit的SDRAM K4S641632d的連接方式。在對尺寸有嚴(yán)格限制且對動態(tài)存儲器容量要求不高的嵌入式系統(tǒng)中常采用此種連接方式。

(2)雙片16bit SDRAM結(jié)合使用

在雙片16bit SDRAM合成一個32bit SDRAM使用時,ARM處理器的地址線A2接SDRAM的地址線A0,其余地址依次遞增,這是因為在SDRAM中字節(jié)是存儲容量的惟一單位,而此時SDRAM為32bit位寬。

SDRAM的BA地址線是其內(nèi)部Bank的地址線,代表了SDRAM內(nèi)存的最高位。在圖4中b例的SDRAM總大小是64M(64M= ),需要A25-A0引腳來尋址,所以BA1-BA0連接到了A25-A24引腳上。還需注意的是SDRAM內(nèi)存行地址和列地址是復(fù)用的,所以地址線的數(shù)目一般少于26條,具體連接需要參考ARM處理器和SDRAM的相關(guān)手冊。

值得注意的是,有些ARM處理器如SamSung公司的ARM940T系列處理器S3C2510 ,其地址總線與其它標(biāo)準(zhǔn)ARM處理器不太一樣,它的地址線分為內(nèi)部地址線和外部地址線兩種類型。根據(jù)所連接的存儲器數(shù)據(jù)總線寬度,內(nèi)部地址線進行相應(yīng)的移位,對應(yīng)到外部地址線A23-A0,從而對外提供固定的地址線A23-A0。其實質(zhì)與典型的ARM處理器是一致的。

4. 嵌入式系統(tǒng)啟動架構(gòu)

啟動架構(gòu)是嵌入式系統(tǒng)的關(guān)鍵技術(shù)。掌握啟動架構(gòu)對于了解嵌入式系統(tǒng)的運行原理有著重要的意義。嵌入式系統(tǒng)在啟動時,引導(dǎo)代碼、操作系統(tǒng)的運行和應(yīng)用程序的加載主要有兩種架構(gòu),一種是直接從Nor Flash啟動的架構(gòu),另一種是直接從Nand Flash啟動的架構(gòu)。

需要注意的是,在嵌入式系統(tǒng)啟動引導(dǎo)的過程中會有多種情況出現(xiàn),如vxWorks的啟動代碼BootRom就有壓縮和非壓縮,駐留和非駐留方式之分,而操作系統(tǒng)本身也多以壓縮映象方式存儲,所以啟動代碼在執(zhí)行和加載過程中需要根據(jù)不同的情況,作出相應(yīng)的處理。

4.1從Nor Flash啟動

Nor Flash具有芯片內(nèi)執(zhí)行(XIP,eXecute In Place)的特點,在嵌入式系統(tǒng)中常做為存放啟動代碼的首選。從Nor Flash啟動的架構(gòu)又可細分為只使用Nor Flash的啟動架構(gòu)和Nor Flash與Nand Flash配合使用的啟動架構(gòu)。圖5 給出了這兩種啟動架構(gòu)的原理框圖。

4.1.1單獨使用Nor Flash

在該架構(gòu)中,引導(dǎo)代碼、操作系統(tǒng)和應(yīng)用代碼共存于同一塊Nor Flash中。系統(tǒng)上電后,引導(dǎo)代碼首先在Nor Flash中執(zhí)行,然后把操作系統(tǒng)和應(yīng)用代碼加載到速度更高的SDRAM中運行。另一種可行的架構(gòu)是,在Nor Flash中執(zhí)行引導(dǎo)代碼和操作系統(tǒng),而只將應(yīng)用代碼加載到SDRAM中執(zhí)行。

該架構(gòu)充分利用了Nor Flash芯片內(nèi)執(zhí)行的特點,可有效提升系統(tǒng)性能。不足在于隨著操作系統(tǒng)和應(yīng)用代碼容量的增加,需要更大容量昂貴的Nor Flash來支撐。

4.1.2 Nor Flash和Nand Flash配合使用

Nor Flash的單獨使用對于代碼量較大的應(yīng)用程序會增加產(chǎn)品的成本投入,一種的改進的方式是采用Nor Flash 和Nand Flash配合使用的架構(gòu)。在該架構(gòu)中附加了一塊Nand Flash,Nor Flash(2M或4M)中存放啟動代碼和操作系統(tǒng)(操作系統(tǒng)可以根據(jù)代碼量的大小選擇存放于Nor Flash或者Nand Flash),而Nand Flash中存放應(yīng)用代碼,根據(jù)存放的應(yīng)用代碼量的大小可以對Nand Flash容量做出相應(yīng)的改變。

系統(tǒng)上電后,引導(dǎo)代碼直接在Nor Flash中執(zhí)行,把Nand Flash中的操作系統(tǒng)和應(yīng)用代碼加載到速度更高的SDRAM中執(zhí)行。也可以在Nor Flash中執(zhí)行引導(dǎo)代碼和操作系統(tǒng),而只將Nand Flash中的應(yīng)用代碼加載到SDRAM中執(zhí)行。該架構(gòu)是當(dāng)前嵌入式系統(tǒng)中運用最廣泛的啟動架構(gòu)之一。

4.1.2從Nand Flash啟動

有些處理器如SamSung公司的ARM920T系列處理器S3C2410支持從Nand Flash啟動的模式,它的工作原理是將NandFlash中存儲的前4KB代碼裝入一個稱為Steppingstone(BootSRAM)的地址中,然后開始執(zhí)行該段引導(dǎo)代碼,從而完成對操作系統(tǒng)和應(yīng)用程序的加載。該方式需要處理器內(nèi)部有NAND控制器,同時還要提供一定大小額外的SRAM空間,有一定的使用局限性,在實際開發(fā)中較少使用。

5. 結(jié)束語

本文作者創(chuàng)新點:根據(jù)ARM體系結(jié)構(gòu)的相通性,以基于ARM的嵌入式最小系統(tǒng)為平臺,從硬件和軟件兩方面對其架構(gòu)進行了研究。硬件方面就ARM處理器與常用外部存儲器的接口方式進行了闡述,軟件方面給出了嵌入式最小系統(tǒng)典型的啟動架構(gòu)及其選擇標(biāo)準(zhǔn)。

參考文獻:

[1] 李別.基于S3C4510B的ARM開發(fā)平臺[J].微計算機信息,2006,10-2:34-36.

[2] 張崙.32位嵌入式系統(tǒng)硬件設(shè)計與調(diào)試[M].北京:機械工業(yè)出版社, 2005.60-61.

[3] NAND Flash Applications Design Guide[EB/OL]. http://www.toshiba.com.