現(xiàn)場可編程邏輯門陣列(Virtex)和高性能數(shù)字信號處理器(DSP)是高速信號處理領(lǐng)域兩大關(guān)鍵器件,Virtex和DSP的運算速度及并行處理效能成為制約高速信號處理應用的主要因素。FPGA以其設(shè)計靈活性及硬件高密度性在高速信號處理領(lǐng)域顯示出愈來愈重要的作用。Xilinx公司最新推出的Virtex系列FPGA。是一種采用5層0.22μmCMOS工藝的高性能、大容量現(xiàn)場可編程邏輯門陣列,其系統(tǒng)門密度高達100萬門,系統(tǒng)性能可達200MHz,可選擇配置為多種接口標準,內(nèi)部含有豐富的布線資源,其SelectRAM和BlockRAM可靈活地配置為SRAM、FIFO、DPRAM、CAM等多種形式的存儲單元。Virtex系列FPGA含有極其豐富的I/O資源,可靈活地與TMS320C40DSP接口,與DSP配合可完成復雜的信號處理功能。C40DSP含有兩組外部總線資源和6個高速通信口,可方便地進行多DSP擴展,以提高系統(tǒng)信號處理的性能。

在對Virtex系列FPGA進行充分理解和研究的基礎(chǔ)上,結(jié)合對XC4000系列FPGA和DSP背板開發(fā)設(shè)計經(jīng)驗,研制出了基于XCV200/300PQFP240和TMS320C40的可編程嵌入式高速信號處理背板。背板采用了針對系統(tǒng)需求自行開發(fā)的XPCI總線,背板可脫離實際應用系統(tǒng)進行獨立的面向應用的設(shè)計和調(diào)試,也可按照XPCI總線標準方便地嵌入到實際應用系統(tǒng)中,成為系統(tǒng)的一部分進行聯(lián)合調(diào)試。

對可編程嵌入式信號處理背板進行全面綜合測試的結(jié)果表明,背板性能達到了預期設(shè)計要求,工作狀態(tài)穩(wěn)定。我們還針對實際應用開發(fā)了一些FPGA模塊和DSP程序。

1Virtex系列FPGA性能簡介

在前幾代FPGA開發(fā)的基礎(chǔ)上,Virtex系列FPGA結(jié)合了多種可編程系統(tǒng)的特征,采用了快速靈活的層次性互連布線資源和先進的處理技術(shù),提供了高速度、大容量的邏輯解決方案,進一步縮短了數(shù)字信號處理系統(tǒng)的開發(fā)周期。與前幾代FPGA相比,Virtex系列FPGA的特性主要體現(xiàn)在以下幾個方面:

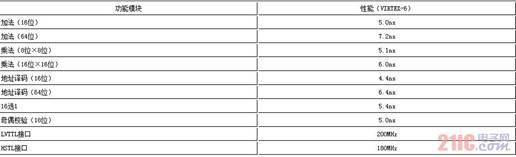

(1)更高的處理速度和更高的邏輯門密度。Virtex系列最大系統(tǒng)門數(shù)高達100萬門,系統(tǒng)性能可達200MHz,其中比較常用的幾個功能模塊性能如表1所示。

表1Virtex系列FPGA幾個常用功能模塊的性能

(2)更多可兼容的I/O接口標準。Virtex系列可兼容16種高性能接口標準,可直接與ZBTRAM器件接口,且其獨特的I/O分組方式可使多種不同電壓標準接口在同一片FPGA上實現(xiàn)。

(3)片內(nèi)時鐘管理電路。Virtex系列內(nèi)部包含4個靈活的延時鎖相環(huán)用于高級時鐘管理,可實現(xiàn)倍頻、分頻、鎖相等功能,此外還有4個主全局時鐘網(wǎng)絡(luò)和24個從本地時鐘網(wǎng)絡(luò),以實現(xiàn)高速時鐘的傳輸。

(4)層次性存儲管理系統(tǒng)。Virtex系列內(nèi)部查找單元可配置為16bit和32bitRAM、16bitDPRAM或16bit移位寄存器,其BlockRAM資源可配置為4kbitDPRAM或FIFO、CAM等存儲器件,且提供了高速外部RAM接口。

(5)更加靈活的系統(tǒng)結(jié)構(gòu)。復雜的進位邏輯鏈提高了算術(shù)邏輯性能,復雜的乘法器支持,級聯(lián)鏈支持寬位輸入模塊,豐富的帶時鐘使能的寄存器和鎖存器,支持異步和同步復位及置位,支持IEEE1149.1邊界掃描邏輯。

(6)基于SRAM的在系統(tǒng)可重構(gòu)技術(shù)。可無限次重復編程,包含主串、從串、SelectRAM和JTAG四種配置模式,支持部分重構(gòu)。

2基于Virtex系列FPGA的可編程嵌入式信號處理背板的設(shè)計

由于對Virtex系列FPGA進行了充分理解和熟悉,我們研制了基于自行開發(fā)的XPCI總線的可編程嵌入式信號處理背板。由于Virtex系列FPGA內(nèi)部結(jié)構(gòu)相同,外部引腳兼容,只是在系統(tǒng)門數(shù)上有所區(qū)別,我們采用了XCV200PQ240-4作為可編程嵌入式信號處理背板的主處理芯片,與FPGA接口的DSP采用功能強大、接口靈活的TMS320C40DSP。背板中DSP的應用目的是對FPGA進行管理和控制、對FPGA處理結(jié)果進行分析、通過DSP軟件實現(xiàn)其他相關(guān)功能,以提高系統(tǒng)設(shè)計的靈活性。C40DSP具有兩組外部總線資源和6個高速通信口,能方便靈活地實現(xiàn)系統(tǒng)擴展。背板中FPGA可根據(jù)設(shè)計需要選擇不同規(guī)模的芯片。

可編程嵌入式信號處理背板結(jié)構(gòu)如圖1所示。

背板上主要包含1片XCV200PQ240FPGA、1片TMS320C40DSP、1片XC9536CPLD、1片EDI8L512SRAM(512K×32bit)、1片AT49020Flash2Mbit、DSP調(diào)試JTAG接口、FPGA調(diào)試X_Checker接口、CPLD調(diào)試JTAG接口、自行開發(fā)XPCI接口及5個獨立DSP通信口。背板所有器件除DSP外均采用貼片封裝、雙面裝焊,使得背板的尺寸較小(76mm×127mm×12mm),DSP外圍512K×32bitSRAM使得背板系統(tǒng)能夠滿足大部分應用程序的要求。2MbitFlash用于固化FPGA配置和DSP應用程序代碼。背板系統(tǒng)既可以獨立工作(Standalone方式),也可以通過XPCI總線嵌入系統(tǒng)工作(Plug_in方式)。

背板系統(tǒng)以40MHz晶振輸出作為時鐘,C40DSP工作在40MHz時鐘下,XCV200FPGA以40MHz時鐘作為輸入,在內(nèi)部通過DDL電路可將內(nèi)部工作時鐘倍頻到180MHz。DSP通過本地總線(LA0..30、LD0..31)以TTL兼容方式與FPGA接口,占用FPGA65bitI/O資源;DSP通過本地總線對FPGA進行配置、參數(shù)設(shè)置及數(shù)據(jù)交換,實現(xiàn)軟硬件之間的協(xié)同處理。

Virtex系列FPGA內(nèi)部供電電壓為2.5V,I/O通過VCCO和VREF控制實現(xiàn)與各種電平接口之間的兼容;與TTL兼容的VCCO控制電壓為3.3V,VREF作為一般I/O使用;Virtex的I/O分組方式實現(xiàn)使得不同電平接口得以在同一芯片設(shè)計中共存。

背板通過168線XPCI總線與外部系統(tǒng)接口,XPCI總線主要包含三大部分:電源接口、FPGA的可編程I/O口、DSP接口。電源接口包括給DSP、CLPD、SRAM及其他TTL邏輯供電的5V電源,給XCV200PQ240等Virtex系列FPGA內(nèi)部工作邏輯供電的2.5V電源,I/O接口供電電平VCCO和分組參考電平VREF(Bank0~Bank7FPGA可編程I/O接口主要提供了64個從Virtex系列FPGA引出的可編程I/O引腳,用于設(shè)計特定邏輯;DSP接口提供了TMS320C40DSP主總線接口、中斷口和通信端口0及TCLK0和TCLK1,用于系統(tǒng)擴展及與用戶程序之間的數(shù)據(jù)交換。

背板有豐富的配置及調(diào)試接口。Virtex系列FPGA在板上可實現(xiàn)三種配置方式:從串方式(通過Xlinx專用X_Checker接口)、JTAG方式(通過XPCI接口提供給用戶)、Select_RAM方式(通過DSP和XC9536CPLD實現(xiàn));DSP調(diào)試通過專用14芯JTAG接口完成;CPLD邏輯可通過標準JTAG電纜實時修改配置。DSP其他5個通信口通過5個IDC14插座輸出,可根據(jù)系統(tǒng)實際需要選用。

3基于Virtex系列FPGA的可編程嵌入式信號處理背板的調(diào)試

在信號處理背板制作完成之后,我們對背板進行了調(diào)試,并開發(fā)了一些背板專用配置程序。

在調(diào)試過程中我們使用了WhiteMount公司的CodeComposerDSP開發(fā)調(diào)試軟件和Xilinx公司的Foundation2.1IFPGA&CPLD開發(fā)調(diào)試軟件。為全面驗證我們預期的設(shè)計效果,調(diào)試按以下過程進行:

(1)利用Foundation2.1I通過X_Checker接口向FPGA下載測試配置,FPGA響應結(jié)果正確。

(2)利用CodeComposer通過JTAG電纜對DSP內(nèi)部RAM和外部SRAM進行測試,測試表明硬件設(shè)計正確。

(3)利用Foundation2.1I通過標準JTAG電纜對XC9536下載測試配置,CPLD響應結(jié)果正確。

(4)利用Foundation2.1I通過標準JTAG電纜對XC9536下載自行設(shè)計的FPGA專用配置,利用CodeComposer通過JTAG電纜對DSP加載專用配置程序,使得DSP完成對Flash燒錄FPGA配置數(shù)據(jù)和DSP的Bootloader數(shù)據(jù)。

(5)脫離開發(fā)系統(tǒng),背板上電通過Flash內(nèi)的配置數(shù)據(jù)自行FPGA配置和DSP的Bootloader運行結(jié)果正確。

4應用設(shè)計實例

為進一步驗證背板的通用性,我們根據(jù)實際課題需求,在背板上開發(fā)了兩個應用設(shè)計實例。一個是320MHz32bit高速計數(shù)器。我們在以前開發(fā)的200MHz高速計數(shù)器的基礎(chǔ)上,基于多路均勻相差時鐘信號在TOA時刻進行邏輯譯碼獲得高速計數(shù)效果的原理,通過外部40MHz輸入時鐘,利用VirtexFPGA內(nèi)部DDL電路產(chǎn)生4路相差90°的80MHz信號,形成320MHz32bit高速計數(shù)器,使得時間測量精度達到3ns左右。該設(shè)計可用于高精度TOA、PW、RF等參數(shù)的測量。

另一個是基于內(nèi)容可尋址存儲器(CAM)的關(guān)聯(lián)比較器。我們在充分分析Xlinx提供的CAM_Core設(shè)計的基礎(chǔ)上,自行設(shè)計了一種基于CAM的可編程關(guān)聯(lián)比較器。該比較器采用中值比較法,可通過控制線控制比較范圍,并設(shè)計了一種專門對付捷變參數(shù)的多值比較邏輯。我們利用XCV200PQ240實現(xiàn)了上述設(shè)計,通過測試母板上的UART從控制臺微機上接收模擬輻射源數(shù)據(jù)。測試結(jié)果表明,在輻射源參數(shù)空間重疊不太嚴重的情況下,該設(shè)計可同時處理80個以上的裝定輻射源參數(shù)(128bitPDW可包含捷變參數(shù)),且能達到較好的分選效果,可見它在偵察信號處理領(lǐng)域的應用前景是非常廣闊的。