作為第3代顯示器,,被譽為夢幻顯示器的,有機電致發(fā)光器件( OrganicLight Emitting Diode,,OLED) 由于其主動發(fā)光,、響應快、高亮度,、全視角,、直流低壓驅(qū)動、全固態(tài)以及不易受環(huán)境影響等優(yōu)異特性,,具有LCD 無法比擬的優(yōu)點,,在手機、個人電子助理( PDA) 、數(shù)碼相機,、車載顯示,、筆記本電腦、壁掛電視以及軍事領(lǐng)域都具有廣闊的應用前景,,因而得到了業(yè)界廣泛的關(guān)注。OLED 發(fā)展至今,,已經(jīng)由最初的單色發(fā)展到現(xiàn)在的全彩,,與此同時對驅(qū)動電路也提出了更高的要求,由最初的無灰階單色靜態(tài)驅(qū)動,,到彩色動態(tài)驅(qū)動,。

目前,OLED 的研究重點是研制高穩(wěn)定性的器件以達到實用化的要求,,但同時研究實現(xiàn)高質(zhì)量動態(tài)顯示的驅(qū)動技術(shù)也很重要,,因為只有結(jié)合良好的驅(qū)動技術(shù),提高反應速度和分辨 率,,才能表現(xiàn)出OLED 的優(yōu)異特點,。然而,單色OLED 顯示就要求驅(qū)動電壓具有較高的控制精度,,彩色OLED 顯示如要同時精確地控制RGB 三基色的灰度,,實現(xiàn)起來難度更大。為實現(xiàn)真彩色,,R,、G、B 三基色要各自實現(xiàn)256 級灰階,。文中所述電路屬于全彩色動態(tài)驅(qū)動電路,,將對其256 級灰度顯示以及外圍驅(qū)動進行研究與設(shè)計,為今后大尺寸OLED 顯示器提供一個可行的技術(shù)方案,。

1 驅(qū)動控制系統(tǒng)設(shè)計

顯示器性能的好壞,,一方面取決于顯示器的制作材料,另一方面取決于顯示器的驅(qū)動電路系統(tǒng),。驅(qū)動電路系統(tǒng)是保證顯示器正常工作必不可少的部分,,對顯示性能 起著舉足輕重的作用,驅(qū)動電路系統(tǒng)的不同會導致顯示器顯示色彩,、亮度以及顯示的灰度,、響應時間、功耗等顯示器參數(shù),。而OLED 顯示屏需要專用的控制驅(qū)動芯片,,只有OLED 屏與驅(qū)動控制芯片的成功結(jié)合,才能推動OLED 的發(fā)展從而取代LCD.然而,,目前國內(nèi)外對OLED 研究的熱點主要在器件與材料上,,關(guān)于驅(qū)動電路和灰度控制方面的研究相對較少,,現(xiàn)有的OLED 驅(qū)動電路集成度低,針對OLED 特性的掃描效率優(yōu)化度也不高,。因此,,設(shè)計高性能的OLED 驅(qū)動電路,成為顯示領(lǐng)域一個亟待解決的問題,。文中在現(xiàn)有的研究基礎(chǔ)上,,自行設(shè)計了分辨率為480 × 640 彩色OLED 屏外圍驅(qū)動電路,并對256 級灰度實現(xiàn)方法進行了優(yōu)化,,使其與OLED 完美結(jié)合,,從而進一步推動OLED 向前發(fā)展。

1. 1 OLED 像素單元電路

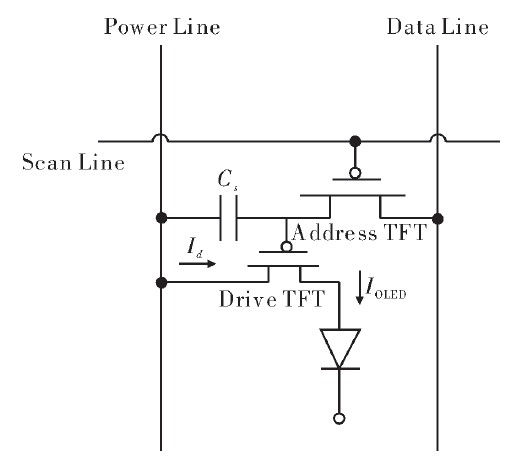

對于OLED 驅(qū)動控制系統(tǒng)的實現(xiàn),,關(guān)鍵技術(shù)在于數(shù)據(jù)的寫入和掃描控制,,圖1 是單個像素的雙管驅(qū)動電路。一個TFT 用來尋址,,另一個是電流調(diào)制晶體管,,用來為OLED 提供電流。為防止OLED 開啟電壓的變化導致電流變化,,使用的是P 溝器件,,這樣,OLED處于驅(qū)動TFT 的漏端,,源電壓與有機層上的電壓無關(guān),。

圖1 OLED 雙管驅(qū)動電路

Data Line 與尋址TFT 的源級相連,Scan Line 使地址TFT 選通,,數(shù)據(jù)線上的內(nèi)容通過漏電流寫入到存儲電容CS上,,并以電荷的形式暫存。

當Power Line 為高電平時,,驅(qū)動TFT 的源級為高電平,,同時CS上的電荷,將選通驅(qū)動TFT,,其漏電流流過OLED 顯示器件,,驅(qū)動其發(fā)光。數(shù)據(jù)線電平的高低決定了像素的亮暗,。

1. 2 256 級灰度顯示

所謂圖像的灰度等級就是指圖像亮度深淺的層次,,將基色的發(fā)光亮度按強度大小劃分,就是灰度級,。

顯示屏能產(chǎn)生的灰度級越高,,顯示的顏色和圖像層次就越多。而且人的視覺系統(tǒng)對亮度強弱的感受不僅與亮度本身的強弱相關(guān),還與發(fā)光時間和點亮面積有關(guān),,在 一定時間范圍內(nèi),,點亮時問越長、面積越大,,人眼感覺的發(fā)光強度就越強,。因而利用人眼對快速的亮暗閃爍并不敏感的“暫留”效應,變換發(fā)光體的點亮時間和面積 來區(qū)分亮度,,就會形成一種不同灰度級畫面的視覺,,一般灰度級越高,所顯示的顏色和圖像層次就越多,,圖像越柔和,圖像層次越逼真,。高灰度級以及有效的灰度調(diào) 制方式對高清晰度顯示的發(fā)展極其重要,,目前OLED 顯示驅(qū)動一個亟需解決的是灰度的精確性問題。

OLED 顯示屏是可以用傳統(tǒng)的模擬電壓控制法來實現(xiàn)灰度,,問題在于: 亮度和數(shù)據(jù)電壓之間呈非線性關(guān)系,,缺少一個漸變的易于控制的線性區(qū)間,因此,,采用模擬電壓法調(diào)節(jié)發(fā)光強度,,難以精確、有效地實現(xiàn)OLED 的灰度級顯示,,現(xiàn)在總的趨勢是使用數(shù)字驅(qū)動電路,。

FPGA" p="" src="http://files.chinaaet.com/images/2012/07/03/670bed80-b694-4559-b315-452895971f21.jpg" title="FPGA" width="400" />

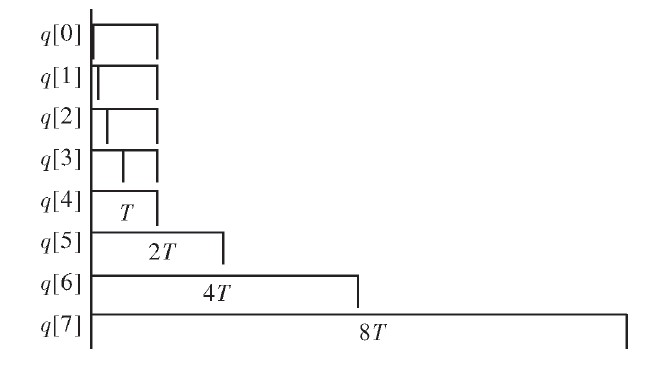

圖2 分時顯示示意圖

數(shù)字驅(qū)動電路的困難在于工作頻率比模擬驅(qū)動電路高得多,現(xiàn)階段較為實用的灰度調(diào)制方法主要有兩種,。一種是脈寬調(diào)制法,,即對驅(qū)動脈沖實現(xiàn)占空比的控制; 另一種方法是子場控制法,,這種方法將發(fā)光時間按1∶ 2∶ 4∶ 8∶ …劃分為若干個子場,,不同的子場導通組合,就能實現(xiàn)不同的灰度等級,。但采用脈寬調(diào)制法,,其時序復雜,要求顯示屏有較高響應速度,; 而采用子場法要求驅(qū)動頻率較高,,對高灰度級的實現(xiàn)難度大。

考慮到幀頻與OLED 屏體顯示效率的折中,,使驅(qū)動電路工作頻率在一個合理水平,,在脈寬調(diào)制和子場原理的基礎(chǔ)上,對這兩種方法進行優(yōu)化,256 級灰度采用通過對圖像數(shù)據(jù)按位分時顯示的方法實現(xiàn),,即對輸入的8 bit 像素信號RGB,,通過給每種顏色字節(jié)的不同位分配不同的顯示時間達到灰度顯示的目的,使每位的顯示時間為128∶ 64∶ 32∶ 16∶ 8∶ 4∶ 2∶ 1,,利用其組合可以得到256 級灰度顯示所對應的子像素發(fā)光時間,,實現(xiàn)視覺上的256 級灰度即1 667 萬色顯示,以實現(xiàn)高質(zhì)量的顯示畫面,。

為實現(xiàn)256 級灰度,,將一個像素點的掃描時間分成19 個單位時間t,8 bit 灰度數(shù)據(jù)q[7: 0]從高位到低位所占的時間分別為8t,,4t,,2 t,t,,t,,t,t,,t.為使不同位顯示時間成一定比例,,從q[3]開始引入t /2 的消影時間,q[2]引入t /4 的消影時間,,d[1]引入t /8 的消影時間,,d[0]引入t /16 的消影時間,如圖2 所示,,由控制電路產(chǎn)生消隱信號進行消隱,。由此計算OLED 屏亮度百分比λ = ( 8 + 4 + 2 + l + 1 /2 + 1 /4 + 1 /8 + 1 /16 ) /19 = 83. 9%.

1. 3 FPGA 控制器

利用FPGA 的處理速度和數(shù)據(jù)寬度高的優(yōu)勢以及芯片中可利用的豐富資源,為分辨率為480 × RGB ×640 的OLED 顯示屏設(shè)計了外圍驅(qū)動控制電路,。其主要作用是向OLED 顯示屏提供掃描控制信號及進行OLED 顯示數(shù)據(jù)的數(shù)字信號處理,。

根據(jù)OLED 顯示屏周邊接口的結(jié)構(gòu)和特性,利用FPGA 芯片為其設(shè)計外圍的驅(qū)動控制系統(tǒng),,為OLED 屏提供控制信號以及傳輸所要顯示的數(shù)據(jù)信號,。

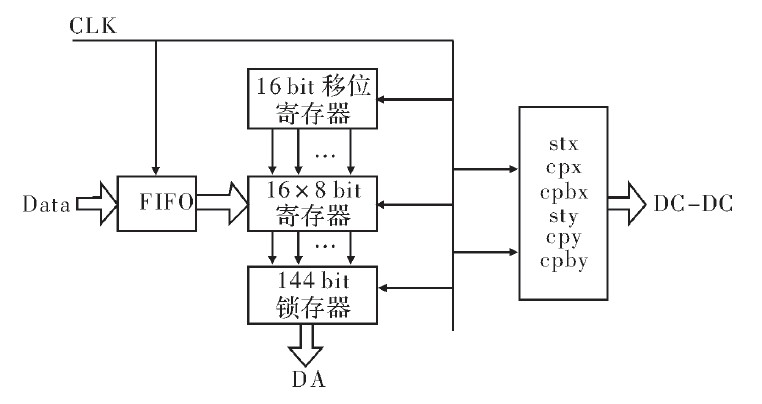

如圖3 所示,經(jīng)解碼后的圖像數(shù)據(jù)存入FIFO( First In First Out) 緩存中,,在主時鐘的控制下,,F(xiàn)IFO中的圖像數(shù)據(jù)將被載入到一個16 × 8 的數(shù)據(jù)裝載寄存器,當這16 個8 位數(shù)據(jù)裝載寄存器裝滿時,,將被一個144 位的鎖存器鎖存,,等待進入D/A 轉(zhuǎn)換模塊; 同時FPGA 控制器還將在主時鐘的控制下產(chǎn)生行列移位時鐘和行列掃描起始脈沖,,產(chǎn)生的時鐘和脈沖進入DC -DC 轉(zhuǎn)換模塊,。

圖3 FPGA 控制器結(jié)構(gòu)框圖,。

1. 4 各種控制信號周期及頻率

為使FPGA 控制器能工作于一個合理的驅(qū)動頻率以及提高顯示屏的亮度,在結(jié)構(gòu)上采用標準單元塊的形式,。對于分辨率480 × 3 × 640 的顯示屏,,以8 × 16個顯示像素燈管構(gòu)成一個單元塊,將480 × 3 行分組組合成為90 個塊( Block) ,,即每塊由一組列信號同時驅(qū)動16 行像素,。設(shè)計列掃描驅(qū)動電路時,將640 列電極分組組合成為80 個塊( Block) ,,每個塊并行驅(qū)動8 列像素,。

OLED 顯示屏的刷新頻率是60 Hz /s,即顯示一幀圖像的時間為1 /60 s,,設(shè)為T,,所以,行掃描起始信號stx 的周期T 為16 667 μs,,占空比為1∶ 90; 因為OLED顯示屏480 × 3 行電極分組組合成為90 個Block,,所以每一塊的選通時間為T /90,即185. 185 μs.而cpx 和cpbx 是一對反相不交疊的脈沖信號,,占空比為50%,在脈沖信號的高電平和低電平時,,都有一個Block 行像素被選通,,即在cpx 和cpbx 一個周期內(nèi)有兩個Block 行像素被選通,所以行掃描驅(qū)動脈沖cpx 和cpbx的周期為T /45,,即370. 370 μs.

同 理,,OLED 顯示屏的列被分為80 個Block,每個列Block 的選通時間為2. 315 μs,,列掃描起始信號sty的周期為185. 185 μs,,占空比為1 ∶ 80.列驅(qū)動脈沖cpy 和cpby 亦是一對反相不交疊的脈沖信號,占空比為50%,,在脈沖信號的高電平和低電平時,,都有一個Block 被選通。由于每個列Block 的選通時間為2. 315 μs,,所以列掃描驅(qū)動脈沖cpy 和cpby 的周期為4. 630 μs.

在每個列Block 選通期間,,從FIFO 中并行讀出的8 個8 bit 數(shù)據(jù)進入數(shù)據(jù)鎖存器鎖存。在每個BLOCK選通期間都將進行一次數(shù)據(jù)的鎖存,,所以數(shù)據(jù)鎖存信號Lock 的周期為2. 315 μs.因為當16 個8 位的數(shù)據(jù)裝載寄存器都載滿數(shù)據(jù)的時候才進行這144 個數(shù)據(jù)的鎖存,,所以16 位移位寄存器時鐘clk _reg 的周期為0. 145 μs.從FIFO 中讀出數(shù)據(jù)的速度必須和向數(shù)據(jù)裝載寄存器中裝載數(shù)據(jù)的速度一致,則FIFO 的讀時鐘clk _ fifo 的周期也為0. 145 μs.對0. 15 μs( 6. 896 MHz) 進行近似為7 MHz,,所以令系統(tǒng)的基本時鐘為14 MHz,,由FPGA 外部晶振產(chǎn)生,。讀時鐘為基本時鐘的二分頻。

1. 5 FPGA 工作流程

FPGA 處理器是設(shè)計的核心部分,,其工作流程為,,在每個clk_fifo 時鐘周期下,從8 個FIFO 緩存中并行讀出8 個8 bit 像素數(shù)據(jù),,在時鐘clk_reg 上升沿到來時,, 16 位移位寄存器發(fā)生移位,它的輸出端接16 個8位數(shù)據(jù)裝載寄存器的片選端,,這樣16 個8 位數(shù)據(jù)裝載寄存器逐個被選通,,此時這些數(shù)據(jù)就可以載入到16 個8 位數(shù)據(jù)裝載寄存器中,這16 個8 位寄存器的輸出端接在144 位鎖存器的輸入端上,。16 個時鐘clk_reg 上升沿過后,, 16 個8 位數(shù)據(jù)裝載寄存器都將依次被裝載滿,此時數(shù)據(jù)鎖存信號Lock 到達,,將144 個數(shù)據(jù)鎖存到144 位數(shù)據(jù)鎖存器中,,然后這些數(shù)據(jù)進入到DA 轉(zhuǎn)換模塊,轉(zhuǎn)換成16 路模擬量,,送至OLED 顯示屏,,完成一個Block 數(shù)據(jù)的載入。

在列掃描驅(qū)動脈沖cpy 和cpby 的控制下,,80 個Block 依次被選通,,在每一Block 被選通期間,都將進行一次144 個數(shù)據(jù)的移位寄存和鎖存,,當80 個Block都鎖存完之后,,一行數(shù)據(jù)的載入也就完成了。當?shù)谝恍械?0 個Block 數(shù)據(jù)顯示完畢后,,列掃描起始信號sty過來,,又開始從第一列掃描,與此同時,,在行掃描驅(qū)動脈沖cpx 和cpbx 的作用下,,第二行像素被選通,所以,,這時將進行第二行的1 到80 個Block 的數(shù)據(jù)載入,,以此類推,直到90 行數(shù)據(jù)都顯示完畢之后,,行掃描起始信號stx 到來,,重新選通第一行,循環(huán)往復,,一幀幀地顯示數(shù)據(jù),。

2 仿真結(jié)果

選用Altera 公司Cyclone Ⅲ 系列芯片EP3C10E144C8 為目標芯片,,采用Verilog HDL 語言進行設(shè)計,在GX - SOPC - EDA - EP3C10 - STARTER -EDK 開發(fā)板上進行Modelsim 仿真,,仿真結(jié)果如圖4 和圖5 所示,。

圖4 外圍驅(qū)動時序仿真結(jié)果

圖5 256灰度產(chǎn)生模擬仿真

由圖4 仿真結(jié)果可以看出,80 組列掃描脈沖cpy和cpby 控制80 個Block,, 80 個列掃描脈沖完畢后,,列掃描起始信號sty 脈沖開始,繼續(xù)掃描下一行,。90 行掃描完畢后,, stx 到來重新選通第一行,依此循環(huán),,符合設(shè)計的要求,。

由圖5 仿真結(jié)果可以看出,對于輸入的8 bit 像素數(shù)據(jù),,經(jīng)灰度產(chǎn)生模塊轉(zhuǎn)化為灰度數(shù)據(jù),。以第一個輸入數(shù)據(jù)8 hff 為例,每位的顯示時間為128∶ 64∶ 32∶ 16∶ 8∶ 4∶2∶ 1,,由其不同組合,,從而實現(xiàn)了256 級灰度的功能。

3 結(jié)束語

基于FPGA 芯片設(shè)計了分辨率為480 × RGB × 640的真彩色OLED 顯示屏的驅(qū)動電路,,在傳統(tǒng)的子場原理和脈寬調(diào)制占空比實現(xiàn)灰度的基礎(chǔ)上,,對其進行優(yōu)化,采用R,、G、B 單基色像素分時顯示的方法,,實現(xiàn)了256 級灰度功能,。經(jīng)仿真和軟硬件協(xié)同仿真驗證,實現(xiàn)了設(shè)計所要求滿足的功能,。其256 級灰度實現(xiàn)方法簡單靈活,,降低了對FPGA 驅(qū)動頻率的要求,對于在高刷率,、高分辨率,、高灰階顯示器件上的應用,具有很高的實用價值,。利用該電路系統(tǒng)可以實現(xiàn)OLED 顯示的全彩色實時動態(tài)圖像的傳輸,,為今后OLED 作為大尺寸顯示器提供了技術(shù)支持。